宽带电台中的CMOS自动增益控制设计

赵思棋,李 斌

(中国电子科技集团公司第五十四研究所,河北 石家庄050081)

宽带电台中的CMOS自动增益控制设计

赵思棋,李斌

(中国电子科技集团公司第五十四研究所,河北 石家庄050081)

摘要自动增益控制(AGC)环路能够实现对输出信号幅度的精确控制,是射频接收器中不可或缺的一部分。提出了一种用于射频宽带电台中的自动增益控制环路。针对自动增益控制环路,从可编程增益放大器(PGA)、可变增益放大器(VGA)和峰值比较器3个角度论述了电路结构和设计方法。对AGC的功能实现和性能指标进行了仿真分析。仿真结果表明,该自动增益放大器在0.13 μm互补型金属氧化物半导体(CMOS)工艺下,具有80 dB动态范围,增益步进为1 dB。

关键词RFIC;自动增益控制环路;动态范围;0.13 μm CMOS

Design on CMOS Automatic Gain Control Loop in Broadband Radio

ZHAO Si-qi,LI Bin

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractThe automatic gain control (AGC) loop can implement the accurate control for output signal amplitude,so it is indispensable to radio frequency receiver.This paper puts forward an AGC loop used in radio frequency broadband radio.The circuit structure and design method are introduced from such three aspects as programmable gain amplifier (PGA),variable gain amplifier (VGA) and peak comparator.The function and performance of AGC are simulated and analyzed.The simulation results show that the automatic gain amplifier has dynamic gain of 80 dB and gain step of 1 dB based on the 0.13 μm complementary oxide semiconductor (COMS) process.

Key wordsRFIC;automatic gain control (AGC) circuit;dynamic range;0.13 μm CMOS

0引言

在无线接收机、助听器和数字电视调谐器等电子设备中,自动增益控制都是不可或缺的模块。对于不同功率的输入信号,自动增益控制可以通过调节增益,使设备的输出幅度保持在一个相对合适的范围[1-5]。

对于宽带电台来说,由于信道距离的不同使得信号具有强弱之分,需要接收机有足够大的动态范围来处理不同强度的信号。这是在宽带电台射频接收机中设计自动增益控制环路的意义所在。对于军用宽带电台射频接收机,由于使用环境的复杂性,天线可能引入各种未知的强干扰信号。在通过整个通道后,干扰信号可能依然存在,并淹没了有用信号,或使信号失真,因此,在特殊用途的宽带电台中,提高它的射频接收机中频通道的线性度非常重要。自动增益控制环路恰恰是中频通道的关键电路。

目前,大多数设计都集中在0.18 μm CMOS工艺下,随着工艺尺寸从0.18 μm减小到0.13 μm,供电电压将从3.3 V减小到1.2 V,尽管整个电路的功耗和速度得到了极大的优化,但是MOS器件的阈值电压仅仅下降100 mV,这一情况将恶化整个电路的增益和线性度,提高了电路设计的难度。

因此,对于应用在不同环境的射频接收机,它需要的AGC的性能指标不同,需要针对电路特定的工作环境,设计出适合接收机正常工作的自动增益控制环路。

此AGC采用数模混合电路设计架构。为满足输入动态范围的需求,电路包含增益粗调和增益细调2个模块,且增益细调模块采用可变反馈网络架构,以此来提高整体电路的线性度。并且,将工艺尺寸从0.18 μm下降到0.13 μm。

1AGC整体架构

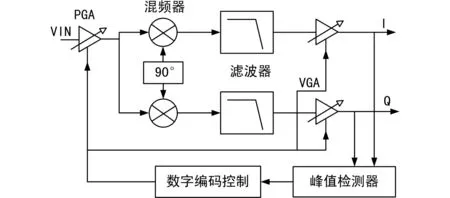

针对AGC的80 dB大动态范围,分别由一个粗调12 dB步进的PGA实现48 dB的动态范围和一个细调1 dB步进的VGA实现36 dB的动态范围。粗调步进使得输入动态范围在VGA的可调范围之内。如图1所示,中频信号经过可编程增益放大器(PGA)之后,再通过混频器下变频到零中频送入低通滤波器,滤除带外强干扰并放大前级信号后,进入可变增益放大器,调节增益并输出信号。最后,通过在峰值比较器中的信号对比,输出控制信号到数字电路,调节VGA和PGA的增益大小。

图1 AGC整体架构

2主要电路设计

2.1增益粗调控制

通过信号B0~B3控制开关来实现PGA电路的增益粗调,达到0dB、12dB、36dB和48 dB的4档可编程增益变化。其中,信号B0~B3是由电路反馈给数字电路产生的控制信号。该电路采用3级级联的方式实现48 dB的增益。前2级是步进为12 dB,总增益为24 dB的可变增益放大器,最后一级为输出buffer,增益固定为0 dB。

粗调增益主要由电路前2级实现,其实现的过程和电路结构如图2所示。

图2 PGA中粗调运算放大器

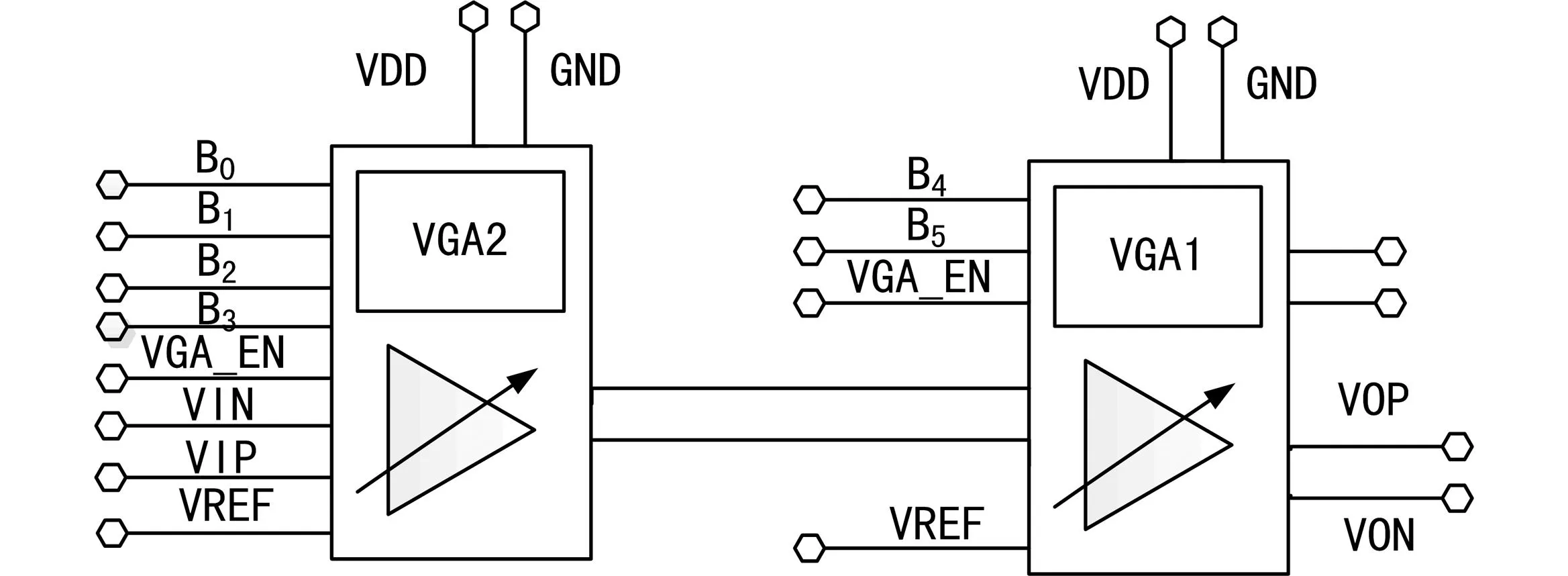

电路由4个基本差分对组成,分别是由M5、M6和M13三管构成的差分对1,由M7、M8和M14构成的差分对2,由M9、M10和M15构成的差分对3以及由M11、M12和M16构成的差分对4。由于基本差分对的小信号增益为[6]:

因此,该电路通过改变信号G1,G2来控制开关M1~M4的状态,以此从4个差分对中选择2个进行级联,达到改变电路增益的目的。例如,当G1为1、G2为0时,开关M1和M4导通,M2和M3闭合,前级跨导为gm5,6,后级跨导为gm11,12。此时该电路的总增益为:

gm5,6RD×gm11,12RD。

2.2细调增益控制

在AGC环路中,可变增益放大器(VGA)是一个核心模块,它的增益受到外部控制信号的控制。可变增益放大器的增益和控制电压的函数关系应该使自动增益控制环路的环路增益在控制信号的整个工作范围保持常数。这个特性使增益控制环路保持一个均匀的环路瞬态响应和恒定的环路稳定时间,而不受输入信号变化的影响。这就要求变增益放大器的增益应随控制信号以dB为单位线性变化,以此来保证自动增益控制环路的稳定时间保持常数。实现增益控制的方法有以下几种[7-10]:① 通过改变输入管的“源级负反馈”电阻Re的阻值来调节放大器跨导的可变跨导VGA;② 实用可变电阻阵列作为放大器负载的可变负载VGA;③ 采用固定增益放大器和可变衰减网络的来改变损耗的可变衰减网络VGA;④ 通过改变放大器的反馈系数来起到调节增益目的的可变反馈网络VGA。

本文采用可变反馈网络 VGA架构设计思路,并在此基础上进行了优化。这种VGA是一个基于全差分运算放大器的闭环反馈电路。不难得出,该放大器的增益为:

G=Rf/Rin。

由于其增益是反馈电阻Rf和输入电阻Rin的比值,因此通过改变Rf或者Rin的电阻值就可以实现增益可变的目的。由于Rf的改变影响到电路输入、输出节点的极点,其变化会对电路的频率特性造成影响,使带宽不稳定。因此通常都是改变输入电阻Rin的值。但Rin的变化会改变前级电路的负载特性,对于一些敏感的电路,需在放大器和前级电路之间加上缓冲器来隔离。

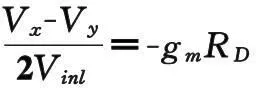

为实现36 dB增益变化,采用2级放大模式,如图3所示。整体电路可实现粗调12 dB,细调1 dB步进。电路中B1~B5为控制信号,改变电路增益。

图3 VGA整体架构

2.3峰值比较器

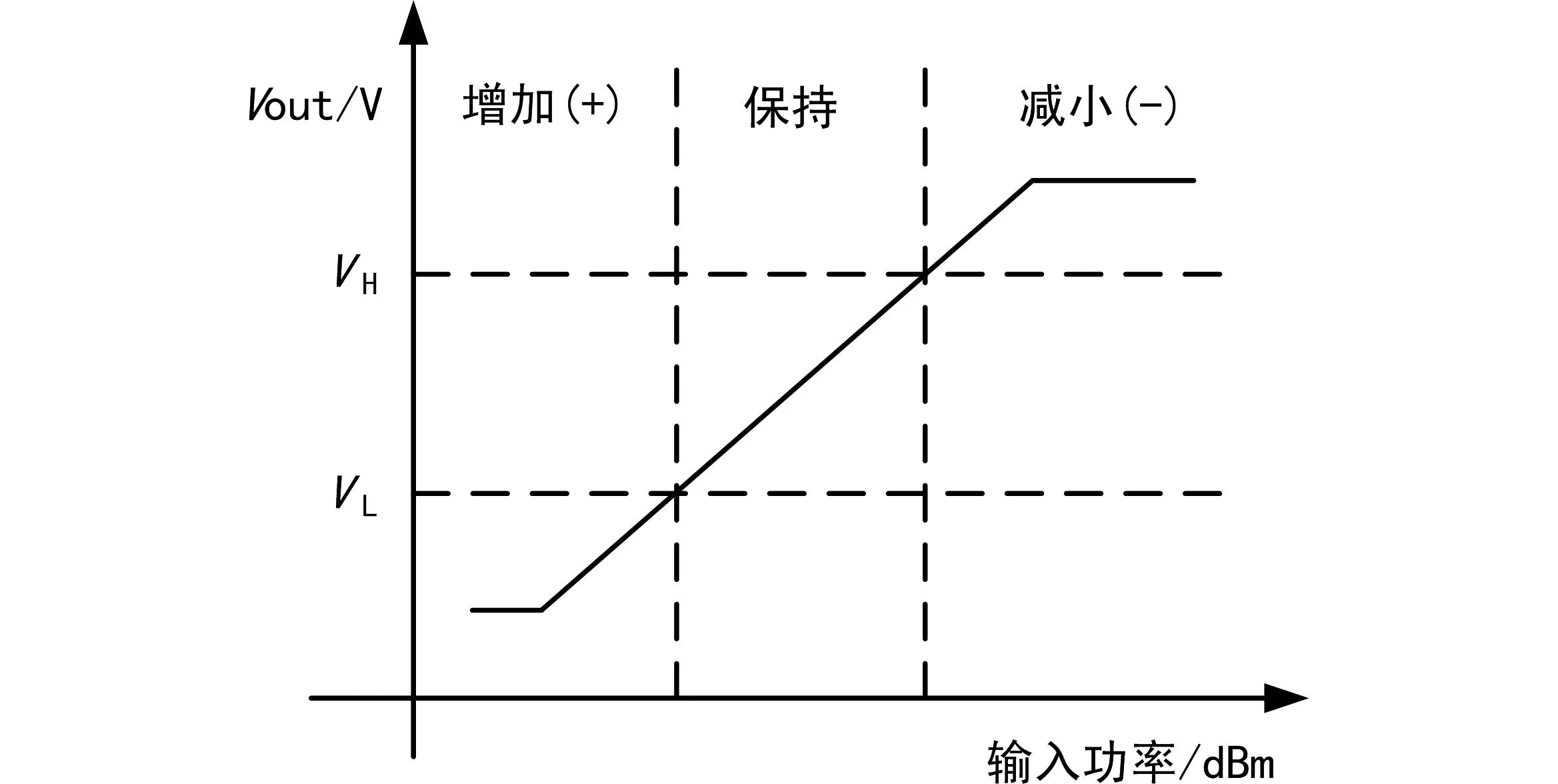

为确保输出信号幅度正确稳定,AGC电路必须设置合适的阈值电压,使信号幅度能稳定在正确的幅度,同时还需要保证环路稳定,使信号不发生包络振荡。本收发机芯片中,自动增益控制环路采用峰值检测,如图4所示,设置波形幅度高位为VH,低位为VL。二者之间为可接受的幅度波动,不需要调整增益。当幅度高于VH时,降低增益,当幅高于VL时,增加增益,以此使输出波形峰值恒定。通过比较器,使用数字代码,10、01和00来分别表示波形峰值高于VH,低于VL,以及在二者之间。然后传送数字代码到数字逻辑算法,以改变可变增益放大器的增益,使输出保持恒定。

图4 比较器规则图形

信号进入峰值检测电路,输出信号峰值电平,分别送入2个比较器和阈值电压进行比较,输出比较结果,如图5所示。

图5 峰值比较器原理

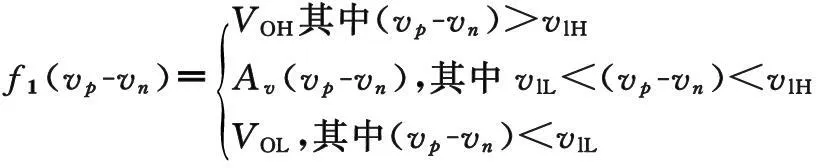

本文采用的比较器为2级比较器,如图6所示,比较器的数学表达式[11]为:

图6 2级比较器

峰值检测保持电路如图7所示。当比较器2个输入端之间存在电压差时,就会在输出端产生一个电压,经过一个PMOS产生电流为电容C1充电,电容上的电压反馈到比较器的正输入端vp。如此构成一个反馈电路实现跟踪输入信号的作用。由于PMOS管与电容C1构成充电支路,无法对其进行放电。所以在输入信号到达峰值后继续减小时,电容上的电压只保留了最大值,进而实现了输入信号峰值保持的作用。另外,电容正端和MOS管构成复位电路,当对信号进行峰值检测保持以及ADC对信号峰值进行模数转化过程中,此MOS管处于关断状态,当接收到复位信号后,MOS管导通,快速泄放掉电容C1上的电荷,以便对后续输入信号的处理工作。

图7 峰值检测电路

3仿真结果分析

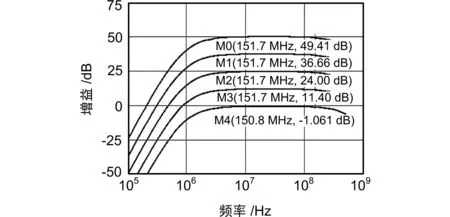

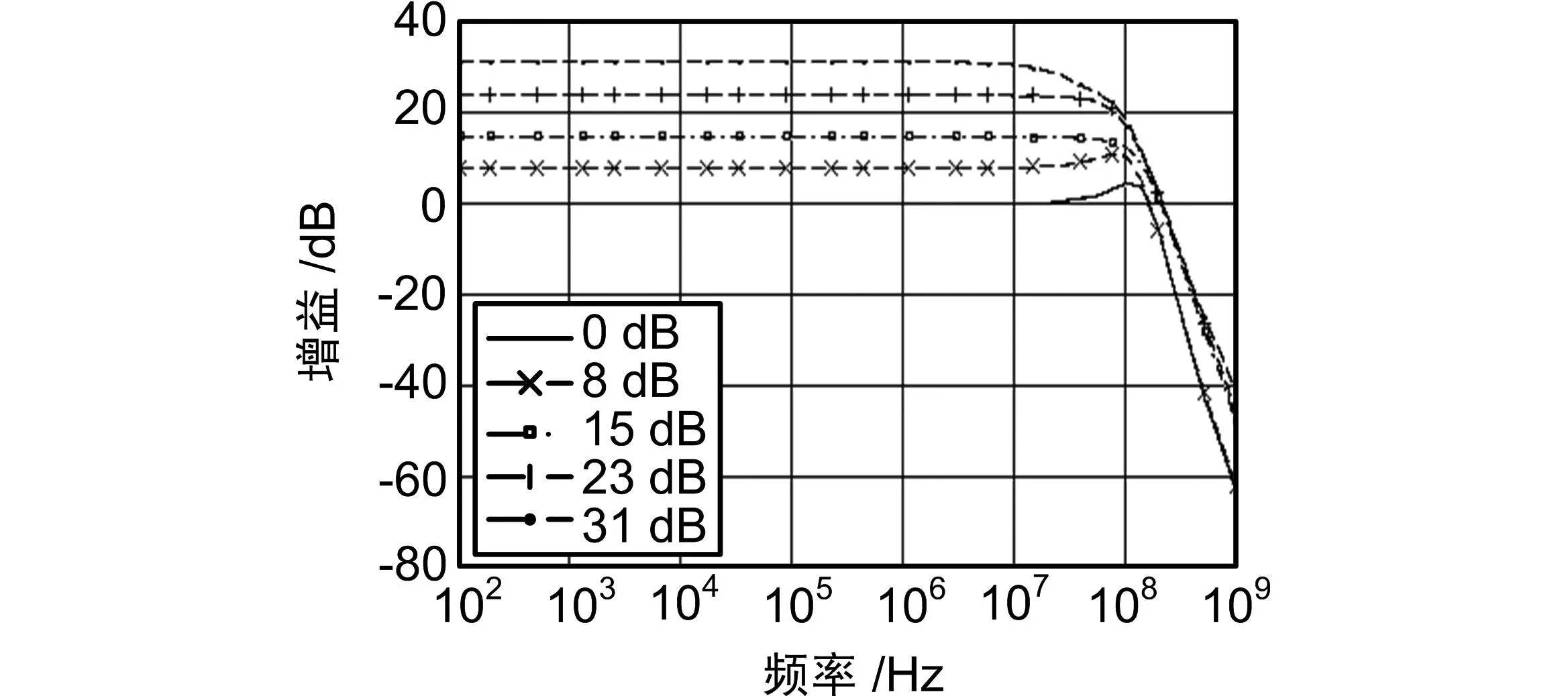

这部分给出了自动增益控制中各个可变增益部分的仿真性能结果。PGA和VGA的增益仿真波形如图8和图9所示。PGA的工作频率为150 MHz,最小增益步长为12 dB。VGA的带宽为10 MHz,最小增益步长为1 dB,实现0~35 dB的增益控制。仿真结果显示,2个模块的增益都满足设计要求。图9中抽样给出了0 dB、8 dB、15 dB、23 dB和31 dB的增益仿真结果。

图8 AGC增益仿真曲线

图9 VGA增益仿真波形

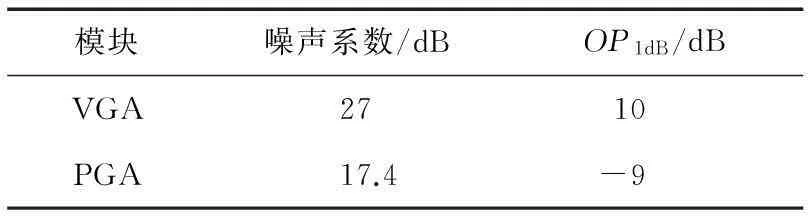

为了满足宽带电台中射频接收机对线性度的要求,在线性度和噪声系数之间进行了折衷,PGA和VGA的噪声系数和输出1 dB压缩点的仿真结果如表1所示,达到设计指标要求。

表1 PGA和VGA的性能仿真结果

4结束语

针对宽带电台的特殊应用环境,设计了一款应用于射频接收机芯片中的自动增益控制环路。详细分析了电路中各个组成部分的电路设计思路并给出了系统的仿真结果。通过仿真结果初步验证了电路实现了AGC的功能指标和性能指标。采用0.13 μm CMOS工艺,使得该模块可以和数字电路集成在一块芯片中,大大降低了芯片尺寸,提高了集成度,并且提升了系统的运行速度[12]。在实现电路功能指标的前提下,综合考虑了电路线性度和功耗之间的折衷,大大提升了AGC环路的线性度,避免了信号传输过程中的增益压缩等非线性失真。

参考文献

[1]NGUYEN H H,NGUYEN H N,LEE J S.A Binaryweighted Switching and Reconfiguration-based Programmable Gain Amplifier[J].IEEE Trans.Circuits Syst.Ⅱ,2009,56(9): 699-703.

[2]CORO G A,ANTONIO A R J L,JAIME R A.Micropower Class-AB VGA with Gain-independent Bandwidth[J].IEEE Trans.Circuits Syst.Ⅱ,2013,60(7): 397-401.

[3]SO Y K,JANG J Y,Oh I Y,PARK C S.A 2.16 m W Low Power Digitally-controlled Variable Gain Amplifier[J].IEEE Microw Wireless Compon,2010,20(3): 172-174.

[4]LIU C,YAN Y P,XIONG Y Z.A 5 Gb Sautomatic Gain Control Amplifier with Temperature Compensation[J].IEEE J.Solid-State Circuits,2012,47(6): 1 323-1 333.

[5]CHOI I,SEO H,KIM B.Accurate dB-linear Variable Gain Amplifier with Gain Error Compensation[J].IEEE J.Solid-State Circuits,2013,48(2): 456-464.

[6]拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2008:84-108.

[7]THANACHAYANONT A,NAKTONGKUL P.Low-voltage Wideband Compact CMOS Variable Gain Amplifier[J].Electronics Letters,2005,41(2): 51-52.

[8]ELWAN H O,ISMAIL M.Digitally Programmable Decibel-linear CMOS VGA for Low-power Mixed- signal Applications[J].IEEE Transactions on Circuits and Systems Ⅱ,2000,47(5): 388-389.

[9]KOM Ji-hun,CHAE Chang-seok,WOO Young-Jin,et al.A CMOS Variable Gain Amplifier with Wide Dynamic Range and Accurate dB-Linear Characteristic [C]∥ The 8th International Conference of Advanced Communication Technology,2006: 831-835.

[10]KWON J K,KIM K D,SONG W C,et al.Wideband High Dynamic Range CMOS Variable Gain Amplifier for Low Voltage and Low Power Wireless Applications[J].Electronics Letters,2003,39(10): 759-760.

[11]艾伦.CMOS模拟集成电路设计[M].北京:电子工业出版社,2012:359-396.

[12]Willy M C Sansen.模拟集成电路设计精粹[M].北京:清华大学出版社,2007:181-200.

赵思棋男,(1991—),硕士研究生。主要研究方向:模拟集成电路设计。

李斌男,(1972—),研究员。主要研究方向:集成电路设计。

作者简介

收稿日期:2015-11-24

中图分类号TP391.4

文献标识码A

文章编号1003-3106(2016)03-0079-04

doi:10.3969/j.issn.1003-3106.2016.03.22

引用格式:赵思棋,李斌.宽带电台中的CMOS自动增益控制设计[J].无线电工程,2016,46(3):79-82.