对PSO结构的设计与优化

严 伟 时广轶 常 莹 北京大学 北京 100084

对PSO结构的设计与优化

严 伟 时广轶 常 莹 北京大学 北京 100084

【文章摘要】

本文基于低功耗电源门控技术,提出了通过分簇的方式改变PSO安放结构,并对局部的PSO采取常关的一个状态。进一步减小门控单元本身的消耗功率。本文中对整个电源门控分簇,采用的中等粒度的插入方式,得到了三种关键因素同时优化的结果。

【关键词】

电源关断;IR压降;功耗

1 电源关断技术的简介

在布局布线的时候,使用后端工具通过在模块的顶部或底部设计Power Switch开关,可以关断一段时间内不工作的模块供电。这样做可以使模块进入休眠模式,此时的漏电流很小即功率也会很小。激活时,通过保持寄存器的记忆状态,可以使模块快速的恢复到关断钱的状态。这就是电源门控的概念。

电源门控的方式分为细粒度和粗粒度两种方式。细粒度的电源门控方式其电源开关位于单个标准单元内部;粗粒度的电源门控方式其电源开关位于标准单元外。前者会增加面积的消耗。可行性较低;后者则存在较大的电压降以及过大的过冲电流的危险。设计者需要优化电源门控的数量以及位置来优化整个电源网络的设计。

2 采用PSO方法电源规划设计的评价方法

2.1IR压降,EM效应和占用的布局布线资源

IR压降即指由于电源Pad到它所供电的逻辑单元之间存在等效电阻而导致电源或地网络电压下降或者升高的一种现象。IR压降会导致逻辑门的错误并且降低芯片速度。所以IR压降电源规划要考虑的重要因素。电迁移是由流经金属线与通孔平均电流引起一种直流现象。这是深亚微米电源网络设计中出现另外一种重要问题。虽然EM可能会造成电源网格中电路开路或短路,但最常见影响还是电源网络路径中电阻值增加,由此引起IR压降或地线反弹,从而影响到芯片时序。此外要考虑的是布局布线的资源。PSO的放置的位置和数量都将占用整个设计的布局资源,会导致芯片成本的增加。而电源网络的金属线则会占用布线资源,造成布线的拥堵问题。所以布局布线的资源占用也是电源规划中需要考虑的重要方面。

3 针对项目设计PSO

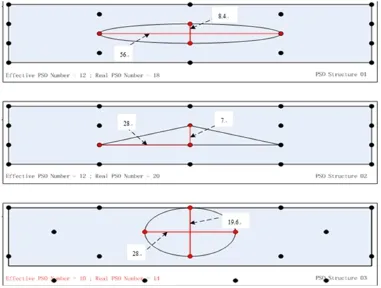

本文使用的分析工具是Candence公司推出的voltus,它可以让电网输送更多的电流,以便驱动各个逻辑门。Voltus可以分析哪些逻辑门区域电压不够。voltus在功耗分析过程中中,通常需要四个步骤:1.计算漏电流、开关电流和内部电流;2.进行分析,进行电压降、电迁移检查等;3.进行布局优化;4.如果电压下降太多,时序就会发生变化。所以平衡电压和时序,使设计完全收敛。三种结构的示意图如下,其中第三版的优化版是跳跃的row是5。

三种电源网络的PSO结构使用的基本条件都是一致的,即同样的lib,SPEF,同样的频率,以及开关转换率等。此次的电源网络的研究是仅仅改变PSO的结构就可以达到结果的优化。

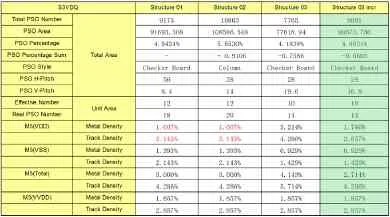

3.1三种结构的关键因素对比分析

所占金属的密度和水平竖直方向的布线拥塞有关:更少的PSO单元可以释放更多的面积进行放置标准单元并进行优化。更少的布线密度可以释放更多的布线资源。我们可以看出优化后的结构03拥有更小的金属层密度,但是与结构1的布线密度相同。

3.2动态压降门控压降以及功耗的分析对比

动态压降根据数据得出结构2有最小的动态压降为3.33%,但是却比结构1多出了1690个pso单元。这样会占用很多布局资源。结构3优化版的压降4.11%是与结构1相比有2.33%的Static Drop的提高,同时又有更优的布局布线资源的节省。结构3的压降是5.44%。从以上的分析中我们也可以得到结论:动态压降违规与PSO单元所占布局百分比和结构有很大的关系。

门控压降是指本身PSO所消耗的那部分电压,报告得出内部功耗压降都是保持在ARM推荐的5%以内。从结构1到结构3优化版分别为3.36%,2.46%,4.55%和3.18%。

静态功率上来看,结构3优化版较结构1也有所提高。结构1到结构3优化版分别是1835mw,1701mw,1788mw和1805mw。

结论从占用布局布线资源和IR Drop的综合分析得到结论第三版本的设计最优,验证了通过改变PSO的安放位置就可以达到优化功耗的结果,同时满足了时序和面积折中的最佳效果。

【参考文献】

[1]Michael Keating.Low Power Methodology Manual For System-on-Chip Design [M].USA Synopsys' Inc &ARM Limited, 2007.

[2]曾晓洋.腾兴宁.SOC低功耗设计方法研究[D].上海:复旦大学,2008.

[3]梁允萍.章成昱等.数字IC低功耗设计综述[J].硅谷,2009,10: 23-24.

表 密度对比