一种高速数据采集系统的设计与实现

,

(中国电子科技集团公司第三十八研究所, 安徽合肥 230088)

0 引言

随着高分辨SAR技术的发展,星载SAR逐渐成为研究的热点。在星载SAR系统中,高分辨率和宽测绘带一直是人们所追求的目标[1]。由于脉冲重复频率的限制,传统星载SAR不能同时实现高分辨和宽测绘带。为满足新体制SAR雷达的关键性技术验证,对数据采集系统提出了大带宽、多通道、多模式、高速采集、高速存储的要求。

随着电子行业的发展,高速ADC芯片和可编程门阵列(FPGA)的性能发展迅速,为高速采集系统的工程实现提供了支持,如今一般采用FPGA对多核ADC芯片进行拼接采样配置以达到高速采样率[2]。拼接高速采样需要解决如高速信号完整性、数模混合PCB板布局布线设计、ADC通道不一致性、高速串并转换同步、高速数据传输、存储等难题[3]。在SAR雷达系统中需要具有灵活的动态配置能力,能够实时根据系统的需求完成不同的采集功能,传统的数据采集系统一般无法满足这些需求。

本文描述的数据采集系统是针对某星载SAR雷达关键性技术验证的需求开发的,ADC芯片完成对模拟正交解调的I/Q信号的基带采样,I/Q信号的最大带宽为1.2 GHz,单路I/Q信号通过4片ADC核拼接达到2 GS/s的采样率。采样后的数据传输至信号处理板,在FPGA中完成串并转换、数据的对齐校正、降速处理等相关控制处理,最后打包由光纤传输至记录仪单机,记录仪可进行高速数据大容量缓存,通过PCI-E总线转储于计算机中[4]。

1 系统方案

数据采集单机的输入信号为模拟正交解调输出的基带I/Q信号,在不同的工作模式下,每对I/Q信号的带宽分别为300 MHz,600 MHz,1.2 GHz,单路I/Q信号的采样率为2 GHz。为了最大限度抑制I/Q输出数据的不平衡性,改善信号的信噪比,数据采集单机使用一个四核ADC芯片完成一对I/Q信号的数字化。FPGA为采集单机的核心组件,它主要完成ADC芯片的配置,时钟芯片的配置,RS422、光模块接口的时序控制,信号处理等功能。

整个系统由计算机控制,计算机发出采样触发、采样深度、选通通道、抽样率等配置信息后,ADC采样后的信号在FPGA中经过相关处理后由光纤传输至记录仪中,记录仪将数据写入DDR3中,可由计算机控制将DDR3中数据通过PCI-E总线转储至计算机中。系统结构如图1所示,本文主要介绍采集单机软硬件设计。

图1 数据采集系统框图

2 硬件设计

根据雷达系统的需求,综合考虑成本与指标实现,宽带数据采集的采样率定为2 GHz,ADC芯片选用E2V公司的EV10AQ190,其模拟带宽可达3 GHz,每个芯片支持二通道2.5 GS/s采样[5],因此,一片ADC可以完成一对I/Q信号的数字化。

FPGA是整个系统的核心,它完成ADC、时钟等芯片的配置,串口、光口的时序控制。同时需要满足整个雷达系统多通道、多模式、高速的要求,对片内RAM资源、逻辑资源、高速信号处理能力都有很高的要求。本设计中系统时钟工作于250 MHz,综合考虑选用Xilinx公司高端系列Virtex7VX485T芯片。

一对I/Q信号对应的数据传输速率计算如下:2 Gbit/s(采样率)×8 bit(位宽)×2(通道数)×10/8(8B10B编码)=40 Gbit/s。实际工作中数据采集并不是一直处于数据传输状态,根据最大脉冲重复频率和回波采样窗长度可以计算,每两个采样触发之间数据传输速率达到20 Gbit/s即可完全满足系统要求。本设计采用TLD850M10GT光模块完成4×5 Gbit/s高速串行数据传输。

在超高速数据采集系统中,LVDS电路的时钟信号都大量采用差分传输的技术,高速串行传输数据采取差分传输。由于两路差分信号的电流回路不可能完全一致,就会产生一部分无法抵消的共模电流,共模电流绘产生共模辐射,影响系统的电磁环境等[6]。

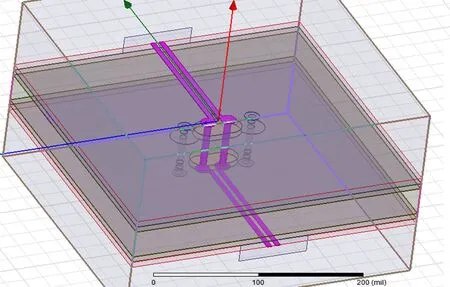

本设计中,高速串行总线传输速率为5 Gbit/s的差分信号,走线需要差分过孔互连。对于高速信号,阻抗的不连续性对信号完整性影响非常大[7],采取增大过孔和铺铜区的距离、减少焊盘的直径,并且在差分过孔旁边增加伴地孔形成信号回路来减小阻抗的不连续性。图2为电磁仿真软件HFSS进行的差分过孔结构仿真结果。

(a)有伴地孔情况下差分过孔结构

(b)优化后差分过孔结构差模回损S11曲线图2HFSS仿真结果

3 FPGA内部逻辑设计

FPGA是整个系统的核心,它通过SPI接口配置EV10AQ190和AD9516芯片,使其工作于设想的工作方式;对RS422,高速串行总线(SERDES)进行时序控制,使系统准确接收上位机的控制命令和采样触发等信息,同时完成和记录仪的高速数据传输;它通过串并转换把ADC高速数据降速至工作时钟处理,完成各种模式下数据的存储、抽取、选通发送等功能[8]。FPGA主要模块结构如图3所示。本文主要介绍时钟复位模块、数据流处理模块的设计和实现。

图3 FPGA内部结构图

3.1 时钟复位模块

在FPGA设计中,一般在确定接口之后首先要考虑的就是时钟和复位[9]。时钟和复位的设计不稳定可能会导致整个系统的崩溃,所以设计好时钟和复位模块是整个内部逻辑设计的首要任务。

对于FPGA内部逻辑设计,全局时钟是最简单和最可预测的时钟,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。在设计中一般尽可能地采用由专用全局时钟来驱动各个模块。本设计的输入时钟为接收前端提供的20 MHz时钟,以及两片ADC芯片提供的500 MHz时钟,利用FPGA提供的Clocking Wizard IP核,生成设计需要的所有时钟。

采集单机在每次上电时,FPGA芯片、AD芯片、时钟芯片、光模块等器件的初始状态都是不确定的,所以复位逻辑设计非常重要,它可以避免整个系统处于一种不确定的状态。本设计的复位逻辑流程图如图4所示。

图4 复位逻辑流程图

FPGA刚上电时,20 MHz信号处于失锁状态,复位逻辑开始工作,等待20 MHz信号锁存成功便开始一步步对各芯片、模块、内部逻辑进行复位。当正常工作状态中间出现不稳定状态也会重新进入复位状态,例如ADC输入的500 MHz时钟信号出现了失锁状态,在不复位的情况下500 MHz信号可能会重新锁存成功,但是此时信号的相位关系是不确定的,由于高速串并转换本身对时钟和数据的相位关系非常高,原本没有毛刺的数据可能会出现毛刺,从而影响整个系统的使用,所以一旦时钟失锁等问题出现时需要重新进行复位使整个系统处于稳定的状态。

3.2 数据流处理模块

随着信息化产业的发展,ADC的采样率越来越高,对FPGA的数字信号处理带来了很大压力。本设计中ADC输出单路信号的数据率为1 Gbit/s,FPGA的工作时钟频率无法匹配如此高的数据率,使用FPGA内部集成的高速串并转换IP核实现高速AD数据的4倍降速处理,这是典型的空间换取时间的设计策略。单片ADC芯片输入I/Q信号各20位、40位信号都需要进行串并转换,由于PCB板上线长不可能完全相等,以及FPGA内部时钟和数据的走线长度不可能完全一致,同时时钟频率非常高对数据与时钟的不同步非常敏感,会导致有些串并转换的结果有毛刺。FPGA内部集成的IDELAYE2模块可以设置时钟或数据的延迟[10],可以通过设置VIO核控制延迟,使用Chipscope(嵌入式逻辑分析仪)软件在线选择合适的范围完成所有模块的时钟数据同步,如图5所示。

(a)时钟数据不同步

(b)调整延迟使时钟数据同步图5时钟数据同步调整

雷达在不同工作模式下的主波信号也不同,是其带宽分别为300 MHz,600 MHz,1.2 GHz及双子带合成2.4 GHz的线性调频信号。对于300 MHz,600 MHz的I/Q信号,相应回波时间窗内的数据在2 GHz采样下传输的数据在一个重复脉冲内记录仪无法完成存储,根据奈奎斯特采样定理可以对300 MHz,600 MHz带宽信号进行4倍、2倍抽取。本设计采用FIFO来完成数据的抽取,时钟域的转换(工作时钟到高速串行发送时钟),数据缓存、封装,采样深度、通道选通等功能的实现。数据帧封装发送模块通过控制FIFO的读使能来打包数据和配置信息,并按照与记录仪通信协议进行帧格式封装,最后按照SERDES高速串行总线的传输格式传输数据和K字符至FPGA自带的SERDES IP核中,其架构如图6所示。

图6 采集单机信号缓存发送架构

4 测试结果及分析

测试结果包括采集单机接收数字信号的信噪比,以及由记录仪传送至计算机中数据的相干性和脉冲压缩结果。

测试数字采集信号的信噪比(SNR)的方法如下:使用3台信号源分别提供0.1~600.1 MHz的正弦信号输入、20 MHz同步时钟和2 GHz采样时钟,输入正弦波信号幅度为0 dBm,信号频率从0.1 MHz步进频率为100 MHz扫频至600.1 MHz结束,通过嵌入式逻辑分析仪软件Chipscope在线记录采集数据,导入MATLAB中进行FFT等运算,计算SNR。图7为100 MHz的频谱图,测试结果如表1所示。在常温条件下测试结果表明,工作带宽内信号信噪比可达到45 dB。

测试数据相干性和脉冲压缩结果的方法如下:接收前端主波信号输入采集系统,由上位机控制采样触发等参数,记录一段时间的采集数据,导入MATLAB中分析计算。图8为100次采样触发记录的波形显示,重合程度非常高,相干性非常好。图9为脉冲压缩结果,脉压结果正常。

图7 100 MHz信号频谱图

表1 数字采集的信噪比和无杂散动态

(a)I路信号

(b)Q路信号图8100次采样触发下信号采集数据

图9600 MHz带宽线性调频脉冲压缩结果

5 结束语

本文介绍了基于高采样率ADC、FPGA的多通道高速采集系统,详细介绍了系统软硬件实现的技术难题和解决方法。通用的硬件设计可以通过更改采集子板等措施适应SAR雷达系统不同课题的科研需求,同时由于FPGA的灵活性,系统可以进一步升级,结合多速率信号处理技术,应用于宽带数字接收系统,符合软件无线电的发展思路,值得进一步的研究。

[1] 邓云凯,赵凤军,王宇. 星载SAR技术的发展趋势及应用浅析[J]. 雷达学报, 2012, 1(1):1-10.

[2] BLACK W C, HODGES D A. Time Interleaved Converter Arrays[J]. IEEE Journal of Solid-State Circuits,1980, 15(6):1022-1029.

[3] 向海生,马利祥,王冰. 基于拼接采样技术的宽带数字接收机[J]. 雷达科学与技术, 2014, 12(4):450-453.

[4] 马鸣锦,朱剑冰,何红旗,等. PCI、PCI-X和PCI Express的原理及体系结构[M].北京:清华大学出版社, 2007.

[5] E2V Inc. EV10AQ190 Datasheet[DS/OL]. [2015-08-16]. http∥www.e2v.com.

[6] 白同云. 电磁兼容设计[M]. 2版. 北京:北京邮电大学出版社, 2011.

[7] 张木山,李玉山. 信号完整性分析与设计[M]. 北京:电子工业出版社, 2010.

[8] 张奕,余海龙,谭剑美. 四通道高速数据采集系统设计[J]. 现代电子技术, 2012, 35(9).10-12.

[9] WILSON P. Design Recipes for FPGAs[M]. London:Newnes, 2007.

[10] Xilinx Inc. UG471:7 Series FPGAs SelectIO Resources User Guide[Z/OL]. [2015-09-26]. http:∥www.xilinx.com.