从设备存储器窗口遍历机制设计与实现

马 超,丁 挚,田 泽,王 婷

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068;3.西安现代控制技术研究所,陕西 西安 710065)

MA Chao1,2,DING Zhi3,TIAN Ze1,2,WANG Ting1,2

从设备存储器窗口遍历机制设计与实现

马 超1,2,丁 挚3,田 泽1,2,王 婷1,2

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068;3.西安现代控制技术研究所,陕西 西安 710065)

目前基于总线接口构成的计算机系统在应用中占据主流地位,并仍将持续作为主流。随着计算机系统及应用的复杂度的不断提高,对外部存储资源的需求越来越大。然而存储资源的不断增大以及存储功能的正确与否大大增加了前期设计验证工作的难度并影响了系统的准确性。文中采用总线接口架构,提出了一种接口总线从设备存储器窗口遍历机制,具有不限制存储系统频率、不限制存储大小的优势。通过窗口更新,实现由主机对存储系统的遍历访问,在系统设计初期完成对外部存储资源功能的验证,极大提高了前端设计以及芯片测试中验证测试的准确性。

计算机系统;总线接口;从设备;窗口遍历

MA Chao1,2,DING Zhi3,TIAN Ze1,2,WANG Ting1,2

0 引 言

计算机系统的不断发展,加大了外部存储资源对带宽、传输效率的依赖,同样也极大地增加了对前期测试验证的难度[1-2]。随着处理效率及性能要求的增加,保证写入存储系统中数据的可测性,成为设计过程中的关键[3]。

为此,在设计中增加主机直接访问存储系统的通路,能够在最大限度上保证前期设计、调试的正确性[4-5]。

1 调试通路设计

1.1 设计及实现

主机通过从通道设计实现对存储的读写访问。主机从通道窗口遍历机制架构如图1所示。

图1 主机从通道窗口机制架构图

窗口机制访问存储操作序列:

(1)主机通过MEM类型从接口,配置窗口寄存器,该寄存器有效位与外部存储资源大小相关,依据外部存储大小,确定窗口寄存器有效位。通过配置该寄存器,完成主机对外部存储资源的窗口映射。

(2)由主机发起访问外部存储的读写操作,基地址由主机配置寄存器完成配置。

(3)更新窗口寄存器,执行下一次读写操作。

1.2 窗口遍历存储机制

为方便主机灵活高效地访问存储系统,允许主机发起单拍访问/Burst读写访问存储系统,采用FIFO类型从通道接口作为调试通路设计基础[6]。

存储的不断增大提高了系统性能,同时受限于主机的带宽,无法作为对外部主机的全部可见,然而,通过窗口机制的设计,能够实现主机对外部存储空间的遍历[7-8]。

窗口机制是主机通过配置窗口寄存器确定访问存储的基地址,结合主机从通路基地址寄存器,完成对外部存储资源的地址映射关系。

根据存储大小,在窗口寄存器的设计中确定寄存器的有效位数。主机配置寄存器的通路是通过从通道MEM类型实现,所以在完成窗口寄存器设计后,仍需实现从通道MEM类型接口到从通道FIFO类型接口的数据传输。保证在FIFO类型接口操作发起时,窗口数据已更新[9]。

1.3 输出控制子模块

输出控制子模块作为主机访问存储系统的核心逻辑,完成外部主机和存储管理与控制单元的读写交互,实现外部主机通过存储管理与控制单元完成对外部存储的读写操作。通过跨时钟域处理,实现存储管理与控制单元的反馈信号以及PCI控制信号的控制及交互[10]。

1.3.1 写操作的设计

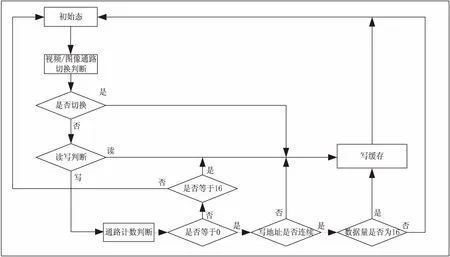

主机访问存储系统的写操作设计方法如下:

(1)判断是否发生主机访问存储系统中通路的切换;

(2)如果检测到发生了通路的切换且缓存内有未向存储系统发送的数据时,将上一次写操作的数据、地址、字节使能等信息写入缓存内;

(3)如果未检测到通路的切换,判断本次操作;

(4)若本次操作为写操作,判断通路计数是否等于0,如本次操作为读操作,将上一次写操作的数据、地址、字节使能等信息写入缓存内;

(5)若通路写数据计数等于0,判断本次操作的地址与上一次写操作的地址是否连续,若通路写数据计数等于16,则将上一次写操作的数据、地址、字节使能等信息写入缓存内,若不等于0且不等于16,则返回初始状态;

(6)若本次操作访问的地址与上一次写操作访问的地址连续,则继续判断是否写入满16个字;

(7)若写满16个字,则将32位下数据拼接成256位,并将本次写操作的数据、地址、字节使能等信息写入缓存内,若未写满,则返回初始态。

主机访问存储系统写操作状态如图2所示。

1.3.2 读操作的设计

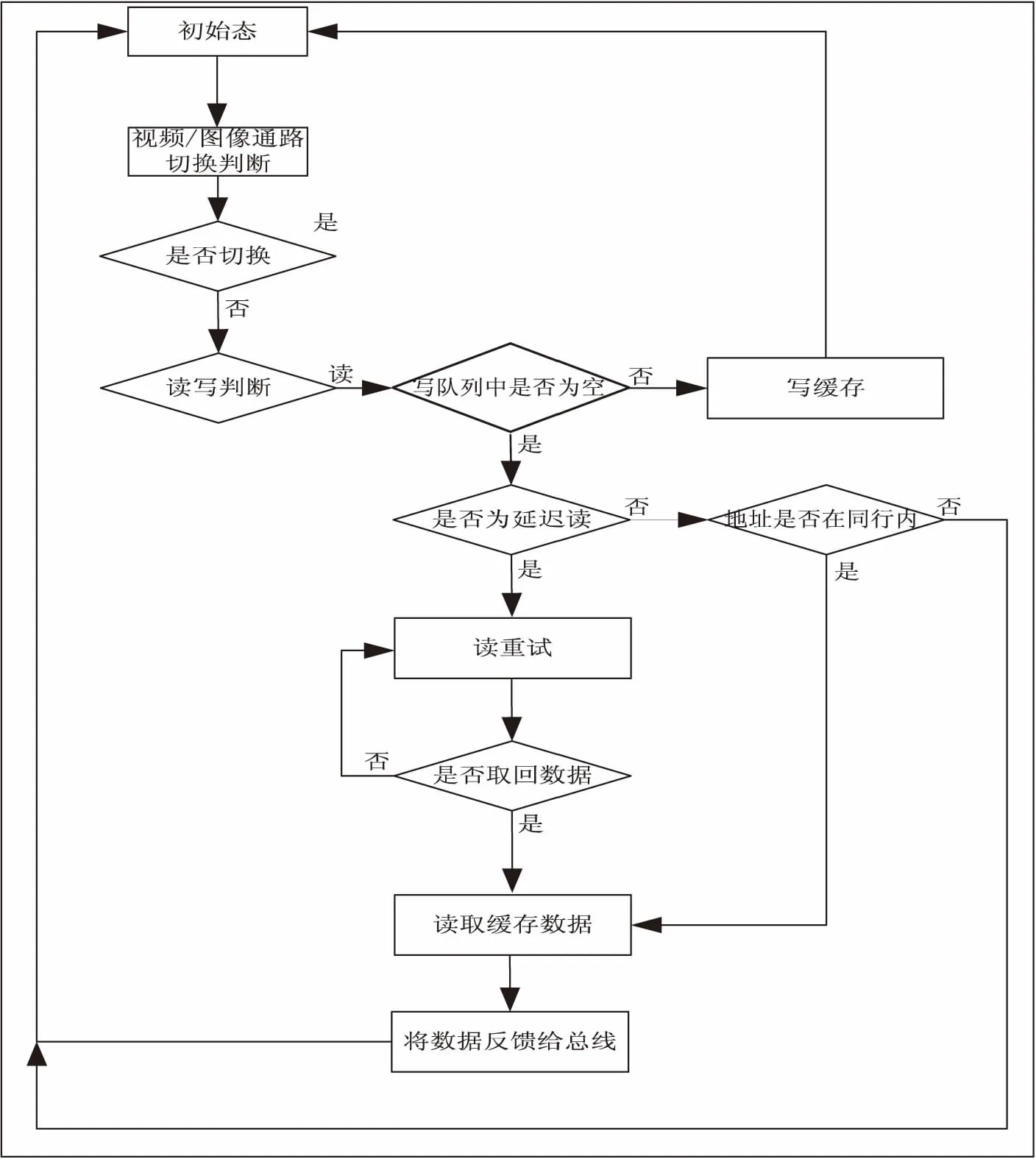

主机访问存储系统的读操作设计方法如下:

(1)主机发起读操作后,判断缓存是否为空;

(2)若写队列非空,则将写队列内数据写入缓存,若写队列空,判断本次操作是否为延迟读;

(3)若为延迟读,重试主机,并等待后端逻辑按照读操作地址取回数据;

(4)若为立即读,判断本次读操作地址是否在上一次读操作地址的同一行内;

(5)读重试中,若取回有效数据后,按照单拍或Burst操作类型,将256位数据拆分成若干32位数据,并将数据反馈给主机,回到初始化;

(6)若立即读操作地址在上次读操作的同一行内,则从缓存中取回数据,按照单拍或Burst操作类型,将256位数据拆分成若干32位数据,反馈给主机,回到初始化。

主机访问存储系统读操作状态示意如图3所示。

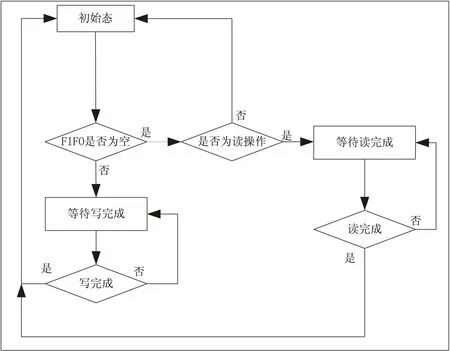

1.3.3 内部缓存控制

缓存控制由两部分设计实现:向主机发送请求和数据缓存、地址控制位缓存。

其中数据缓存通过DPRAM实现,地址控制位通过FIFO实现。

图2 写操作状态示意图

图3 读操作状态示意图

主机数据位宽32位,存储系统接口数据位宽为256位,通过内建DPRAM存储,将主机32位数据位宽拼接成256位数据位宽后存入DPRAM(若主机单字操作,则其余位补零),待存储管理与控制单元接到请求后,读取该DPRAM内的数据,已完成外部主机对存储管理与控制单元的数据写操作[11-12]。

主机对存储发起写操作时,不仅要将数据准确地发送给存储系统,还需要将地址等关键控制信息发送给存储。将地址、字节使能以及窗口偏移地址拼接成48位数据压栈到FIFO内,与数据同时发送给存储系统,以保证主机读写数据的一致性[13-14]。

存储控制状态如图4所示。

图4 存储控制状态示意图

2 结 论

通过主机接口设计,实现了主机对外部存储资源的直接读写访问,有效解决了低速低优先级主机接口访问高速外部存储时频繁向外存发起请求,外部存储频繁仲裁而引起的效率及准确率过低的问题,大大提高了访问效率,保证了前端设计的准确性。

3 结束语

通过主机访问存储系统来实现主机端对存储器的直接读写访问,通过32位寄存器,依据不同的外部存储大小,选用不同有效位作为窗口结合PCI主机配置空间T1通路配置基地址寄存器,将主机对窗口的访问映射到外部存储资源,实现了通过窗口映射对外部存储资源的遍历访问。一方面能够在设计过程中确保整体功能的正确性,能够以最快的时间通过主机对存储的读写来定位问题,保证了设计进度及功能正确;另外,在芯片测试时也能够提供更加直观的存储功能的判断。然而受限于存储系统数据位宽与主机接口数据位宽的不匹配以及存储系统竞争机制中主机访问的优先级问题,导致以往的设计中很少能够实现由外部主机直接对片外存储的有效读写访问,因此该设计充分考虑了主机访问存储系统的操作类型、操作顺序以及存储对外部读写访问的处理、竞争机制的特点,实现了在不限制外部主机操作类型、操作顺序以及不影响存储系统与其余功能单元的数据交互的前提下,由主机直接访问存储系统的功能,解决了日渐增加的外部存储资源对前端设计造成的设计隐患,极大提高了前端设计验证的效率,保证了前端设计功能的准确性。

[1] 蔡士杰,宋继强,蔡 敏.计算机图形学[M].第3版.北京:电子工业出版社,2007:10-21.

[2] 徐新海,林宇裴,易 伟.CPU-GPGPU异构体系结构相关技术综述[J].计算机工程与科学,2009,31(A1):24-26.

[3] Wolf W.High performance embedded computing architectures,applications,and methodologies[M].New York:Elsevier,2007.

[4] 128-bit processor local bus architecture specifications[M].[s.l.]:IBM,2004.

[5] Patnaik G,Corrigan A.Efficient utilization of a CPU-GPU cluster[C]//Proc of 50th AIAA aerospace sciences meeting including the new horizons forum and aerospace exposition.Nashville,Tennessee:[s.n.],2012.

[6] Rainald F C,Baum J D.Large-scale blast calculations on GPU clusters[C]//Proc of 50th AIAA aerospace sciences meeting including the new horizons forum and aerospace exposition.Nashville,Tennessee:[s.n.],2012.

[7] 贾 真,林 清.PCI总线应用设计与研究[J].现代电子技术,2008,31(10):85-87.

[8] 马安国,成 玉,唐遇星,等.GPU异构系统中的存储层次和负载均衡策略研究[J].国防科技大学学报,2009,31(5):38-43.

[9] 王 鹏,伊 鹏,金德鹏,等.基于三级存储阵列缓存高速数据包及性能分析[J].软件学报,2005,16(12):2181-2189.

[10] 张立倩,白凤山.基于PCI总线的数据传输系统设计[J].内蒙古大学学报:自然科学版,2005,36(1):84-88.

[11] 张伟栋,王国庆,崔红利.一种基于IP内核的PCI总线接口设计方法研究[J].航空计算技术,2008,38(5):115-118.

[12] 柳 钰,梅策香,吴继侠.PCI总线从设备控制器的设计与实现[J].微计算机信息,2009,25(7-2):278-280.

[13] 刘 鑫,许华荣.基于GPU的特征点提取与匹配算法比较[J].计算机辅助设计与图形学学报,2013,25(10):1496-1502.

[14] 刘海华,陈心浩.异步非透明PCI-PCI桥的应用研究[J].微计算机应用,2006,27(4):478-480.

Design and Implementation of Window Traversal Mechanism of

MEM Unit Accessing by Target Device

(1.Aeronautics Computing Technique Research Institute,Xi’an 710068,China;2.Aeronautics Science and Technology Key Laboratory of Integrated Circuit and Micro-system Design,Xi’an 710068,China;3.Xi’an Modern Control Technology Research Institute,Xi’an 710065,China)

The computing system based on bus-interface structure has been occupied large amount of implementation.With the huge increasing complexity of computing system and its application,the demand in chip-out MEM units has been increased either.However,the increasing of storage resources and storage function correcting or not significantly increases the difficulty of the preliminary design verification work and affects the accuracy of the system.A new windows traversal method in achieving the fully accessing to MEM units under the bus-interface-structure is proposed.This method allows the host device to access to MEM unit without any limitations in size of MEM unit and operation frequency.According to windows updating,implementing the traversal access to storage system by the host,completing verification of external storage resources functions in the early stage of system design,the veracity of design and completeness of verification would be enormously improving.

computer system;host interface;target device;windows traversal

2015-06-16

2015-09-22

时间:2016-05-05

中国航空工业集团公司创新基金(2010BD63111)

马 超(1984-),男,工程师,研究方向为集成电路设计与验证;田 泽,博士,研究员,中航首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计。

http://www.cnki.net/kcms/detail/61.1450.TP.20160505.0814.004.html

TP39

A

1673-629X(2016)05-0135-04

10.3969/j.issn.1673-629X.2016.05.029