基于FSM的控制系统设计与实现

丰 坤,李跃华,张金林,李佳炜

(空军预警学院,武汉 430019)

基于FSM的控制系统设计与实现

丰坤,李跃华,张金林,李佳炜

(空军预警学院,武汉 430019)

摘要:介绍了有限状态机的基本描述方式、评判标准、编码方式以及描述风格,并对比了不同编码方式和描述风格的优缺点,以局部动态可重构过程中控制系统的有限状态机为例,用Verilog HDL实现了3种不同描述风格的有限状态机,对比了它们各自的安全稳定性、RTL Viewer、资源消耗和速度,得出了有限状态机的最优描述风格。

关键词:有限状态机;描述风格;编码方式

0引言

随着微电子设计技术和硬件系统的飞速发展,基于现场可编程门阵列(FPGA)的动态可重构技术被广泛应用于生活中的各个领域,重构控制系统作为动态可重构的重要组成部分,引起了众多硬件开发者的关注。控制系统的主体是一个有限状态机[1](FSM),它描述了一个由有限个独立状态组成的过程,这些状态之间可以互相迁移直到最终离开这个过程[2]。FSM简单易读、结构清晰、设计灵话,易于建立、理解和维护,特别应用在具有大量状态转移和复杂时序控制的系统中,更显其优势[3]。目前,FSM已在数字电路系统设计中广泛应用。

本文介绍FSM的几种编码方式和描述风格,分析了FSM的几个评判标准,运用Verilog HDL语言,以3种不同的描述风格实现了动态重构过程中的控制状态机,从资源消耗、可靠性等方面对比3种不同描述风格的优缺点,选择最优的描述风格。

1FSM的基本特性

状态、输入和输出是状态机的3个基本要素,状态用来划分设计的逻辑顺序,输出根据是否与输入有关,将状态机分为摩尔型和米勒型两大类[4]。如果输出仅仅与当前状态相关,而与输入条件无关,那么该状态机为摩尔型状态机;如果输出不仅与当前状态有关,还受输入条件的影响,那么该状态机为米勒型状态机。本文中的控制状态机输出受到当前状态和输入的影响,所以选用米勒型状态机。

1.1 FSM的基本描述方式

状态机的基本描述方式有3种:状态转移图,状态转移列表,HDL语言描述。

状态转移图是FSM最直观的描述方式,这种描述方式直观、清晰、方便,很容易理解设计者的意图,其常用在设计的规划阶段来定义逻辑功能,在规模较小的状态机方面使用广泛。状态转移列表是用列表的方式描述状态机,在状态化简方面应用较多,但对安全性、稳定性要求较高的状态机,不用其来优化状态。用HDL语言描述状态机具有很大的优势,因为Verilog HDL[5]经过几十年的发展,已经由最初的私有语言演变成主流的硬件描述语言之一,在FPGA和专用集成电路(ASIC)的设计中应用较为广泛,且Verilog设计方便,应用灵活,维护修改快捷,可以根据不同标准完成不同功能的状态机。本设计使用Verilog HDL来描述状态机。

1.2 FSM的评判标准

状态机的评判标准有很多,下面从安全稳定、速度、面积以及复杂程度4个方面来讨论。

安全稳定:状态机要安全,稳定性高。安全主要指确保状态机工作在正常状态,不会进入死循环;稳定性高,要保证状态机最后的实现结果不受异常干扰,如毛刺等。

速度:这里的速度指设计稳定运行能够达到的最高频率,状态机要求速度快,能够满足设计的频率要求。

面积:这里面积是指设计中消耗的FPGA逻辑资源数量,状态机要求消耗逻辑资源数量少,即面积小。

复杂程度:状态机设计要清晰易懂,便于解读,以方便后续的维护。

在具体设计中,以上4条标准要综合考虑,满足设计要求。当评判标准发生冲突时,按照安全稳定、速度、面积以及复杂程度的顺序来考虑,也即是“安全稳定”优先级最高,必须优先考虑;“复杂程度”优先级最低,可最后再考虑。

1.3 FSM的编码方式

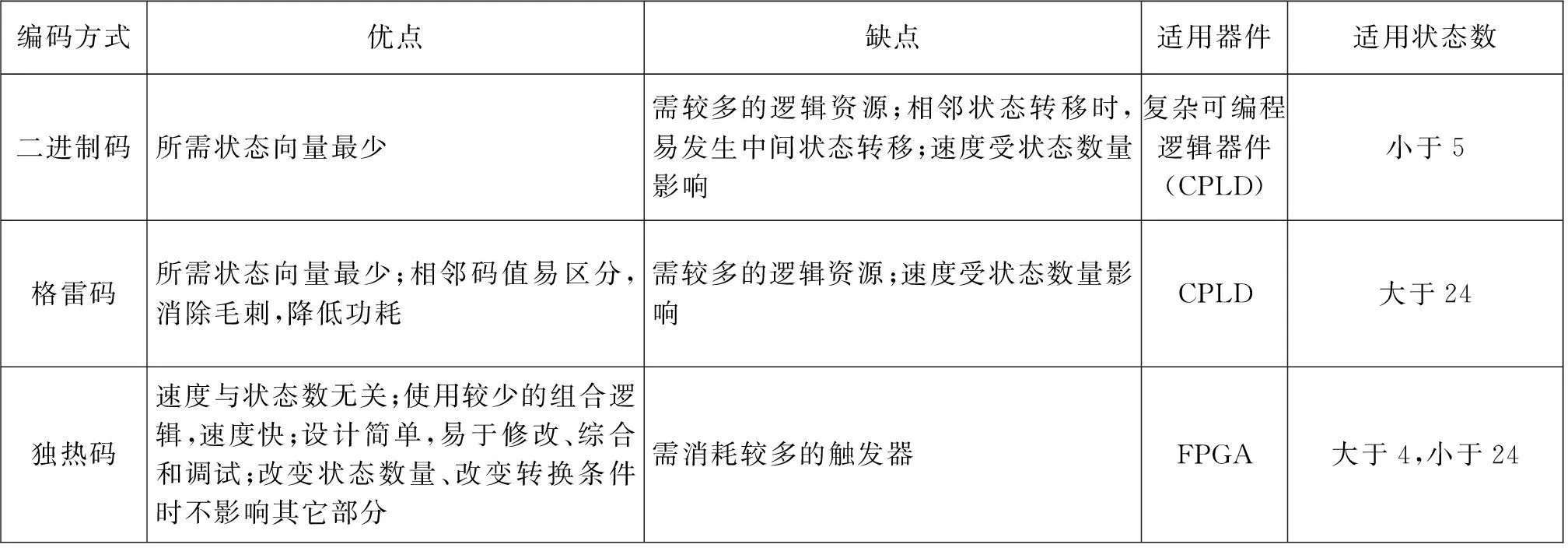

编码方式是状态机的重要组成部分之一,根据设计需要选择最适合的编码方式,能够满足状态机的评判标准,使设计效果最佳。常用的编码方式主要有3种[6]:二进制码、格雷码、独热码。表1是3种编码方式的优缺点、适用器件以及适用状态数。

表1 3种编码方式的优缺点、适用器件以及适用状态数

由于本设计中的控制状态机有6种状态,硬件平台选用的是FPGA器件,再根据设计的具体细节要求,对比表1的3种编码方式,选用独热码进行编码。

1.4 FSM的3种描述风格

通常,最常用的FSM有3种描述风格[1]:One-Always(一段式FSM描述风格)、Two-Always(两段式FSM描述风格)、Three-Always(三段式FSM描述风格)。

One-Always由1个Always模块组成,即将整个状态机写到1个Always模块里,该模块里包含了输入、输出以及转移状态;Two-Always由2个Always模块组成,其中一个Always模块用来描述状态转移,另一个Always模块用来描述状态转移的条件和状态转移的规律;Three-Always包含了3个Always模块,其中一个Always模块描述状态转移,第2个Always模块描述状态转移的条件和状态转移的规律,第3个Always模块则通过使用同步时序电路描述状态的输出。

表2是3种描述方式的优缺点。

表2 3种描述风格的优缺点

2控制系统的有限状态机设计与仿真验证

2.1 控制系统的有限状态机设计

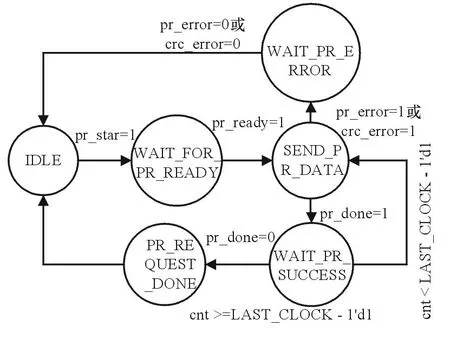

本设计描述的是局部动态可重构中的控制模块,该控制模块的主体是FSM,主要对可重构的过程进行监测。该状态机有6个工作状态,分别是:IDLE(闲置状态)、WAIT_FOR_PR_READY(重构准备状态)、SEND_PR_DATA(传送数据状态)、WAIT_PR_SUCCESS(重构成功状态)、WAIT_PR_ERROR(重构失败状态)、PR_REQUEST_DONE(重构结束状态)。其状态流程图如图1所示。

图1 控制系统状态流程图

该FSM工作过程:系统正常工作时,状态机处于闲置状态(IDLE),当接收到重构开始信号“pr_start=1”时,则进入重构准备状态(WAIT_FOR_PR_READY),并对外输出重构请求信号“pr_request”。当接收到外部应答信号“pr_ready=1”,则判定系统完成锁定,进入传送数据状态(SEND_PR_DATA)。在该状态,存储器开始按照地址向动态模块传送.rbf文件,对动态模块进行重新配置。如果接收到“pr_done=1”信号,表明配置成功,则系统进入WAIT_PR_SUCCESS(重构成功状态),并通过cnt< LAST_CLOCK-1'd1判断重构是否全部完成。若cnt< LAST_CLOCK-1'd1,满足条件,表示重构全部完成,此时系统进入PR_REQUEST_DONE(重构结束状态),在该状态,表明重构结束,系统进入IDLE。若cnt< LAST_CLOCK-1'd1,不满足条件,则系统返回数据传输状态,继续传送数据,每传送一次,计数变量cnt和外部存储器地址都加1。如果接收到“pr_error=1”或“crc_error=1”信号,表明此次配置不成功,系统进入WAIT_PR_ERROR(重构失败状态)。在WAIT_PR_ERROR(重构失败状态)状态,接收到“pr_error=0”或“crc_error=0”信号,系统回到等待状态。

2.2 3种描述风格的FSM

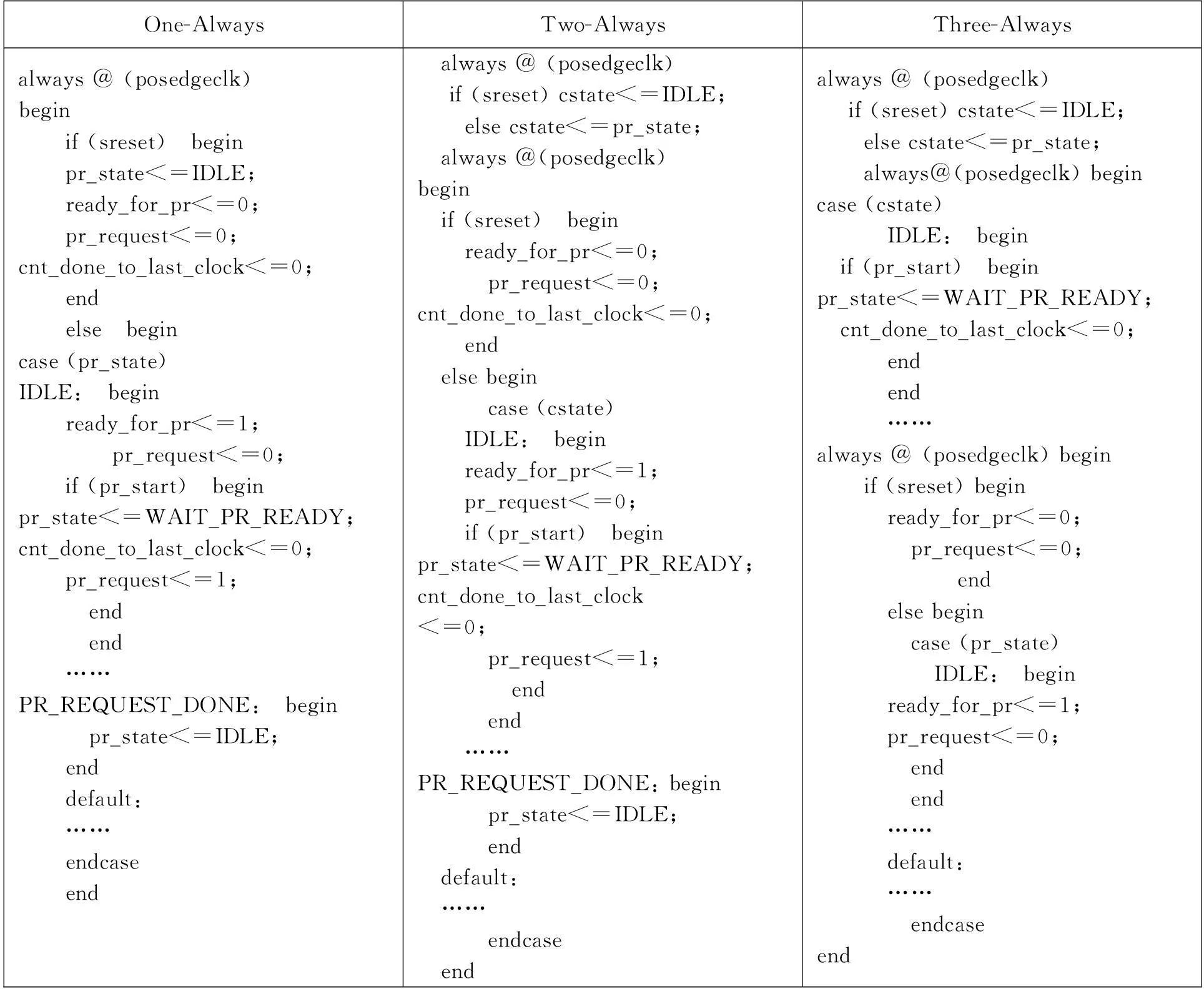

下面是用3种不同的描述风格对该控制模块状态机进行描述,其部分关键代码如表3所示。

2.3 仿真验证与比较分析

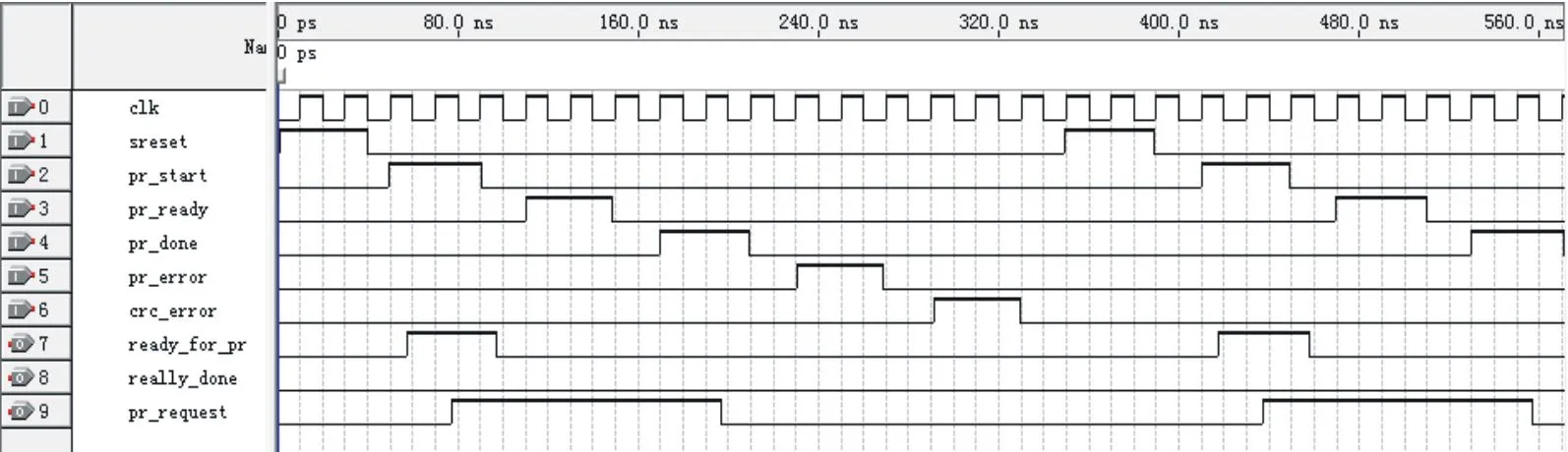

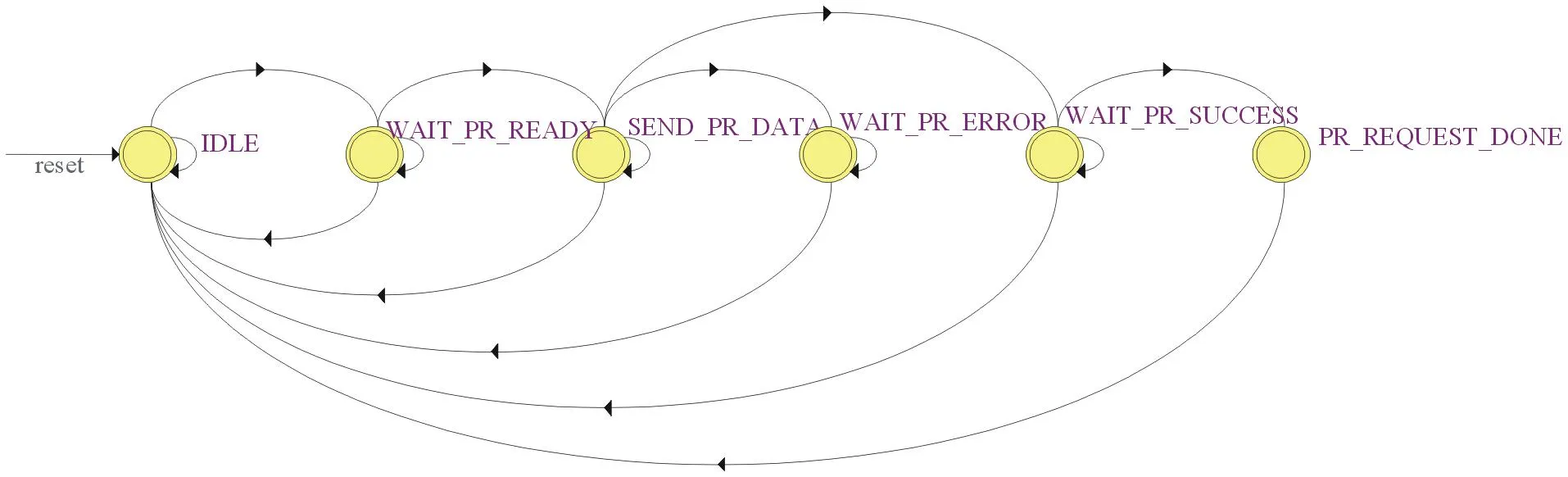

利用功能强大的QuartusII软件对以上3种描述风格的FSM进行综合、编译、时序仿真后,得到其时序仿真图如图2所示。并选择任一种描述风格(如One-Always)生成其状态机,如图3所示。从时序仿真图和状态机可观察出,设计符合要求。

图2 时序仿真结果

图3 控制系统的FSM

One-AlwaysTwo-AlwaysThree-Alwaysalways@(posedgeclk)beginif(sreset) beginpr_state<=IDLE;ready_for_pr<=0;pr_request<=0;cnt_done_to_last_clock<=0;endelse begincase(pr_state)IDLE: beginready_for_pr<=1; pr_request<=0;if(pr_start) beginpr_state<=WAIT_PR_READY;cnt_done_to_last_clock<=0;pr_request<=1; end end……PR_REQUEST_DONE: begin pr_state<=IDLE;enddefault:……endcaseend always@(posedgeclk) if(sreset)cstate<=IDLE; elsecstate<=pr_state; always@(posedgeclk)begin if(sreset) begin ready_for_pr<=0; pr_request<=0;cnt_done_to_last_clock<=0;end elsebegin case(cstate)IDLE: beginready_for_pr<=1;pr_request<=0;if(pr_start) beginpr_state<=WAIT_PR_READY;cnt_done_to_last_clock<=0; pr_request<=1; end end ……PR_REQUEST_DONE:begin pr_state<=IDLE; end default: …… endcase endalways@(posedgeclk) if(sreset)cstate<=IDLE;elsecstate<=pr_state;always@(posedgeclk)begincase(cstate) IDLE: begin if(pr_start) beginpr_state<=WAIT_PR_READY; cnt_done_to_last_clock<=0; end end ……always@(posedgeclk)beginif(sreset)begin ready_for_pr<=0; pr_request<=0; end elsebegin case(pr_state) IDLE: begin ready_for_pr<=1; pr_request<=0; end end …… default: …… endcaseend

对3种不同描述风格的FSM进行综合、编译、布局布线后,可以生成各自的寄存器传输级视图(RTL Viewer)。对它们进行对比,One-Always风格的有限状态机的RTL Viewer相对比较简单,但其状态、输入以及输出都放在了一个模块中,当前状态可能会受到其它状态的影响;Two-Always风格有限状态机的RTL Viewer比较复杂,它是在One-Always的基础上增加了一个状态(cstate),把转移状态和转移条件放在2个Always模块中描述,使RTL Viewer清晰易读;Three-Always风格的有限状态机的RTL Viewer 最复杂,其与Two-Always的最大不同在于能够根据下一状态的判断,把FSM的输出寄存在同步时序逻辑中,可有效消除毛刺。

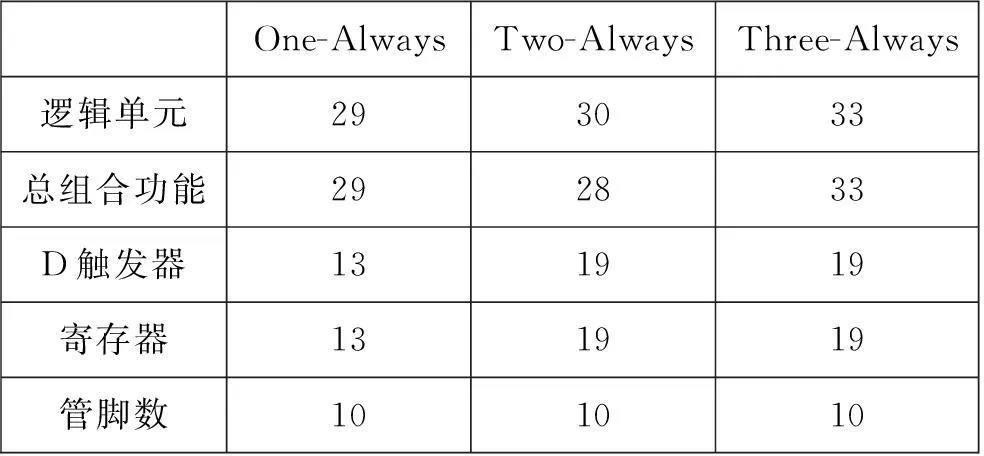

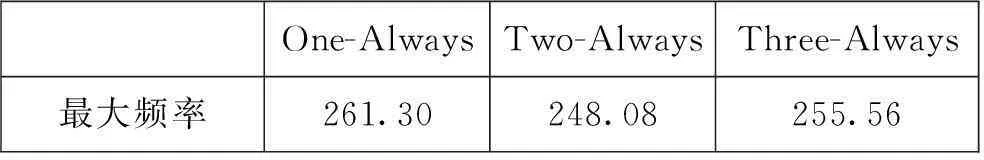

根据综合、编译得出的编译报告对3种不同描述风格FSM的资源消耗(即面积)和最大频率(即速度)进行对比,分别如表4、表5所示。

表4 3种描述风格消耗资源对比(单位:个)

表5 3种描述风格的最大频率对比单位:MHz

从表4、表5可看出,在3种描述方式中,One-Always消耗资源最少,速度最快;Two-Always消耗资源较多,速度最慢;Three-Always消耗资源最多,速度较快。

综上,如果仅从资源消耗以及RTL Viewer复杂程度来考虑,选用One-Always的描述风格最佳。但是,One-Always将同步转移、输出和输入条件都混写在1个Always模块中,这与时序与组合逻辑分开的Coding Style(代码风格)不相符,整个描述代码不清晰,后期维护和修改也比较困难,不利于综合和布局布线对设计本身的优化以及时序约束,且容易产生状态锁存(Latches),影响FSM的安全稳定性,因此,一般不推荐使用这种描述风格来描述FSM。

Two-Always把同步时序与组合逻辑分别写到2个不同的Always模块中,能在一定程度上克服One-Always的不足,但是这种组合逻辑输出可能会产生毛刺,不仅会影响约束、综合和布局布线,还可能影响状态机的安全稳定性。

但其资源消耗比Three-Always少,且RTL Viewer复杂程度比Three-Always的低,可以在FSM的组合逻辑输出端插入1个额外的节拍(Latency),使输出寄存1个节拍,消除毛刺,此时插入节拍的Two-Always为最佳的描述方式。

与Two-Always相比,Three-Always的最大好处在于状态机的输出使用了同步时序逻辑寄存,有效消除了毛刺,但是 Three-Always资源消耗最多,输入到输出比One-Always和Two-Always会延时1个周期,在Two-Always不允许插入额外节拍的情况下,使用该描述方式。

3结束语

FSM是动态可重构技术中控制系统的主要组成部分,其设计技术是数字系统中实现高效率、高可靠性逻辑控制的重要途径[7]。在使用Verilog HDL语言描述有限状态机时,应根据评判标准优先保证其安全稳定性,继而在考虑速度、面积和复杂程度之后,再根据具体的实际需要选择合适的编码方式和描述风格,使设计更优。本文用3种不同的描述风格设计了控制系统的FSM,并依据评判标准的4个方面进行了比较,得到了最优的描述风格。

参考文献

[1]刘小平,何云斌,董怀国.基于Verilog HDL的有限状态机设计与描述[J].计算机工程与设计,2008,29(4):958-960.

[2]李云,冯永浩,孟涛.基于VHDL有限状态机控制器的设计方法[J].微计算机信息,2010,26(5):74-75.

[3]樊辉娜.基于状态机的8路彩灯VHDL设计[J].制造业自动化,2011,33(1):176-179.

[4]方洪浩,雷蕾,常何民.基于Verilog HDL的有限状态机设计[J].科学技术与工程,2007,20(7):5276- 5281.

[5]张继森,杨恢东,黄波,等.基于Verilog HDL的DDS信号发生器的设计与实现[J].微电子学,2012,42(6):819-822.

[6]孔听,吴武臣,侯立刚,等.基于Verilog的有限状态机设计与优化[J].微电子学与计算机,2010,27(2):180- 183.

[7]吴春波,苏厚勤.基于有限状态机模型的GUI设计及其应用[J].计算机应用与软件,2010,27(11):141- 144.

Design and Implementation of Control System Based on FSM

FENG Kun,LI Yue-hua,ZHANG Jin-lin,LI Jia-wei

(Air Force Early WarningAcademy,Wuhan 430019,China)

Abstract:This paper introduces the basic description mode,evaluation criteria,coding mode and description style of finite state machine(FSM),and compares the advantages and disadvantages of different coding modes and description styles,taking FSM of control system in the local dynamic reconfiguration process as an example,realizes three FSMs of different description styles by using Verilog HDL,and compares the security stability,RTL Viewer,resource consumption and speed of the three different FSMs,obtains the optimal FSM description style.

Key words:finite state machine;description style;coding mode

基金项目:青年创新基金,项目编号:2013QNCX0112

收稿日期:2015-05-19

DOI:10.16426/j.cnki.jcdzdk.2015.05.021

中图分类号:TP332.3

文献标识码:A

文章编号:CN32-1413(2015)05-0094-05