多参数数据记录器设计与实现

杜文略 ,张亮红 ,沈三民 ,刘文怡

(1.中北大学 仪器科学与动态测试教育部重点实验室,太原 030051;2.中北大学 电子测试技术重点实验室,太原 030051)

在航空航天领域,遥测系统是航天测控通信系统的重要分系统。遥测系统担负着“近测远传”的任务,即在弹箭、飞船、卫星等飞行器上安装仪器,就近测量飞行器的相关参数,并通过传输媒介将参数传递到地面接收站。飞行器的测量参数包括模拟量参数、数字量参数、开关量参数,这3类参数统称为遥测参数。对于验证飞行器的设计参数、故障诊断、故障隔离以及飞行器遥控调姿等功能的实现,遥测数据提供了重要的参考依据。

本设计来源于某飞行器“遥测数据存储设备研制”项目,通过对多路遥测系统参数采集、传输、混合编码、存储等关键技术的研究,设计出一种能够同步采集3路冲击信号、1路RS-422 PCM信号以及1路LVDS高速图像信号的数据记录器。本数据记录器的设计原理、设计过程及测试结果对相关设计具有一定参考意义[1]。

1 系统的总体结构

数据记录器由电源板和主控板组成,其结构框图如图1所示。其中,+28 V由外部系统提供,电源板将28 V电压滤波后转换成5 V电压提供给主控板;主控板负责具体的参数采集、编码和存储任务。

图1 系统总体结构Fig.1 Overall structure of the system

主控板以FPGA为控制核心,接收LVDS接口传输的LVDS图像数据、RS232传输过来的码同步信号和PCM数据、AD转换后的3路冲击信号以及启动信号、地面命令等数据,再将数据在FPGA内编码后存入NAND Flash芯片,同时可以将测试数据通过LVDS传输接口传输到上位机进行分析[2]。

2 系统硬件设计

2.1 3路冲击信号采集电路设计

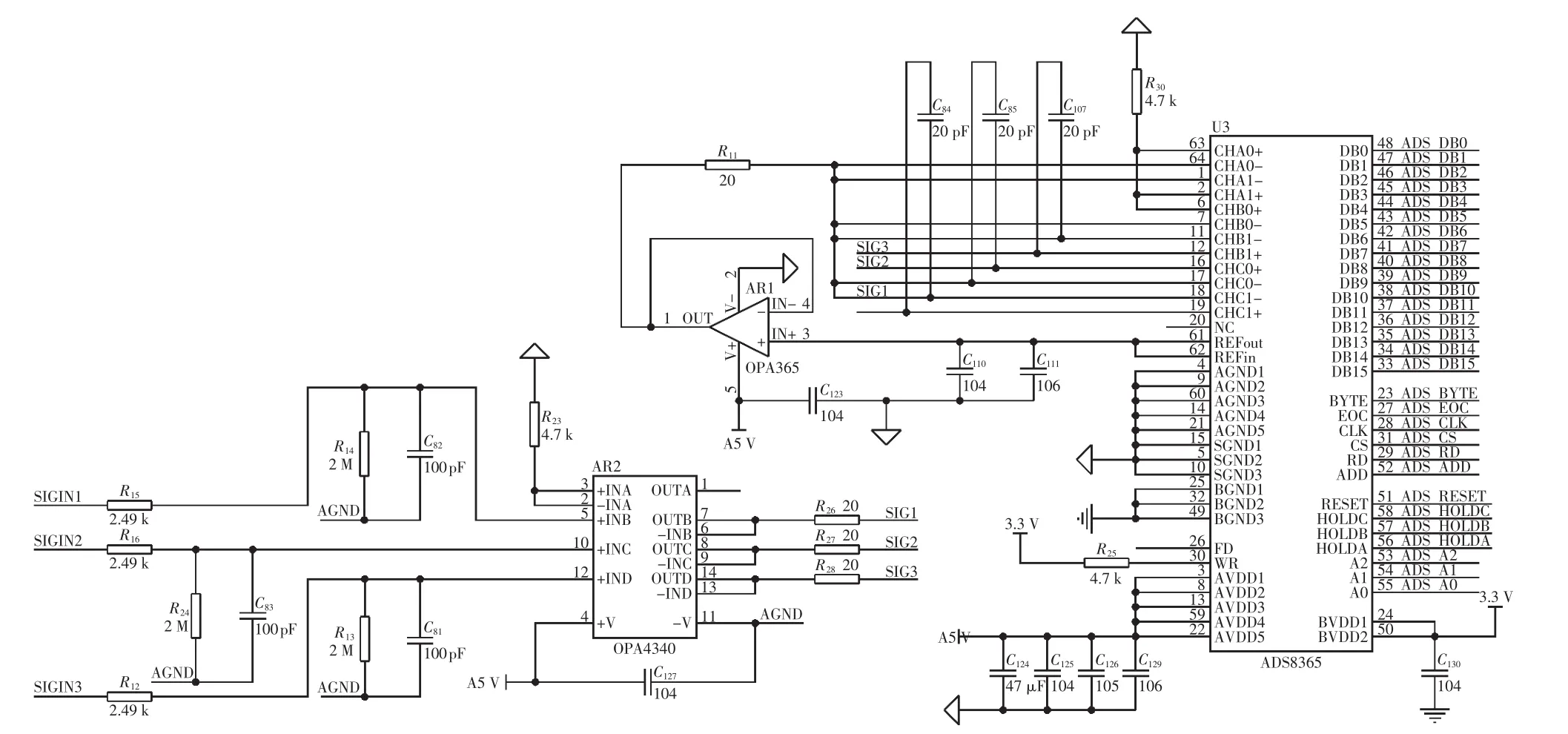

3路冲击信号为0~5 V的模拟量电压信号,所以要经过调理及AD采集电路将其转换为数字信号传输给FPGA。要求单路采样率不小于40 Hz,采样精度16位。本设计选用TI公司的16位模数转换芯片ADS8365,它采用单端+5 V供电、6通道同步采样、差分输入,具有高性能、低功耗等特点,当参考时钟最高为5 MHz时,该芯片的转换时间为3.2 μs,此时的采样率为最高的250 kHz,完全满足设计要求。ADS8365的应用电路如图2所示。

图2 AD8365采集电路Fig.2 AD8365 acquisition circuit

ADS8365的模拟信号输入端有2种驱动方式:单端输入和差分输入。冲击信号由OPA4340跟随调理后,电压范围仍为0~5 V,为简化电路设计,冲击信号采用单端输入方式。选用CHB1、CHC0和CHC1这3对管脚作为冲击信号的输入端,此时每对管脚负端输入电压 (VCHX-)等于共模电压(VCM)。 输出参考电压 REFOUT(Pin61)与输入参考电压 REFIN(Pin62)短接,设置输入端参考电压为VREF=+2.5 V,此时CHX+的电压输入范围为-VREF+VCM~+VREF+VCM[3]。

2.2 PCM接收电路设计

数据记录器接收地面测试设备发送的1路PCM数据,传输方式为RS-422差分同步传输。DS26C32是低功耗CMOS器件,具有噪声容限宽、静态功耗小等特点。在实际电路设计中要注意2个问题:(1)考虑终端阻抗匹配。传输线的源端和终端阻抗不匹配会产生反射,引发信号震荡、阶梯效应等问题,影响信号传输效果。数据记录器与地面测试设备之间的传输介质为6类双绞线,根据其阻抗特性,在接收端选用100 Ω电阻作为终端匹配电阻,并以并联方式接入电路;(2)不用的输入管脚要接地。DS26C32是CMOS器件,而CMOS器件是电压控制器件,输入阻抗高,悬空的管脚易受外界噪声干扰造成器件逻辑错误或者栅极感应静电击穿损坏器件。在本设计中,DS26C32的不用的差分输入管脚通过一个4.7 k下拉电阻接地。PCM码流接收电路如图3所示[4]。

图3 PCM数据接收电路Fig.3 PCM data receiving circuit

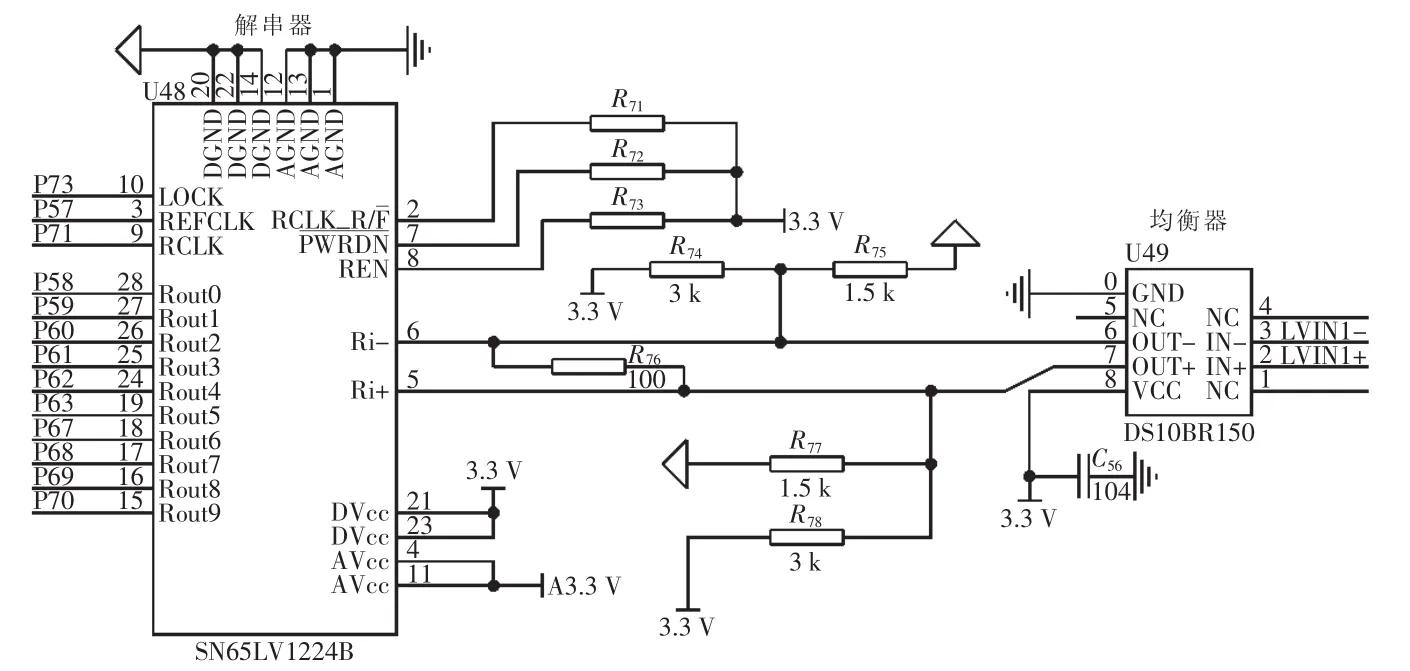

2.3 图像接收模块电路设计

LVDS传输接口采用低压差分信号进行传输,具有抗干扰能力强、传输速度快等优点。根据技术参数要求,数据记录器采用LVDS解串器SN65LV1224B来进行LVDS图像数据的接收。SN65LV1224B是一个并行总线10位的LVDS解串器,系统时钟范围10 MHz~66 MHz,兼容 DS92LV1023。 设计使用均衡器DS10BR150来改善这些情况。

DS10BR150是TI公司推出的一款单通道、高速LVDS均衡器,输入兼容LVDS、CML和LVPECL 3种逻辑电平,输出为LVDS电平,芯片内置了1个100 Ω终端电阻,降低输入输出的回波损耗,同时也减小了布板空间。LVDS图像数据接收电路如图4所示。

图4 LVDS图像数据接收电路Fig.4 LVDS image data receiving circuit

2.4 存储模块电路设计

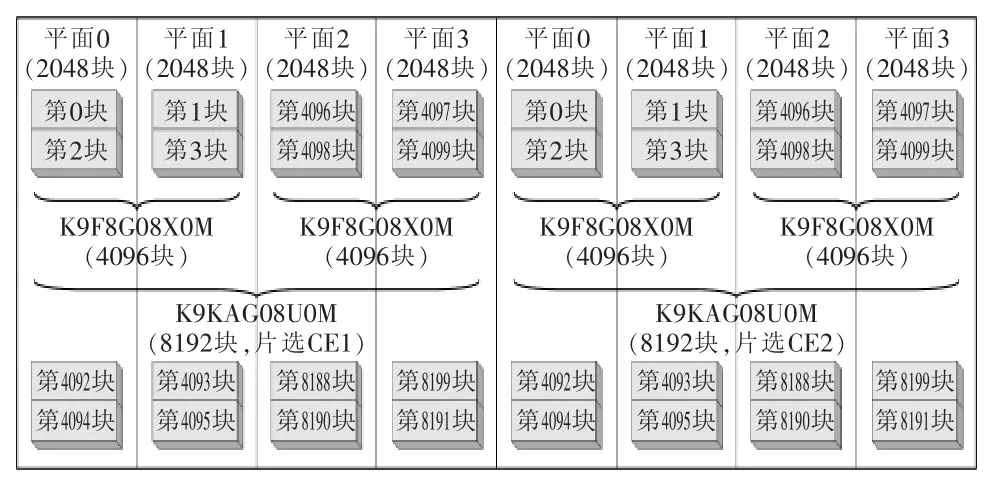

设计选用SAMSUNG公司推出的4 GB NAND Flash存储芯片K9WBG08U1M。K9WBG08U1M存储空间为4 GB,内部由2片完全相同的存储阵列K9KAG08U0M组成,每片2 GB,片选通过片选信号CE1和CE2选定。每片由8192块组成,每块包含64页,每页存储空间为4 KB+128 B,其中4 KB用来存放数据,128 B用于存放坏块标志、ECC码等状态信息。

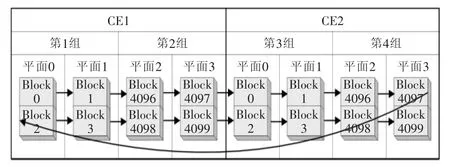

在该存储芯片内部,块是按照一定的规律排列的。块地址映射如图5所示,从图中可以看出,存储芯片中2片K9KAG08U0M具有相同的块地址映射,因此对这2片K9KAG08U0M中的块寻址还要使能片选信号CE1或CE2。每一片K9KAG08U0M中有8192个块,这8192个块按照地址被分为4个平面(Plane),每个平面有2048个块,这4个平面又被分为2个组,第0平面和第1平面为一组,第2平面和第3平面为另一组,每个组包括4096个块[5]。

图5 K9WBG0U1M块地址映射Fig.5 K9WBG0U1M block address mapping

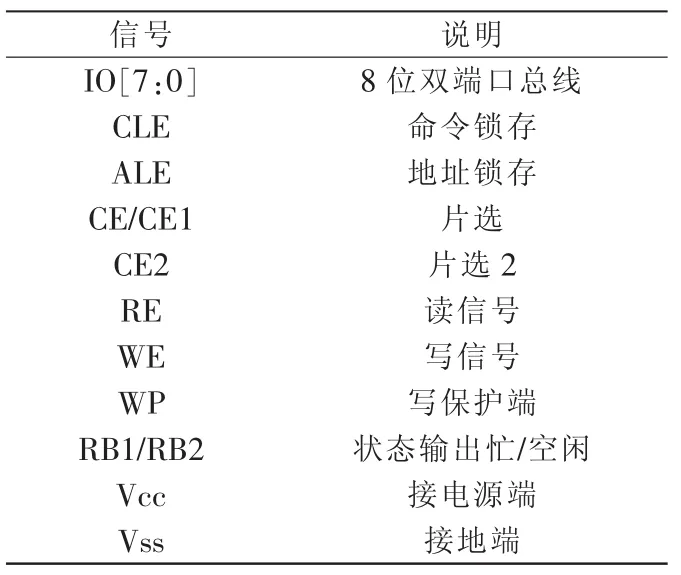

表1是存储芯片的管脚定义,其中I/O 0~I/O 7为命令总线、地址总线和数据总线复用端口,当对芯片进行操作时,需要FPGA设置CLE或ALE信号,才能让Flash正确识别I/O端口数据属性。K9KAG08U0M容量为2 GB,寻址空间为13位列地址×19位行地址。列寻址可以确定字节位置,行寻址可以确定页位置,这个寻址方式可以确定一个字节在整个存储空间的位置。向Flash写入地址需要2个写循环,写入行地址需要3个写循环,无论是写入列地址还是行地址,在最后一个写循环,有效地址位数总不够8位,无效的地址位必须为低电平。

表1 K9WBG08U1M引脚功能表Tab.1 K9WBG08U1M pin function table

记录器的存储区容量为8 GB,要使用2片K9WBG08U1M存储芯片。为了节约FPGA管脚资源以及紧凑化设计,设计选用2片4 G存储芯片串行扩展为8 G存储器,扩展结构示意如图6所示。在一片K9WBG08U1M连接到FPGA的基础上,另一片K9WBG08U1M只把2个片选信号连接到FPGA,其他信号与第一片共用。

图6 存储容量扩展示意Fig.6 Expansion of storage capacity

3 系统软件逻辑设计

3.1 模数转换逻辑设计

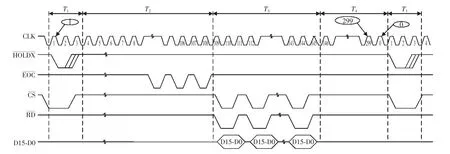

ADS8365有 6个模拟信号输入通道,分为CH A、CH B和CH C 3组,每组各有1个控制信号HOLDA、HOLDB及HOLDC,控制信号置高时启动对应组模数转换。模数转化值输出有Address模式、Cycle模式和FIFO模式3种,A2 A1 A0是模式控制管脚。设计采用Cycle输出模式,即A2 A1 A0=110,此时芯片循环把CH A0到CH C1通道的模数转换值放到输出寄存器中以供外部FPGA逻辑读取。需要注意的是,尽管模拟输入只占用了3个模拟通道,由于采用Cycle模式,每个循环FPGA逻辑仍需要依次读取每个通道的模数转换值。模数转化时序如图7所示。

图7 AD转换时序Fig.7 AD conversion timing diagram

在T1时间里,将HOLDX和CS信号拉低,开始本次数模转换;T2为数模转换时间,在T2末期EOC信号出现了3个低电平,表示全部数模转换完成;外部逻辑在T3时间里,按照Cycle模式要求,在读时钟下降沿依次读取6个通道的电压值;在T4时间里,对采集到的数据进行编码,并存入FIFO中。

3.2 图像接收逻辑设计

接收的单幅图像数据帧格式为320×512,帧速率20 ms/帧,帧数量不大于500帧,SN65LV1224B的同步时钟为12 MHz,并行10位输出,图像数据接收时序如图8所示。由帧格式可知,20 ms产生一帧图像数据,大小为160 KB,LVDS接口传输160 KB的数据需要时间为16.38 ms,这表明图像数据不能在整个传输过程中一直保持满负荷传输状态。而在使用LVDS接口进行数据传输时,需要实时进行数据同步,因此LVDS数据发送端在图像数据传输的间隙填充了无效数据(0100000000),以满足对数据同步的要求。

图8 图像数据接收时序Fig.8 Time sequence of image data

LVDS图像数据传输的约定为SN65LV1224B输出的高2位表示状态信息,低8位是数据。当状态信息是01、10或者11时,表示当前接收到的是有效图像数据,并存入对应的FIFO中,如果是00,表示当前接收到的是无效数据,不予处理。

3.3 片外流水线存储逻辑设计

K9WBG08U1M有4种页编程方法:单平面页编程、交错单平面页编程、双平面页编程和交错双平面页编程技术。其中交错双平面的页编程速度最快,理论值达到14.8 MB/s,为提高速率一般采用并行和流水线2种技术。并行技术实现了记录速度提升,但是增加了不必要的存储空间和主控芯片的I/O资源,同时也相应增大记录器体积。因此本设计使用片外流水线存储技术,利用片选CE信号增加一级流水,实现写入速度的提高。

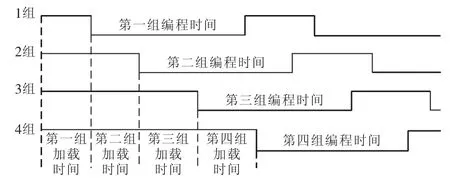

片外流水页编程方式时序和流程分别如图9和图10所示。存储芯片的8个平面分成4个组,当第一组完成数据的加载,进行编程操作时,开始加载第二组数据,以此类推,完成4组数据的加载。后续3个组的加载时间填补了第一组的编程时间,从而提高了写入速度。

图9 片外级流水数据时序Fig.9 Time sequence diagram of the off stage flow data

图10 片外级流水数据流程Fig.10 Flow chart of the outer stage flow

4 系统试验结果与分析

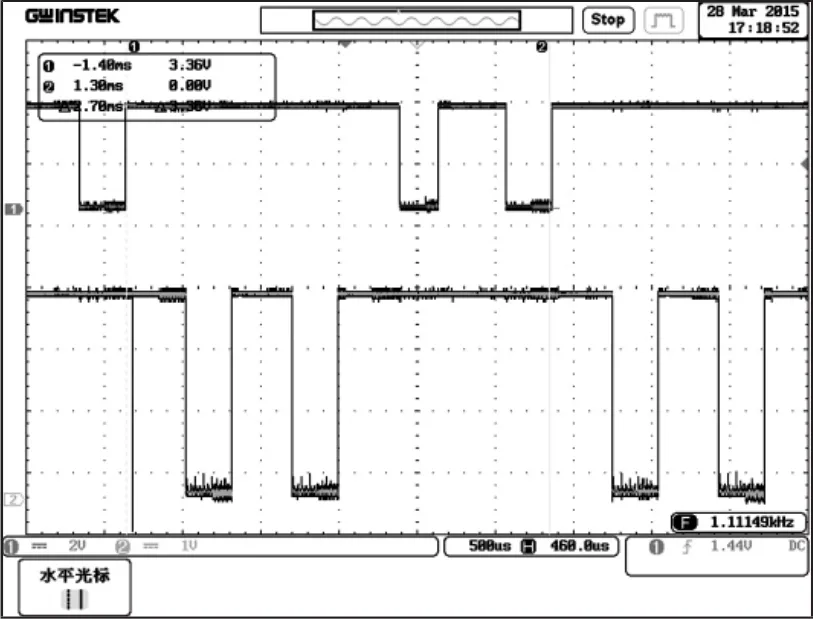

图11 CE信号Fig.11 CE signal

图11中信号为CE1信号,低电平宽度表示CE1片选时间tCE1=1.35 ms,由于片选信号在CE1和CE2之间切换,所以高电平时间表示CE2片选时间tCE2=1.35 ms。从片选信号时间角度,一个页编程循环时间为tWCof 8 pages=tCE1+tCE2=2.7 ms。图12中上方为RB1信号,下方为RB2信号,以RB1为参考对象,RB1的一个周期代表一个页编程循环时间,图中用已经标出一个RB1的周期tRB1of cycle=2.7 ms,因此tWCof 8 pages=tRB1of cycle。从而验证了流水线存储技术的正确性。

图12 RB1/RB2信号Fig.12 RB1/RB2 signal

5 结语

针对某飞行器遥测系统需求,设计了一种基于NAND Flash的弹载高速大容量数据记录器。根据技术指标要求,提出了数据记录器的总体设计方案。数据记录器以XC3S1400AN作为逻辑控制中心、K9WBG08U1M作为存储芯片,接收上位机命令,采集3路冲击信号、1路RS-422 PCM码流、1路LVDS图像数据,二次编帧后存入8 GB NAND Flash中,最高存储速度可达19 MB/s,记录完毕后,通过LVDS接口将数据回传给上位机。重点介绍了数据记录器的硬件电路设计、FPGA控制逻辑设计、片外2级流水交错双平面技术及FPGA时序验证技术。该数据记录器已成功应用于某航天遥测系统中。

[1]马志刚,刘文怡,凌伟.基于PCI和LVDS的高速数据存储系统的设计[J].电子技术应用,2014,40(4):80-84.

[2]丁海飞.基于双平面技术的固态存储器的设计与实现[D].太原:中北大学,2012.

[3]范旭东,沈三民,刘建梁,等.基于LVDS和68013A的数据控制传输系统设计[J].计算机测量与控制,2014,22(6):1950-1953.

[4]S Gregori,A Cabrini,O Khourietal.On-chip correction techniques for new-generationflash memories[J].Proc.of IEEE,2003,91(4):602-616.

[5] 李进,金龙旭,李国宁,等.ECC嵌入BCH码的NAND闪存纠错算法[J].哈尔滨工程大学学报,2012,33(11):83-88.