DDR3仲裁控制器设计及FPGA验证

尹春梅,陈 钱,顾国华,隋修宝

(南京理工大学 电子工程与光电技术学院,江苏 南京210094)

0 引 言

在高速CCD 的成像系统中,一些复杂算法会用到外部存储器[1],当前所用的外部存储器都是RAM 或者SDRAM[2,3],但是RAM 和SDRAM 具有以下两个缺陷使其无法满足高速CCD 系统的设计要求:①最主要的一个缺陷是,RAM 和SDRAM 体积大,一片RAM 或者SDRAM又只能给一个算法使用[4],当高速CCD 成像系统中有多个算法需要用到外部存储器时就要在硬件设计中加入多个RAM 或者SDRAM,这样需求的FPGA 的引脚数量增多,增加了系统的功耗和硬件消耗,难以缩小体积,无法满足CCD 的小型化要求;②RAM 和SDRAM 数据存储速度慢,最高工作频率仅143 M[5],不仅无法满足高速CCD 数据存储要求,还无法采用时分复用的方法使多个算法共用一片外部存储器。基于以上RAM 或者SDRAM 使用的局限,本文在高速CCD 系统设计中用DDR3 作为外部存储器。DDR3做外部存储器具有以下两点优势:①DDR3数据存储速度快,最高工作频率可以达到400 兆[6];②体积小,功耗低[7]。然而,和RAM 还有SDRAM 类似,一片DDR3只能给一个算法使用,当多个算法需要用到DDR3时,在硬件电路设计中依旧需要用到多个DDR3,不利于小型化的设计。基于DDR3数据存储速度高达400兆,但是CCD内部数据流不超过100兆,本文提出了一种用于高速CCD数据存储的DDR3 仲裁控制器,采用时分复用的方式[8],用仲裁的形式操作DDR3,使多个算法只需要一片DDR3就能实现数据流读取,这样既能充分利用DDR3高速的优势,又能极大减少设计空间,便于满足CCD 的小型化要求[9,10]。

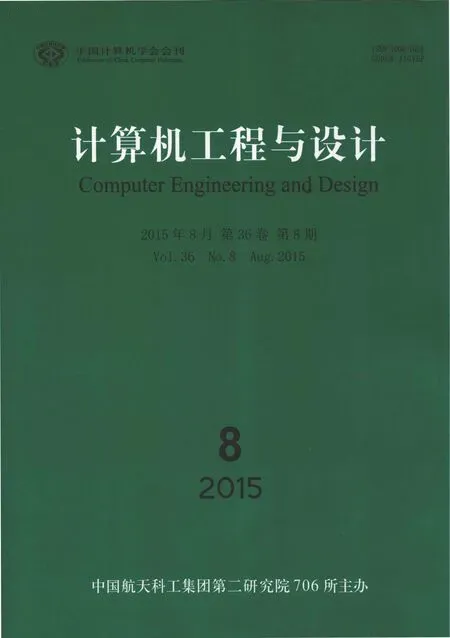

1 DDR3SDRAM 仲裁控制器系统构成

本文提出的DDR3仲裁控制器结构如图1 所示,主要由读写控制模块、DDR3 仲裁模块、IP 核控制器、数据格式装换模块、DDR3 芯片构成。前端算法模块将要写往DDR3的数据和对应的地址,以及要读出数据对应的地址写到读写控制模块中,读写控制模块根据阈值条件决定是否将这3个信号以及读写控制信号给后续仲裁模块,由仲裁模块决定是否将这3个信号给IP核控制器。当仲裁模块决定将这3个信号给IP核控制器时,IP核控制器才将这3个信号传输给DDR3芯片。要存入DDR3的写数据就写进了DDR3中对应的写地址。读地址对应的DDR3中的数据从DDR3芯片传回DDR3控制器IP核,IP核将读出的数据和读数据使能传输给读写控制模块,由读写控制模块输出给数据格式转换模块,经过数据格式转换后输出给后续电路使用。

图1 DDR3SDRAM 仲裁控制器系统结构

(1)读写控制模块:对前端的数据流进行缓冲,解决了前端数据流的传输速度比DDR3的写数据速度慢的问题,从而确保数据能够正确的写入DDR3。

(2)DDR3 仲裁模块:当多个数据流同时申请使用DDR3时,对这些数据流使用DDR3的先后顺序进行判断,根据判断结果分配读写存储模块的使用资源。

(3)数据格式转换模块:根据从DDR3中读出的数据和对应帧信号将数据转化为后续电路所需的标准格式,从而解决因数据写入DDR3再读出,导致数据格式发生改变后无法满足后续电路所需的数据格式的问题。

(4)IP核控制器:对外的输出接口通过FPGA 的引脚分配直接和外部电路相连接,主要负责DDR3正确的读写数据。

(5)算法模块:CCD 系统中的一些图像处理算法需要缓存一帧或者两帧的图像,为了节约内部资源,缓存这些图像数据必需用到外部存储器。

下文将对上述模块进行详细分析。

2 读写控制模块设计

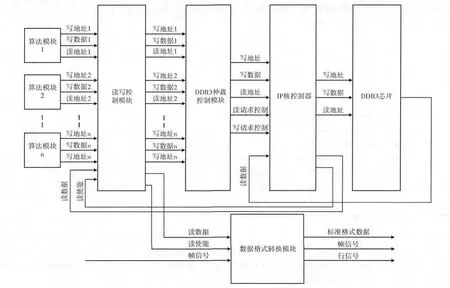

该模块的工作过程可分为读操作和写操作,工作流程如图2所示。

(1)读操作。当需要读DDR3某个存储器空间的数据之前,先将想读的数据在DDR3 中的地址存储进读地址FIFO,前端数据流在读控制信号的控制下,不停地将读地址写入读地址FIFO 中;当读地址FIFO 的存储器空间多于设定的高阈值,向DDR3 仲裁控制器申请开始对读地址FIFO 进行读操作,从DDR3中读取对应地址的数据写入到读数据FIFO 中。当读地址FIFO 的存储器空间少于设定的低阈值时,向DDR3仲裁控制器申请停止对读地址FIFO 的读操作;前端数据流会对已经写入读地址FIFO 内的地址个数计数,当快满一帧个数时,给出一个读帧结束信号rf_end (在倒数第二次读停止信号后,最后一次读停止信号之前给出高电平,最后一次读停止信号之后置零)到仲裁控制器,该信号屏蔽最后一次读地址FIFO 的读停止信号,使仲裁模块能够一直分别读取读地址FIFO 中的地址,直到其为空 (可将读地址FIFO 的empty信号接入到仲裁模块中监视其是否为空)。读数据FIFO 则为:如果读数据FIFO 数据超过设定的高阈值时,由前端算法连续读取读数据FIFO中的数据,并对其进行计数,当读取够一帧时停止读取。通过FIFO 的缓冲使帧间的消隐时间相同。

所有FIFO 在读写操作完成后需要清空。读地址FIFO,读数据FIFO 的高低阈值根据DDR3的读写速度来估算,阈值太高或者太低都会影响DDR3的读写效率。

图2 读写控制模块

(2)写操作。前端数据流不停地将欲写的地址和数据发送至写地址FIFO 和写数据FIFO;当两个FIFO 中数据个数超过设定的高阈值时,读写控制模块向仲裁模块发出写请求,将写数据FIFO 中的数据写入DDR3 中相对应地址,当写地址FIFO 数量低于设定的低阈值时向仲裁模块申请停止对写地址FIFO 和写数据FIFO 的读操作。在此同时,需要对已经写入写地址FIFO 内的地址个数计数,当快满一帧个数时,给出一个写帧结束信号wf_end (在倒数第二次读停止信号后,最后一次读停止信号之前给出高电平,最后一次读停止信号之后置零)到仲裁模块,该信号屏蔽最后一次读停止信号,使仲裁模块能够一直分别读取两个FIFO 中的地址和数据,直到两个FIFO 为空 (可将FIFO的empty信号接入到仲裁模块中监视FIFO 是否为空)时停止写操作。通过以上操作,来实现一整帧图像的地址和数据写入DDR3。和读操作类似,写操作的写地址FIFO 和写数据FIFO 的高低阈值要根据DDR3的读写速度来估算。

DDR3的IP核配置时可选择字节突发长度,一般为4,8或者不突发。IP 核接收的数据是64 位,恰巧是4 突发,因此把4的16位的数据合成一个64位的数据,否则就浪费了高48位。因此,本文提出的系统中,DDR3读写的图像数据一行的数据个数以及数据对应的地址个数只能是4的整数倍。但是前端给的图像数据格式是不定的,无法保证一行的数据个数就是4的整数倍。因此,本文在读写控制模块中加入了一个数据格式转换模块,包括地址格式转换模块、写数据格式转换模块、读数据格式转换模块。地址格式转换模块和写数据格式转换模块负责将输入数据连续的4个数据和对应4个地址转换为一个数据和一个地址,读数据格式转换模块是将一个数据转化为4 个地址连续的数据。

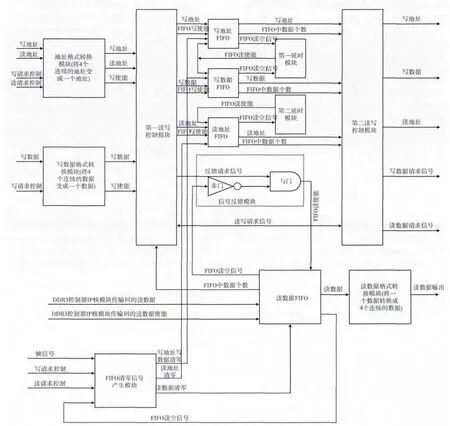

2.1 延时模块和信号反馈模块设计

一般情况下,图2读写控制模块中的写地址FIFO、写数据FIFO、读地址FIFO、读数据FIFO 中的数据是不允许读空的。所以如上文所述,本文提出用判断阈值的方法来决定是否继续读取FIFO 中的数据。但是有另一种情况,上述也提到了,当一帧数据快结束时,即便不满足阈值条件也需要将FIFO 中的数据读空。延时模块和信号反馈模块的作用就是判定FIFO 何时读空,等FIFO 读空的时候,标志FIFO 读空的信号就是高电平,经过延时模块和信号反馈模块的作用,给FIFO 使能端低电平,让FIFO 停止工作。图3为延时模块的结构。

图3 延时模块

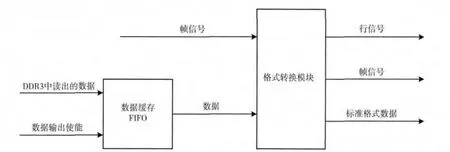

2.2 数据格式转换模块设计

在分析图2中读数据格式转换模块时已经提到,经过读数据格式转换模块转换后的图像数据一行的数据个数一定是4的整数倍,和后续电路所需的图像数据格式不一定相符合,结合图1,本文在读写控制模块中加入了一个数据格式转换模块,该模块功能主要是将DDR3中读出的图像数据转换为后续电路需要的图像数据格式。

数据格式转换模块如图4 所示,包括数据缓存FIFO、格式转换模块。当数据输出使能为高电平时,表示DDR3开始有数据读出,从DDR3读出的数据在数据缓存FIFO 模块中缓存3行,从FIFO 中读出的数据和前端数据流给的帧信号输入格式转换模块,最后输出后续模块所需的标准数据格式、行信号、帧信号。

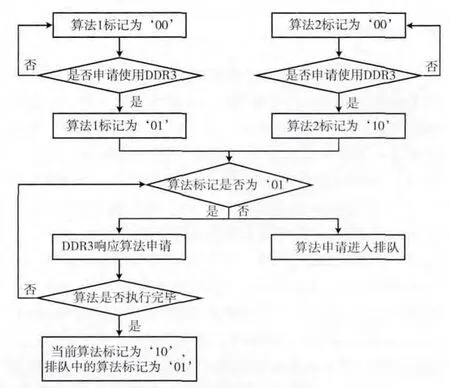

3 DDR3仲裁控制模块设计

图4 数据格式转换模块

实际工作中,在单一数据流申请的情况下,DDR3仲裁模块并没有发挥作用,只有当多个数据流申请时,仲裁模块才会起到仲裁作用。以两个算法申请为例,如图5所示,将算法1标记为 ‘01’,算法2 标记为 ‘10’,当两个算法都不申请时,当前状态标记为 ‘00’,当算法1申请时当前状态标记为 ‘01’,当算法1还未执行完时,此时如果算法2也申请使用DDR3,则此刻DDR3继续相应算法1的申请,而将算法2 排在申请队伍里。当算法1 执行完后,再将当前标记记为 ‘10’,执行算法2。如果当算法1和算法2 同时申请时,则根据顺序,DDR3先响应算法1的申请,执行完后再响应算法2的申请。

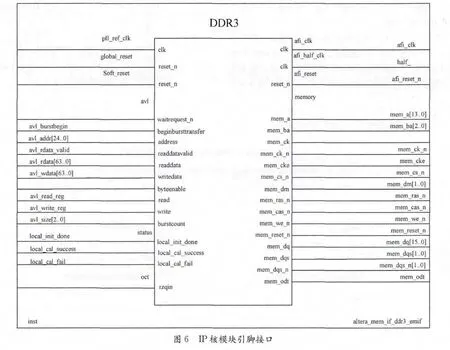

4 IP核控制器引脚接口配置

IP核控制器是由quartus生成软核如图6所示,部分特殊引脚定义如下:

(1)mem 开头的引脚是直接和DDR3芯片相连的,不需要配置。

(2)pll_ref_clk是IP核的参考时钟,有别于afi_clk和afi_half_clk,afi_clk和afi_half_clk是DDR3读出数据的时钟,用哪个时钟读出数据需要在生成IP核的时候设置。

(3)local_init_done、local_cal_success、local_cal_fail是DDR3初始化标志信号,当local_init_done、local_cal_success为高电平,local_cal_fail为低电平,则DDR3初始化成功,否则初始化不成功。

图5 仲裁模块工作流程

引脚配置好后,经实验调试发现,必需按照以下步骤编译才能通过。

(1)编译。当编译进行到Fitter(Place &Route)时报错。错误显示大量相同错误。

(2)运行自动分配引脚程序,Tools->Tcl Scripts->Pin assignment。

(3)再次编译。

图6 IP核模块引脚接口

5 实验验证

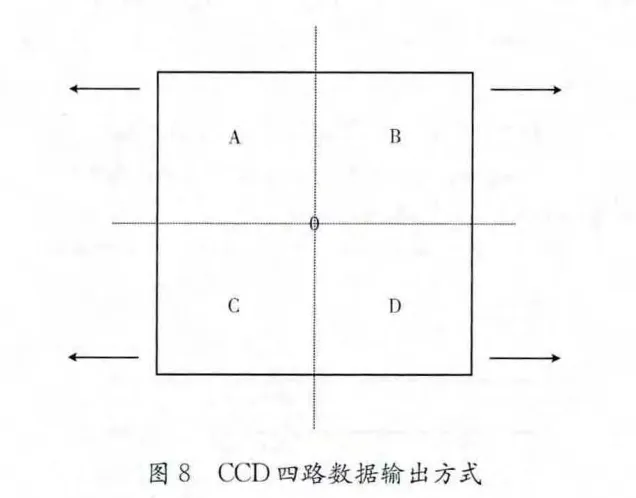

本文提出的DDR3 仲裁控制器已经实际应用于高速CCD 的数据存储。信号处理板的电路板如图7所示,图中虚线框就是两片DDR3芯片,其中一片是备用芯片,实际只用了一片。CCD 图像处理算法共有3 个算法共用一片DDR3,分别是图像拼接算法、帧间滤波算法、图像翻转算法。3个算法并不是直接操作DDR3,而是通过仲裁控制器分时占用DDR3。实现该仲裁控制器所用的软件是quartus 12.1,实现语言是VHDL,使用的FPGA 是Cyclone V,采用的DDR3芯片型号为MT41J128M16-15E,CCD 采用的数据格式如图9所示。以图像拼接算法和图像翻转算法为例:本文中CCD 选择了四路输出,即将图像分为四块输出,如图8所示,图中箭头表示数据的输出顺序,但系统的后续算法只能处理一整幅图像,因此需要用到图像拼接算法,将CCD 输出的四路数据拼成一路,又不丢失有效数据同时满足图9所示的数据格式。图像翻转算法是在图像拼接后续实现的功能,作用就是实现图像的上下左右翻转。图像拼接算法和图像上下翻转算法均需要缓存两帧图像,如果仅用片内RAM 则占用了大量的内部资源,会影响整个系统,所以两个算法都要将两帧图像缓存进DDR3。图10中的两幅图像均是完成图像拼接后显示的图像,左侧图像未开启图像翻转功能,整个系统中只有一个算法使用了DDR3,右侧图像开启了图像翻转功能,整个系统中有两个算法申请使用DDR3。

经实际应用证明,本文提出的DDR3仲裁控制器应用于高速CCD 数据存储速度最高能达到400M。以往用RAM作为高速CCD的外部存储器,最高能达到的数据存储速度只有100M。如果用传统的RAM 作为外部存储器,那么3个算法就需要用到3个片外RAM,加上一片备用RAM,在硬件电路设计中就需要设计四片RAM 而本文提到的CCD系统只用了一片DDR3,硬件设计也只设计了两片,加上DDR3的体积本身就要比RAM 小,极大的节约了设计空间,对高速CCD 的小型化设计有极为重要的意义。

图7 CCD 信号处理板

图10 图像拼接算法和图像翻转算法申请使用DDR3实际效果

6 结束语

本文提出了一种DDR3仲裁控制器的结构,已经很好地运用在高速CCD 系统设计中。其使得高速CCD 中用到的外部存储器可以摒弃传统的RAM 改用DDR3,实现了多个算法共用一片DDR3的仲裁模式,不用再拘泥于以往一个算法对应一片存储器的模式,CCD的数据存储速度上限也从100M 提升到400M。该结构只需要改动数据格式转换模块中的部分参数就可以适用于不同格式的CCD数据存储。

[1]Zhou Runjing,Ha Yuanyuan,Quick system-level DDR3signal integrity simulation research [J].Journal of Electronic Science and Technology,2013,11 (3),286-294.

[2]WANG Linlin,GUO Yong,YUAN Xing,et al.Design of DDR3controller based on H.264encoder[J].Video Engineering,2013,37 (23):89-92 (in Chinese). [王林林,郭勇,袁兴,等.基于H.264编码器的DDR3 控制器设计 [J],电视技术,2013,37 (23):89-92.]

[3]JIAN Yuhua,LI Junhui,XU Fei,et al.Data rearrangement design based on DDR3 [J].Fire Control Radar Technology,2013,42 (2):45-49 (in Chinese).[简育华,李军辉,徐飞,等.基于DDR3的数据重排设计 [J].火控雷达技术,2013,42 (2):45-49.]

[4]FANG Yong,LI Guoqiang,HU Yuehui.Design of DDR3 SDRAM controller based on Stratix III[J].Microcomputer Information,2009,25 (2):112-114 (in Chinese). [方勇,李国强,胡跃辉.基于Stratix III的DDR3SDRAM 控制器设计[J].微计算机信息,2009,25 (2):112-114.]

[5]Altera.DDR2and DDR3 SDRAM controller with UniPHY userguide[EB/OL].ftp://202.38.75.13/incoming/DOC/ddr2/emi_ddr3up_ug.pdf,2013.

[6]XIANG Houzhen,ZHANG Zhijie,WANG Peng.FIFO cache technology in video and image processing system based on FPGA[J].Video Engineering,2012,36 (9):41-42 (in Chinese).[向厚振,张志杰,王鹏.基于FPGA 视频和图像处理系统的FIFO 缓存技术 [J].电视技术,2012,36 (9):41-42.]

[7]ZHANG Gang,JIA Jianchao,ZHAO Long.Design and realization of DDR2SDRAM controiler based on FPGA [J].Electronic Sci & Tech,2014,27 (1):70-74 (in Chinese). [张刚,贾建超,赵龙.基于FPGA 的DDR3SDRAM 控制器设计及实现 [J].电子科技,2014,27 (1):70-74.]

[8]WANG Jiawen,LI Limu,PAN Hongbing.3DNoC based on statistical time division multiplex[J].Journal of Electronics &Information Technology,2012,34 (10):2050-2057 (in Chinese).[王佳文,李丽木,潘红兵.基于统计时分复用技术的三维片上网络[J].电子与信息学报,2012,34 (10):2050-2057.]

[9]LIU Jun,LIU Chao.Cable’S recognition technology based on the CCD vision [J].Journal of Chongqing University of Technology (Natural Science),2014,28 (2):93-98 (in Chinese).[刘军,刘超.基于CCD视觉的线缆识别技术 [J].重庆理工大学学报 (自然科学),2014,28 (2):93-98.]

[10]LI Dapeng,CAO Guohua,CHEN Jiyan.Research on imaging system based on STM microcontroller unit[J].Journal of Changchun University of Science and Technology (Natural Science Edition,2014,37 (1):38-42 (in Chinese). [李大朋,曹国华,陈佶言.基于STM32单片机驱动面阵CCD 实时图像显示的研究 [J].长春理工大学学报 (自然科学版),2014,37 (1):38-42.]