高速差分连接器测试方法及分析

陈毓彬,王文双

(工业和信息化部电子第五研究所元器件检测中心,广东 广州 510610)

0 引言

随着连接器技术的飞速发展,高速差分连接器作为一种传输高速信号的新型连接器,已广泛地应用于各个高速传输领域。相对于传统的单端传输方式而言,高速差分技术具有功耗低、误码率低和传输速率高等特点。但在实际应用中,影响高速差分连接器信号完整性的因素较多,如阻抗、串扰和数字传输率等性能参数。本文通过对高速差分连接器的主要性能参数的测试方法进行研究,综合地考核了高速差分连接器的信号完整性,从而评价了高速差分连接器传输性能的优劣。

1 高速差分连接器的测试方法

1.1 特性阻抗测试

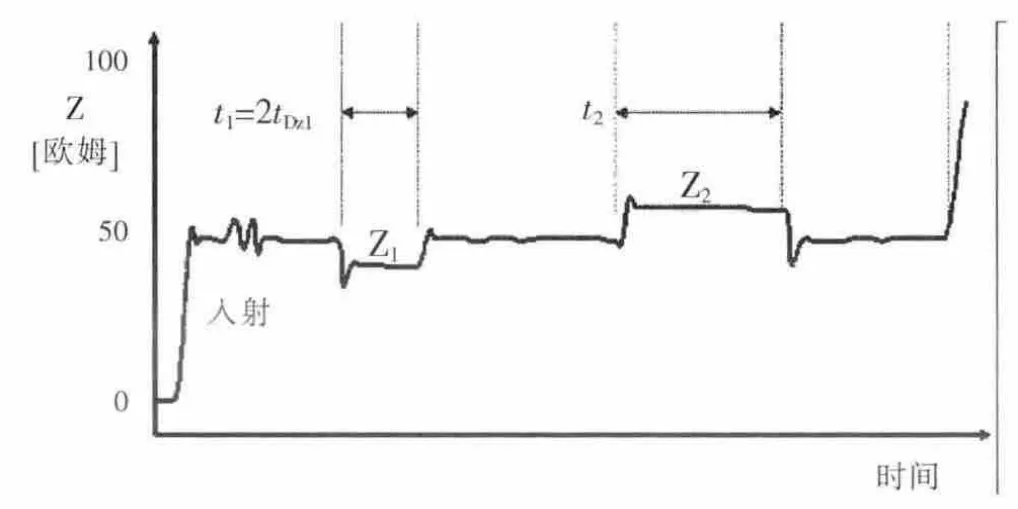

特性阻抗测试主要采用TDR测试,其原理主要是当传输路径中阻抗发生变化时,部分能量会被反射,剩余的能量会继续传输[1]。注入到高速线路中的能量、反射回来的能量与阻抗的变化有理论上的数学关系。只要知道发射波的幅度,然后测量反射波的幅度,就可以计算出阻抗的变化。同时只要测量由发射到反射波再次到达发射点的时间差就可以计算阻抗变化的位置。特性阻抗可通过信号在传输线路上的情况反映出来。一个阶跃信号在传输线上传输时,电信号到达某个位置时,就会令该位置上的电压发生变化,传输线在此位置对地形成了电流回路,因此就有阻抗的存在[2]。TDR测试方法是基于传输线的反射理论,在高速通道中,任何的阻抗不连续都可以在TDR波形中反映出来,如图1所示。

图1 TDR波形

1.2 串扰测试

当信号在传输线上传播时,有些电压和电流能传递到邻近的静噪传输线上,这些有害的耦合噪声被称为串扰[3];两条相邻传输线上的噪声可用图2所示的测试方法来测量,信号从传输线的一端输入,为了消除末端折射,在远端端接匹配负载,而噪声电压可在相邻的静态线两端测量,两端的噪声明显的不同。为了区分这两个末端,把距离传输信号源较近的一端称为近端串扰 (NEXT),离传输信号源较远的一端称为远端串扰 (FEXT)。在高速串扰测试时需要用一个模拟的干扰源向传输线上施加快速沿脉冲信号,同时测量相邻的被干扰线路上远端和近端的干扰噪声信号的幅度,通过公式可以计算出近端串扰和远端串扰。

图2 传输线上的串扰

1.3 数字传输率测试

数据传输率是指在单位时间内总线上传送的数据量,即每秒传送数据的最大稳态数据传输率[4]。在高速差分连接器的测试中,串扰对其的影响是不可能完全消除的;而传输信号间的串扰问题会严重地影响高速传输的误码率,从而影响到数据传输率。到目前为止,业界还没有一种科学、有效的统计方式来计算数据传输率。而对于数据传输率的测试,传统的测试方法是采用数字示波器来接收信号,观察差分信号对之间的串扰对连接器高速传输性能的影响,从而做出判断。如果将采集到的数字串行信号的比特位用余辉方式累积显示结果,那么叠加后的图形就会看起来和眼睛很像,所以通常把数据传输率简称为眼图[5],如图3所示。眼图能直观地显示码间串扰和噪声的影响,可以评价一个高速传输系统性能的优劣。

图3 差分连接器眼图

2 测试结果及分析

2.1 阻抗测试

本次测试以高速差分连接器为测试对象,每个高速差分连接器样品由4个差分同轴接触件组成,每个差分同轴接触件上对应地安装有2对差分接触件。将连接器中的1对差分接触件的一端按图4所示接入DSA8200数字串行分析仪中,分析仪的差分TDR模块端接一对100 Ω的四绞线电缆,被测高速差分连接器的接触件的另外一端接分析仪的接收端或接负载,将数字串行分析仪设置为差分测试模式。

图4 特性阻抗测试图

特性阻抗测试时的测试夹具应具有能及时地确定样品近端和远端的特性,即测试时能够及时地确定测试夹具内样品的近端和远端。被测样品的近端和远端可通过测量夹具单独的近端传输延迟、装置单独的远端传输延迟和装有样品夹具的传输延迟来确定。近、远端通常用下面的方法来确定:

a)将TDR设备与标准线路近端连接。观测显示器上TDR阻抗曲线急剧下降的时间。记录该时间作为样品近端的时间位置。

b)将TDR设备装有样品的装置相连接,并测量传输延迟。

c)装有样品装置的传输延迟与样品近端时间位置的差值即为样品远端的时间位置。

当受试样品阻抗与测试设备阻抗不匹配时,应具有阻抗匹配装置。插合的差分接触件按图4-9连接可靠,选择特性阻抗测试,设置测试上升时间为100 ps(10%~90%),可通过对差分接触件的阻抗进行叠加来得到差分合阻抗。特性阻抗测试的结果如图5所示。

由测试结果可得,该差分接触件的合阻抗为M1=C1+C2,该差分接触件对的特性阻抗在102.48~115.50 Ω 之间。

在测试过程中,测试装置的损耗、电路板线路、测试板介质的变化和其他问题都可能引起显著的测量误差。在图5中的TDR阻抗分布曲线中,横坐标为时间,纵坐标为阻抗;该曲线包括了样品两端的SMA转接器 (标记1、3)、传输线 (标记a、b)及被测样品 (标记2);根据该TDR阻抗分布曲线,专业测试人员能够快速地确定高速差分连接器的起始和终止、被测试高速差分连接器的最大和最小阻抗值,以及样品的平均阻抗。

图5 特性阻抗测试结果

在测试过程中,应考虑测试夹具的制作与阻抗匹配的问题。高速传输测试平台提供的是阻抗为50 Ω的SMA接口,测试时需把差分接触件通过导线转接成SMA接口或通过转接印制板转成SMA接口。由于高速连接器的种类较多,所涉及的测试夹具种类繁多,针对高速连接器、高速传输电缆、背板等专门设计了相关的测试夹具,这样将更有效地提高测试效率及准确性。当测试PCB印制板时,有时会使用差分探头,但使用探头的接触方式往往会由于人为的接触不均匀或连接不可靠而引起测试结果误差的增大,而采用SMA接口的连接方式能提供更为可靠、稳定的连接。

2.2 串扰测试

主要的串扰测试方法与步骤如下所述。

a)测量系统上升时间。由于夹具增加了激励阶跃上升时间,因此,测量系统的上升时间会大于测试设备的上升时间,需要测量上升时间 (在10%~90%电平范围内测量)。一般来说,测试系统应包括测试夹具、设备和连接线;若相关标准规定测量是以激励线路的输出而不是输入为标准,则应连同样品进行测量,得到实际的测量系统上升时间。

b)将实际的测量系统上升时间与要求的值或表1中的值匹配。记录测量系统阶跃幅度Am。

表1 推荐的测量系统上升时间

c)按图6所示连接被测样品,进行测量。

d)输出测量结果:从传输参数中读取串扰比(幅度相对值),单位dB。

e)再读取幅度相对值AS,计算串扰比A=AS/Am。

2.2.1 近端串扰

将高速差分连接器中的2对插合的差分接触件按图6a所示进行连接,未插合的差分接触对末端均需端接终端负载进行匹配。设置测试信号上升时间,由数字串行分析仪可读出接收通道的电压值,即为串扰电压。

图6 串扰测试图

在对高速差分连接器的差分接触件进行近端串扰测试时,设置测试上升时间为28 ps(10%~90%),如图7所示,高速差分连接器的反射曲线中间出现一个干扰信号,测试接收信号的电压为5.22 mV。近端串扰可以用公式 (1)表示:

式 (1)中:U11——测试信号输入通道电压;

U21——接收信号通道测试电压。

实测近端串扰时,测试信号的上升时间为28 ps(10%~90%)。则根据公式 (1)计算得知,该样品的近端串扰为39.6 dB。

图7 近端串扰测试

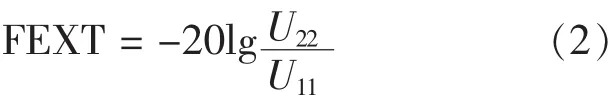

2.2.2 远端串扰

将高速差分连接器中的2对插合的差分接触件按图6b所示进行连接,输入不变,未插合的差分信号对末端均需端接终端负载进行匹配。将同一个接触件与输入差分对相邻的差分对导通对应的另一接触件差分对连接到数字串行分析仪来进行测试。设置测试上升时间为28 ps(10%~90%),如图8所示,测试接收信号通道的电压为3.68 mV。

图8 远端串扰测试

同样,远端串扰也可以用公式 (2)表示:

其中,U11——测试信号输入通道电压,U22——输入差分对相邻的差分对远端测试通道电压;实测远端串扰时,测试信号上升时间为28 ps(10%~90%)。则根据公式 (2)计算得知,该样品的远端串扰为42.7 dB。

高速差分连接器的性能参数、差分接触件间距、信号输出端和接收端的电气特性及端接方式等都对串扰有一定的影响。

2.3 数据传输率测试

将1对插合的差分接触件按图9所示接入数字串行分析仪,通过眼图对电连接器的传输性能做综合衡量。

图9 传输性能测试图

测试时,上升时间设置为200 ps(10%~90%),数据传输率为1.65 Gbps;要求输入电压为1 V时,测试所得到的高速传输连接器差分接触对的传输眼图中有50%的时间段内的输出电压大于408 mV。根据要求,设置相关眼图模板中的各点的坐标如表2所示:

表2 眼图模板坐标

按前面的测试方法对高速传输连接器进行测试,得到的测试眼图如图10所示,从图中可见眼图的眼睛 “睁开”得很大。

从测试结果可得,通过数字串行分析仪来处理一个连续信号的波形,可以显示出噪声、眼宽、眼高和抖动等相关信息。通过眼图的形状特点可以快速地表征数据传输率,眼图能直观地表明码间串扰和噪声的影响。眼图脉冲中部的开口面积是数据传输质量的指标。眼开度越大,传输质量越好,即比特 (bit)误码率越低。通过对眼图进行分析,测试人员能够准确、快捷地完成测试并对测试结果进行分析,定位问题,找出问题的根本原因。

图10 实测眼图

3 结束语

本文讨论了高速差分连接器中常用的信号完整性测试方法,包括特性阻抗测试、串扰测试和数据传输率测试。以测试方法为基础,高速差分连接器为测试样品,得出测试数据,客观评价高速差分连接器信号完整性的优劣,为产品的鉴定检验工作提供科学的依据。

[1]YD/T 926.3-2001,大楼通信综合布线系统第3部分:综合布线用连接硬件技术要求 [S].

[2]赵宇萍,刘治国.基于TDR技术的连接器高速传输性能测试 [J].电子产品可靠性与环境试验,2012,30(5):134-137.

[3]吴伯春,龚清萍.信号完整性分析技术 [J].航空电子技术, 2004, 35 (2): 20-24.

[4]吴世湘.军事/航天连接器发展态势研究 [J].电子产品世界, 2008 (2): 58-63.

[5]ERIC Bogatin.信号完整性分析 [M].李玉山,李丽平,译.北京:电子工业出版社,2005:10-13,132-138.