传感器高速采集传输系统中Aurora协议测试分析*

刘 京, 何怡刚, 罗旗舞, 史露强

(合肥工业大学 电气与自动化工程学院,安徽 合肥 230009)

0 引 言

在传感器高速数据采集传输[1,2]系统中,以现场可编程门阵列(field programmable gate array,FPGA)来作为硬件系统的核心,FPGA间的数据高速稳定传输的应用越来越多。Aurora串行总线协议是专用于FPGA间数据传输的高速接口协议。在Aurora协议传输通道中,数据以帧的格式进行传输,帧的格式由用户根据需求任意定义[3],因此,测试Aurora协议中的帧格式对通道数据传输率的影响,可以更加合理地利用Aurora协议。本文针对Aurora协议进行测试,分析了协议帧格式与通道数据传输率的关系,并验证分析结论的可靠性。

1 Aurora 64 B/66 B IP核

任何数据分组可以通过Aurora协议封装在芯片间,板间传输[4]。Aurora 64 B/66 B是在FPGA内嵌高速收发器硬核模块的物理编码子层(physical coding sublayer,PCS)采用64 B/66 B编码,开销仅有3 %左右[5]。Aurora协议的数据传输通道由多个“弄”绑定生成,在配置IP核时可以选择“弄”的数量,IP核内部逻辑结构如图1所示。

2 硬件系统设计

2.1 传感器高速采集与传输系统硬件设计

传感器高速数据采集与传输系统硬件框架主要包括传感器模块、模数转换器(analog-digital converter,ADC)采样模块、FPGA模块、DDR3数据缓存模块、上位机模块以及其他FPGA网络模块。传感器模块在检测过程中产生大量模拟信号的数据,经过ADC采样成数字信号通过JESD204接口协议[6]传输至FPGA中进行数据处理并通过DDR3模块进行数据缓存,FPGA通过PCIE高速总线与上位机进行数据交互[7]。系统整个硬件框架如图2所示。

图1 Aurora IP核内部逻辑结构

图2 传感器高速数据采集与传输系统硬件框架

FPGA为单层网络的核心,与其他FPGA网络的FPGA通过内部封装了对应的Rocket I/O 的Aurora协议进行数据交互,因此,Aurora协议的性能直接影响到整个网络系统高速数据传输的性能。

2.2 Aurora协议性能测试硬件设计

以Xilinx的Kintex—7 FPGA 为载体,利用FPGA上的GTX高速收发器进行单个“弄”通道,全双工模式的Aurora 64 B/66 B协议测试,传输通道采用差分模式以增加高速信号传输的抗干扰能力。Aurora 64 B/66 B IP核需要输入2路时钟驱动,吉比特(Gbit)的高速数据传输对时钟频率和质量要求很高,因此,外部输入时钟采用差分接口[8],外部时钟源采用的时钟模块NI PXIE—6674定时模块,利用高精度的DDS时钟生成LVDS电平标准的500 MHz的两路差分输出时钟,分别通过SMA射频线输入到两块Kintex—7 FPGA的GTX高速收发器的参考时钟输入接口。

3 软件设计

采用Xilinx的Vivado开发工具进行软件开发,整个软件框架主要包括顶层模块,帧产生模块,帧检测模块,IP核模块,复位模块,时钟模块与收发器配置模块。在顶层模块调用Aurora IP核,帧产生模块发送从DDR3缓存模块传送来的数据,帧检测模块对接收的数据进行检测,如果出现错误会有错误标志位error信号置高。

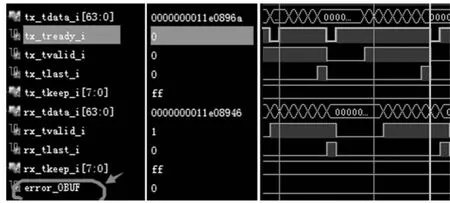

Aurora 64B/66B IP核采用AXI4-Stream 接口协议,该协议没有地址项,允许无限制的数据突发传输规模,适合于高吞吐量的数据传输[9]。通过在线逻辑分析仪(ILA)抓取待观测信号,如图3所示,通过虚拟I/O(virtual I/O,VI/O)修改帧长与帧间隙的值,对Aurora 64B/66B通道数据传输率进行实测。在图3中可以看到发送模块正确产生了所定义的帧格式。图中箭头标记的error信号位始终为低,表示数据正确接收,测试的通道数据传输率可靠。

图3 ILA信号观测

4 Aurora 64 B/66 B协议通道数据传输率测试分析

4.1 帧长对通道数据传输率影响测试

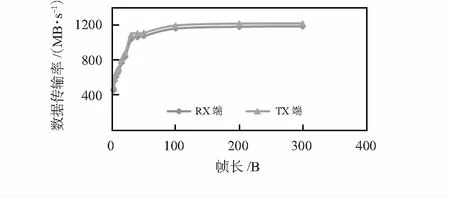

将帧间隙固定为10 B,帧长范围从1 B增加到400 B,对帧长范围内一些点进行采样,分别在发送端(TX)和接收端(RX)测试得到相应的通道数据传输率,测试结果如图4所示。

图4 帧长与通道数据传输率关系

可知当保持帧间隙不变,随着帧长的增加,通道数据传输率呈不断增加趋势,但增速下降,帧长增加到一定值后通道数据传输率接近数据传输率峰值,接近水平曲线。同时可以看到在RX端的通道数据传输率始终小于TX端,这主要因为时钟补偿和64 B/66 B编码补偿开销,为了更加准确测定通道数据传输率,采样测定RX端的通道数据传输率。

4.2 帧间隙对通道带宽影响测试

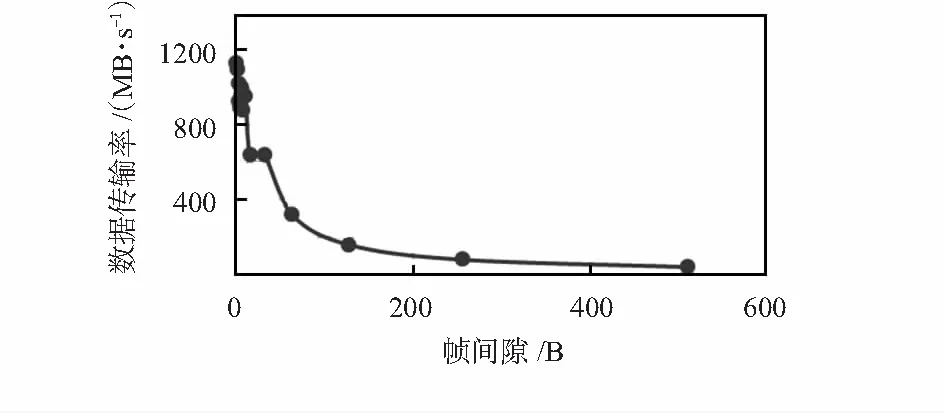

将帧长固定为15 B,帧间隙由0 B增加到511 B,对帧间隙范围内一些点进行采样,测试得到RX端通道数据传输率,测试结果如图5所示。

图5 帧间隙与通道数据传输率关系

可知,当保持帧长不变,随着帧间隙的增加,通道数据传输率呈不断减少趋势,但减速下降。

由此可见,Aurora 64 B/66 B协议中,帧和帧间隙的长度对通道数据传输率具有关键性的影响,帧长与通道数据传输率呈正相关,帧间隙与通道数据传输率呈反相关,因此有

(1)

式中Vr为当前实际有效数据传输率,MBps;Vp为通道数据传输率峰值,MBps;lfs为Aurora协议中帧的长度,B;lifg为Aurora协议中当前帧与下一帧之间的间隙,B。

为了验证式(1)结论的正确性,将帧间隙值固定为50 B,帧长不断增加,将采样点通道数据传输率测试值的曲线与式(1)理论通道传输率值进行对比,如图6所示。

图6 帧长与通道数据传输率关系

可以看到,式(1)理论曲线很好地拟合了采样曲线,说明了由Aurora 64 B/66 B协议中帧和帧间隙与实际通道数率传输率之间的关系的正确性。

通过Aurora协议进行高速数据传输时,在不同帧间隙值,根据式(1)选择合适的帧长既可以满足通道数据传输率的需求,又可以降低增加帧长带来的数据传输的时延以及传输过程中数据丢失出错的可能性,以平衡传感器高速数据采集传输系统中FPGA间数据传输时对通道数据传输率和通道性能的需求。

5 结束语

本文设计传感器数据高速采集与传输处理硬件系统,并以Kintex—7 FPGA为核心设计了Aurora 64 B/66 B协议传输性能测试硬件系统。在实际板级调试环境下采样测试了Aurora 64 B/66 B协议通道吞吐量范围内不同的帧格式下通道数据传输率值,得到了帧格式与通道数据传输率之间的关系,测试结论稳定可靠。结论对设计传感器数据高速采集与传输系统中合理的利用FPGA间数据交互的Aurora 64 B/66 B协议提供了参考。