2.5 GHz高线性度瓦级CMOS功率放大器的设计*

徐元中,梅 菲

(湖北工业大学 太阳能高效利用湖北省协同创新中心,湖北 武汉430068)

2.5 GHz高线性度瓦级CMOS功率放大器的设计*

徐元中,梅 菲

(湖北工业大学 太阳能高效利用湖北省协同创新中心,湖北 武汉430068)

设计了一个工作于2.5 GHz、最高输出功率达到 31.8 dBm的 CMOS功率放大器(PA),该PA由两级放大器组成,两级放大器均采用全差分电路结构。为了实现1 W以上的输出功率,第二级放大电路由两个完全相同的子放大器组成,然后通过高效率的片上功率合成器将两个子放大器的输出电压相加。片上二次谐波短路电路用来提高PA的线性度,对比没有采用二次谐波短路的PA,采用二次谐波短路后PA的三次谐波失真下降7 dB。该PA采用 TSMC 0.18 μm CMOS设计,采用Agilent ADS软件进行电路仿真和片上无源器件的设计,电路仿真结果表明:在2.5 GHz工作频率点,PA的输入完全匹配(S11=-25 dB),小信号增益达到25 dB,功率增益为19.4 dB,最高输出功率达到31.8 dBm,最高功率附加效率(PAE)达到32.9%,三阶交调失真在输出功率等于22.3 dBm时为-30 dBc。

CMOS;功率放大器;三阶交调失真;二次谐波短路

0 引言

功率放大器(PA)应用于发射机系统,将上变频之后的射频信号进行放大,然后输出到天线发射出去,由于PA处在发射机的末端,所以其线性度直接决定了发射信号的质量。随着现代调制方式越来越复杂,对发射信号的质量要求也更加严格,因此设计一个高线性度的PA成为了一个充满挑战的课题。另一方面,为了实现远距离通信要求,对PA的发射机功率要求也越来越高,目前常见的手机通信协议对PA的发射功率要求接近甚至超过1 W,无线局域网(WLAN)虽然对 PA的发射机功率要求只有20 dBm,但是由于WLAN采用正交频分复用技术(OFDM)调制方式,信号峰均比(PAR)达到17 dB,为了满足系统对线性度的要求,PA一般工作在功率回退的情况,同样为了满足WLAN输出功率要求,WLAN PA的最高输出功率也要设计到瓦级。

目前市场上主流 PA产品采用的是砷化镓(GaAs)、锗化硅(SiGe)等特殊工艺,虽然采用CMOS工艺设计制作的PA也已成功应用于手机产品[1],但是由于CMOS工艺一些难以克服的固有缺陷,CMOS PA市场占有率仍然较低。为了解决CMOS PA设计的问题并使所设计的PA达到一定的性能指标,将输出功率提升技术、线性度提

高技术和效率提高技术广泛应用于CMOS PA的设计[2-8]。本设计采用片上变压器合成技术增加PA的输出功率,二次谐波短路用来提高PA的线性度,从而实现了2.5 GHz高线性度瓦级CMOS功率放大器的设计。

本文所述的PA电路设计基于TSMC 0.18 μm CMOS工艺,仿真结果表明在 2.5 GHz工作频率点,输入完全匹配(S11=-25 dB),小信号增益达到25 dB,功率增益为19.4 dB,最高输出功率达到31.8 dBm,最高功率附加效率(PAE)达到32.9%,三阶交调失真在输出功率等于22.3 dBm时为-30 dBc。根据仿真结果,该PA达到输出功率、线性度和效率等性能指标的折中设计,可应用于2.5 GHz频段的发射机系统,实现高输出功率的单片CMOS收发器。

1 功率放大器的电路设计

2.5 GHz的整体电路结构如图1所示,包括输入变压器、驱动放大器、2个子功率放大器和功率合成器等4个模块。其中输入变压器用来实现单端输入信号到差分输出信号的转换;驱动放大器和子功率放大器结构相同,采用差分结构来输出更高的功率,同时抑制奇次谐波,提高PA的线性度;功率合成器实现两个子功率放大器的输出信号相加,同时将差分信号转为单端信号输出到负载。为了提高整体电路的稳定性,串联RC网络应用于驱动放大器和子功率放大器。输入变压器和功率合成器两端均有调谐电容,控制整体电路在2.5 GHz达到最优性能。差分结构的电感接在驱动放大器的正负输出端,和级间电容在 2.5 GHz谐振,同时从该电感的中心抽头给驱动级提供电源。

图1 2.5 GHz CMOS PA电路原理图

该PA的电路设计过程如下:从输出端开始向输入端逆向进行设计,首先选定功率合成器的结构、主次线圈比、几何形状;然后设计子功率放大级,确定MOS管的具体尺寸,采用负载牵引仿真,使得输出功率和效率达到最大值;下一步设计驱动级MOS管的尺寸和级间电感的大小;最后设计输入变压器,同样确定其线圈比、几何尺寸。以上电路尺寸确定完毕后还需要对PA整体电路进行优化仿真,在线性度和效率等性能之间进行折中处理,同时考虑后期版图的设计,对电路中的每个尺寸进行仔细核对并作合理优化,最终使PA各项性能指标达到设计要求。

2 功率合成器

随着CMOS工艺节点越来越小,可提供的电源电压也越来越小,但是MOS管的阈值电压并没有随之下降,这样为了增加PA的输出功率必须采用更大尺寸的MOS管,导致功率和面积增加。为了增加PA的输出功率,功率合成器广泛应用于 CMOS PA的设计[2,4-6],同时实现阻抗变换、差分信号转单端信号、静电保护等功能。根据输入信号接入形式,片上功率合成器可以分为串联和并联两种形式,其中串联功率合成器实现电流相加,并联功率合成器实现电压相加[4]。功率最大传输效率 Gmax用来衡量功率合成器的性能:

其中:

图1所示功率合成器用来实现两个子放大器的输出电压相加,其三维几何结构如图2所示,总面积大小为1 360 μm×450 μm,合成器的主线圈和次线圈均采用半圆结构,线圈宽30 μm,线间距3 μm。基于TSMC 0.18 μm CMOS工艺参数,采用电磁仿真软件 Momentum对该合成器进行仿真,仿真结果如图3所示,该功率合成器在2.5 GHz的功率传输效率达到82%。

图2 功率合成器三维示意图

图3 功率合成器的插入损耗

3 二次谐波短路

为了提高PA的线性度,系统级的数字预失真(DPD)[8]、电路级的偏置电路[4]、器件级的预失真[2]等技术被广泛应用于PA的设计,但是由于设计的复杂度,系统级和电路级的设计不免带来芯片面积和功耗的增加。DPD一

般将 PA的幅度和相位非线性参数存储查找表(LUT)中,LUT中的参数可以根据PA的实际测量结果更新,然后提供一个与PA相反的非线性特性,但是DPD需要复杂的基带处理算法,直接导致芯片面积和功耗的增加,同时还需要完整的预失真系统级设计,增加了PA的设计难度。作为一种器件级的线性度提高技术,PMOS补偿技术一般用来抵消NMOS栅端电容随栅端电压的变大而下降,使得NMOS栅端电容基本不随栅端电压摆幅变化,降低PA的相位失真,但是 PMOS管的加入会导致功率增益下降[2]。

本设计采用器件级的二次谐波短路技术,串联的LC网络谐振在两倍工作频率(5 GHz),接在差分功率放大器的共模节点:共栅管的栅端和功率合成器主线圈的中间节点(如图4所示),减小二次谐波因反馈存在和基频产生的交调失真。二次谐波短路对PA线性度的提高程度如图5所示,三次谐波交调失真(IMD3)用来衡量PA的线性度,在图4所示的节点加上二次谐波短路电路之后,IMD3最高达到7 dB的提升,对PA的线性度改善明显。

图4 带二次谐波短路的2.5 GHz CMOS PA电路原理图

图5 二次谐波短路对PA线性度的改善仿真结果

4 仿真结果

首先对该PA进行小信号S参数仿真,扫描频率范围1.5 GHz~3.5 GHz,仿真结果如图6所示。图中可以看到输入回波损耗S11达到-25 dB,输入阻抗在 2.5 GHz完全匹配,S21达到25 dB,说明电路整体在2.5 GHz谐振,参数取值合理。

图6 2.5 GHz PA的S参数仿真结果

然后对 PA进行大信号仿真,2.5 GHz单频点信号接在PA输入端,输入功率扫描范围-25 dBm~5 dBm,仿真PAE、输出功率和功率增益如图7所示,该 PA最高输出功率达到 31.8 dBm,最高 PAE为 32.9%,功率增益为19.5 dB。采用功率合成器可以实现瓦级输出功率,为高输出功率的 CMOS PA提供了一种非常有效的解决方案,降低了系统的设计难度。

图7 2.5 GHz PA的大信号仿真结果

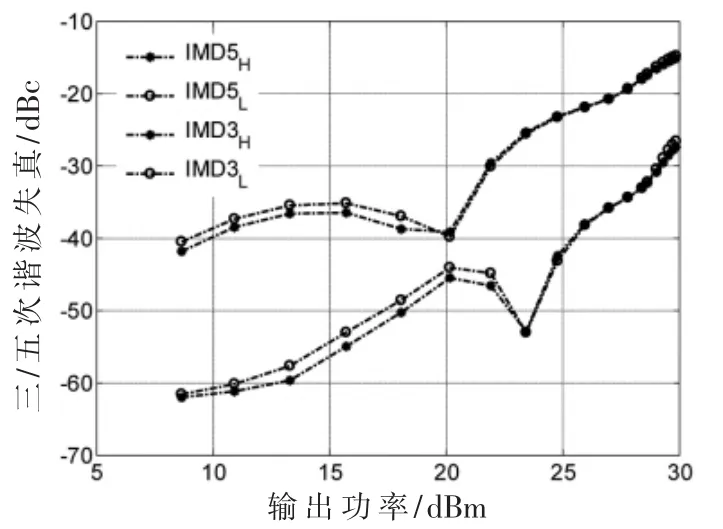

最后,为了对该PA的线性度进行仿真,两路频率相差5 MHz的双声信号(2.502 5 GHz和2.497 5 GHz)同时接在PA的输入端,同样对输入功率进行扫描,仿真IMD3和五次谐波交调失真(IMD5)如图8所示,其中IMD3在输出功率等于 20 dBm时为-40 dBc,IMD5在输出功率等于26 dBm时为-40 dBc。虽然IMD3和IMD5存在一定程度的不对称,可能导致相邻信道抑制比(ACPR)和误差相量幅度(EVM)的下降,但是对线性输出功率并不会产生明显影响,而且这一问题可以采用其他线性度提高技术来解决。

图8 2.5 GHz双声信号仿真结果

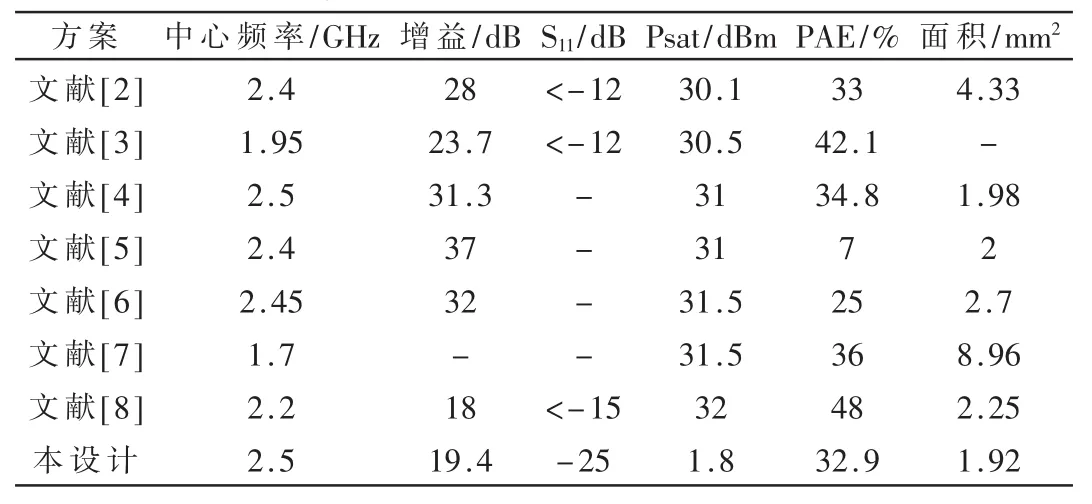

该PA和目前已有研究的成果进行对比结果如表1所示,整体性能在效率和线性度之间取得非常好的折中,输出功率也较高,虽然流片测试之后的性能会下降,但是本文所用的功率提升和线性度提高技术得到验证,

可以应用于同类PA的设计。

表1 PA性能指标对比

5 总结

设计了一个2.5 GHz的CMOS PA,通过采用功率合成技术和线性度提高技术来提升该PA的整体性能,片上变压器作为功率合成器在 2.5 GHz时其功率传输效率达到82%,二次谐波短路电路通过片上电容和片外键合金线的寄生电感谐振,大大降低芯片面积,同时对该PA的 IMD3改善达到 7 dB。该 PA采用 TSMC 0.18 μm CMOS进行设计,最高输出功率达到31.8 dBm,三阶交调失真在输出功率等于22.3 dBm时为-30 dBc,芯片面积仅为 1.92 mm2,具有高输出功率、高线性度、结构简单、匹配良好等优势。

[1]JOHANSSON T,FRITZIN J.A review of watt-level CMOS RF power amplifier[J].IEEE Trans.Microw.Theory Tech.,2014,62(1):111-124.

[2]CHOWDHURY D,HULL C D,DEGANI O B,et al.A fully integrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMAX applications[J].IEEE J.Solid-State Circuits,2009,44(12):1054-1063.

[3]KOO B,JOO T,NA Y,et al.A fully integrated dual-mode CMOS power amplifier for WCDMA applications[C].International Solid-State Circuits Conference.San Francisco:IEEE,2012:82-84.

[4]KIM J,YOON Y,KIM H,et al.A linear multi-mode CMOS power amplifier with discrete resizing and concurrent power combining structure[J].IEEE J.Solid-State Circuits,2011,46(5):1034-1048.

[5]AN K H,LEE D H,LEE O,et al.A 2.4 GHz fully integrated linear CMOS power amplifier with discrete power control[J].IEEE Microw.Wireless Compon.Letters,2009,19(7):479-481.

[6]AFSAHI A,BEHZAD A,LARSON L E.A 65 nm CMOS 2.4 GHz 31.5 dBm power amplifier with a distributed LC power-combining network and improved linearization for WLAN applications[C].International Solid-State Circuits Conference.San Francisco:IEEE,2010:452-453.

[7]WONGKOMET N,TEE L,GRAY P R.A 31.5 dBm CMOS RF Doherty power amplifier for wireless communications[J]. IEEE J.Solid-State Circuits,2006,41(12):2852-2859.

[8]DEGANI O B,COSSOY F,SHAHAF S,et al.A 90 nm CMOS power amplifier for 802.16e(WiMAX)applications[J]. IEEE Trans.Microw.Theory Tech.,2010,58(5):1431-1437.

Design of a 2.5 GHz high linearity Watt-level CMOS power amplifier

Xu Yuanzhong,Mei Fei

(Hubei Collaborative Innovation Center for High-efficiency Utilization of Solar Energy,Hubei University of Technology,Wuhan 430068,China)

A 2.5 GHz PA consisting of two-stage fully differential amplifiers is presented in this paper.The saturated output power reaches to 31.8 dBm,by combining the output voltages of two sub-amplifiers with the same configuration,which is included in the second stage amplifier.In order to improve the linearity of the PA,on-chip the second harmonic termination is proposed in the second stage to suppress the third harmonic distortion.Finally,the PA is designed and simulated in Agilent’s ADS using TSMC 0.18 μm CMOS spice model.According to the simulation results,S11 is less than-25 dB,S21 is 25 dB,power gain is 19.4 dB,the saturated output power is 31.8 dBm,the maximum PAE is 32.9%,and IMD3 is-30 dBc at 22.3 dBm output power.

CMOS;power amplifier;the third-order intermodulation distortion;capacitance compensation

TM277

A

0258-7998(2015)05-0063-04

10.16157/j.issn.0258-7998.2015.05.013

2015-01-12)

徐元中(1974-),通信作者,男,讲师,主要研究方向:射频集成电路设计及射频器件研究,E-mail:leo_josh@163.com。

国家自然科学基金(51371079)

梅菲(1980-),女,博士,副教授,主要研究方向:射频器件研究。