基于多DSP的遥感图像实时压缩系统设计*

贺文静,胡 坚,李子扬,孟凡荣,周春城

(中国科学院光电研究院 中国科学院定量遥感信息技术重点实验室,北京100094)

基于多DSP的遥感图像实时压缩系统设计*

贺文静,胡 坚,李子扬,孟凡荣,周春城

(中国科学院光电研究院 中国科学院定量遥感信息技术重点实验室,北京100094)

随着遥感技术的发展,对高分辨率的遥感图像实时压缩的需求日益迫切。设计了高性能的图像压缩系统,由8片ADSP-TS201为核心处理器和2片FPGA组成,可提供高达28.8 GFLOPS的峰值浮点运算能力。该平台采用PCIE总线作为外部接口,具有良好的可扩展性和强大的数据交换能力;各处理器采用Link Port互联,形成松耦合结构,可实现高速传输、实时处理和大容量存储三者的平衡,具有良好的可重构性和通用性。最后采用该系统实现JPEG2000压缩,实验结果表明,该压缩系统无损压缩速率可达6.2 Mpixels/s,非常适用于高分辨率、高质量遥感图像压缩领域。

多DSP;FPGA;图像压缩;JPEG2000;并行处理

0 引言

随着新型传感技术的发展,卫星遥感图像的分辨率迅速提升,数据量的爆炸式增长趋势为传输信道和存储空间带了极大的压力,因而,能否对遥感图像进行在轨实时高效压缩便成为制约遥感技术发展的一个关键问题[1]。目前,相对于基于离散余弦变化广泛采用的小波变换压缩算法具有非常好的抗误码性能,不过相对于早期的压缩算法,这类算法的复杂度明显提高,运算量和内存消耗增大[2],这对图像压缩处理系统提出了较高的要求。

FPGA和DSP在数据处理平台中发挥着日益重要的作用,FPGA擅长执行并行处理,而DSP擅长多算法任务和多条件操作等,因而采用FPGA和多片DSP的并行运算系统受到越来越多的关注。

为了探索遥感图像的机载实时压缩技术,本文首先根据遥感图像处理数据及流程特点,设计了 2 FPGA+ 8 DSP的并行拓扑架构,并构建了机载实时处理硬件平台,最后基于该平台介绍了JPEG2000压缩算法的实现方法,实验结果表明该平台具有较强的遥感数据实时处理能力。

1 图像压缩系统设计

1.1 芯片选型

在本系统中,FPGA主要实现外部接口、逻辑控制和时序控制等功能,并承担部分数据处理工作,因此,需要具有较大的存储空间,支持PCIE接口设计,具备较多的逻辑资源实现图像预处理功能,并具有足够的I/O口为FPGA管理多片DSP提供管脚支持。本系统选用Xilinx公司的XC6VLX240T。

为了满足遥感图像实时压缩的要求,系统中选用的DSP要具有很强的定点和浮点运算能力;要具有高性能的互联接口;支持DSP之间、DSP与FPGA之间建立高速的数据通道;并且具有较大的内部存储空间,适应图像压缩过程中大量中间数据的高速缓存。因此本系统选用ADI公司的TS201。

1.2 并行互联方式

实现大规模运算的高速执行,需要借助多个处理单元同时运行来减少任务执行时间。并行技术可以体现在处理器内部、处理器级以及系统级等方面,处理器间的拓扑结构可分为两种[3]:(1)多处理器共享总线和存储器的紧藕合结构;(2)多处理器通过独立接口实现互联的松藕合结构。

紧藕合结构的优点在于提供全局物理地址空间,允许任何处理器对等访问全部存储器,便于程序设计。ADSP-TS201的主机接口可以支持最高 64 bit位宽的总线共享,全局映射的统一寻址空间可实现多处理器及存储器间的无缝连接。但是,当处理器数目较多时,频繁的数据交换会产生严重的总线控制权竞争问题,从而导致系统运算效率降低,特别是在进行大数据量运算和大数据量通信时,这个缺点会极大地制约整个系统的运行效率。遥感图像的实时压缩是运算密集型、数据吞吐密集型的数据处理过程,紧藕合结构很难实现运算、存储、传输间的平衡,不利于实现复杂压缩算法的实时处理。

在分布式松藕合结构中,每片DSP通过独立的接口连接到FPGA,这样就能避免多个DSP同时访问FPGA时的数据冲突。FPGA与DSP间常用的接口设计方法主要有3种:(1)采用外部双口RAM;(2)在FPGA内部构建双口RAM;(3)通过DSP的高速传输接口。前两种连接方式中数据直接通过总线传输,且不涉及复杂的通信协议,接口设计比较简单[4],但是当芯片数量较多时,硬件设计中的管脚及布线压力会很大;另外DSP的数据总线将同时用于与FPGA和与外部存储器通信,仍然会存在总线竞争风险。TS201可提供4路链路口,在采用4位并行方式传输时,可支持高达1.2 GB/s的双向吞吐率;数据通信可由处理器核控制,也可由DMA控制器控制,而不需要占用处理器资源,这能为FPGA与DSP、DSP与外部存储器以及DSP与DSP之间的高速数据传输提供便利,解决在数据密集型处理中这一制约系统整体性能的问题,因此,本系统将采用这种互联结构。

1.3 系统结构

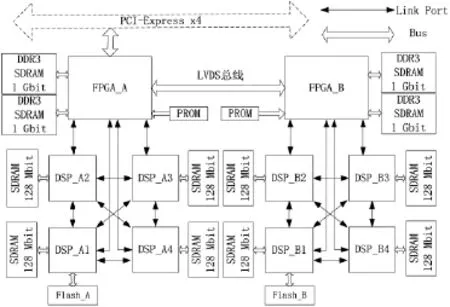

本系统采用2片FPGA和8片DSP的拓扑结构,其结构框图如图1所示。8片DSP分为结构对称的2簇,构成两个并行的运算子模块。每簇内的4片DSP利用链路口点对点互联,并且每片DSP分别通过一个链路口与FPGA相连。2片FPGA各负责一个运算子模的任务和数据交互管理工作。这种拓扑结构使得簇内各DSP以及DSP与FPAG间都能实现高速互联,且增强了数据流的灵活性,可实现按任务划分的流水并行计算,也可实现按数据划分的分布式并行计算。每片 DSP都外挂4 M× 32 bit的 SDRAM作为外部存储空间,利用 TS201内的SDRAM地址映射空间和外部接口,借助SDRAM控制器可轻松实现无缝连接,满足大量数据实时处理过程中的存储需求。DSP采用EPROM和链路口相结合的程序引导和加载方式[5],每簇外挂 1片 Flash,簇内其他 DSP采用链路口形式,这种设计避免了给每片 DSP配备Flash,降低了功耗和电路面积。

图1 图像压缩系统结构框图

1.4 FPGA程序设计

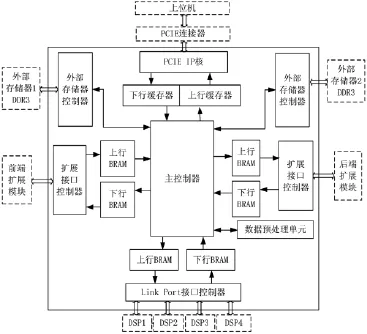

在本系统中,FPGA作为逻辑控制中心,主要实现以下几个功能:(1)数据解包、切分、串/并转换、打包、分发等数据管理功能;(2)数据缓存,利用DDR3 SDRAM乒乓作业的工作方式实现数据无缝缓存;(3)快速流水协议,实现与TS201链路口进行高速通信;(4)自定义接口协议,参考快速流水协议设计自定义协议,通过LVDS总线实现与另一片FPGA通信;(5)数据预处理功能,利用内部DSP和逻辑资源实现数据预处理,发挥FPGA并行处理的运算优势。此外,系统中的 FPGA_A还负责与上位机通信,因此,需要利用设计 PCIE接口单元。FPGA_A中的逻辑结构如图2所示,FPGA_B采用相似的逻辑设计。

2 JPEG2000压缩应用实例

JPEG2000作为新一代静止图像压缩标准,能在甚低比特率压缩时提供良好的率失真特性和主观视觉质量,并且具有非常好的抗误码性能,在星载遥感图像压缩领域受到越来越多的关注。

JPEG2000的基本编码过程为:源图像数据经正向预

处理后进行离散小波变换(DWT),对变换后的DWT系数进行量化,再进行熵编码,最后根将熵编码后的数据组织成压缩码流输出[6]。

图2 FPGA逻辑结构示意图

为了使程序在 TS201上高效运行,从系统层、算法层、代码层三个不同层面上对JPEG2000压缩程序进行了优化[7,8],例如:优化DWT中的中间结果存储方式,在节约内存的同时减少访问时间;采用建立上下文索引表的方法减小嵌入式最优截断编码过程中的扫描运算量;适当修改数据类型,进行数据拼接存储,提高数据读写效率等。

2.1 DSP与FPGA接口设计

此外,系统的高效运行还依赖于高效的数据收发机制。DSP通过 LinkPort接口与FPGA通信,实现原始图像数据的接收和压缩码流的发送,本系统DSP中的发送和接收单元中分别采用了乒乓缓存+突发式DMA传输的设计方法。以数据接收单元为例,DSP中分配了3个缓存空间:input_buffer1、input_ buffer2和input,其中,input_buffer1和input_ buffer2以乒乓作业的方式缓存接收数据,input用于缓存预处理后的图像数据,以备后续压缩处理。在接收数据时,DSP接收到FPGA的发送指令,便开启Link Port接口接收数据到Link Port Receive Buffer中,在接收到指定数据量后,Link Port接口自动开启 DMA传输,将数据转移到 input_buffer1中,并关闭 Link Port口,以防止接收到错误数据。此后,DSP对input_buffer1中的数据进行数据类型转换等预处理,然后转存到input缓存区中。考虑到Link Port接收、DMA传输均需要耗时,而又可以不需要内核参与,因此,设计了双通道乒乓作业的接收方式,这样在数据的突发传输任务中,可以配置好参数交给Link Port接口和DMA来独立完成,从而解放出内核的逻辑计算单元,使之专注于运算和判断。DSP内核在监测到本次DMA传输完成后,首先交换DMA接收端的选择指针,指向input_buffer2,再开启Link Port接口,便可以利用内核进行预处理操作了。处理过程中如果有新数据到来,硬件会自动完成接收操作并更改状态标识,内核只需要在完成当前处理后,查询其状态标识便可知道数据是否已经接收完成。如此循环,便可实现图像数据的快速接收。

2.2 软件设计流程

从系统层面来看,FPGA与其控制的4片 DSP组成两个运算节点A、B,8个DSP之间执行以数据划分的分布式并行计算。FPGA_A通过PCIE总线接收源图像数据,解析包头获取任务信息并进行串/并转换、数据缓存、数据切分、将数据分发给DSP和FPGA_B等。DSP内的压缩处理以图像块为单位,在完成当前图像块数据的接收后,开始压缩处理并将压缩码流实时回传至FPGA,DSP内程序流程如图3所示。FPGA接收各DSP发送的压缩数码流数据包,再以图像块为单位进行码流重组、缓存,最终通过PCIE总线传输给上位机。

图3 DSP程序流程图

3 实验结果

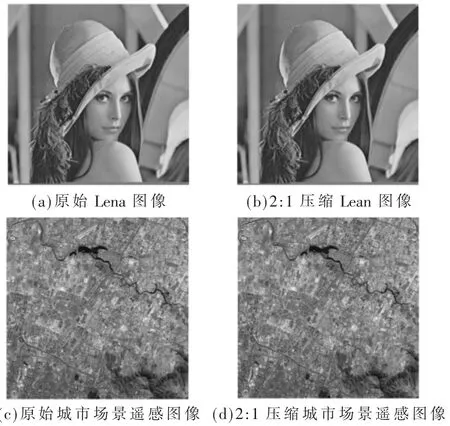

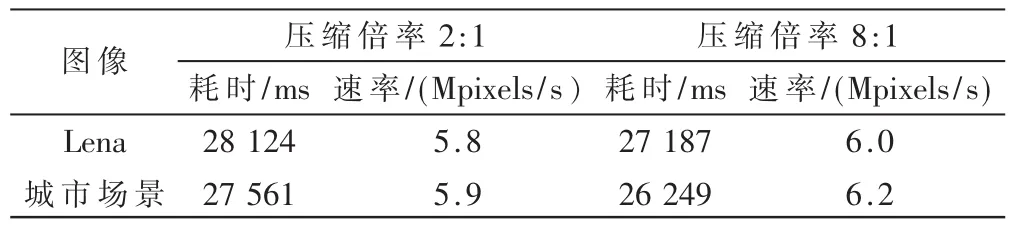

为了验证压缩系统的可行性,本文采用12 800×12 800

的8 bit图像数据分别进行了 2:1无损压缩和 8:1高倍率压缩实验。图4所示为Lena图像和一副纹理复杂的城市场景遥感图像的无损压缩实验结果,可见系统具有较高的压缩质量。表1为应用本平台的JPEG2000压缩系统的性能测试结果,无损压缩时系统最高吞吐速率可达5.9 Mpixels/s,高倍率压缩时性能略有提升,最高吞吐速率可达6.2 Mpixels/s,可见,本系统具有较强的数据处理能力。

图4 JPEG2000压缩效果图

表1 JPEG2000压缩性能测试

4 结论

本文首先分析了多DSP并行处理拓扑结构及片间互联方式,为了有效平衡系统运行速度、数据传输能力和板上存储空间三大因素,采用松藕合结构设计了基于2 FPGA+8 DSP的高速大容量实时压缩处理平台。最后,基于该平台实现了JPEG2000压缩处理。实验结果表明,该系统具有强大的数据处理和吞吐能力,能够为遥感图像实时压缩应用奠定技术基础。

[1]刘荣科,张晓林,廖小涛.星载遥感图像压缩编码技术综述[J].遥测遥控,2004,25(2):7-12.

[2]肖志东,肖明君,刘森.基于小波变换的遥感图像压缩算法综述[J].科技创新导报,2008(35):75.

[3]Wu Jie.分布式系统设计[M].高传善,译.北京:机械工业出版社,2001.

[4]唐垚,曹剑中,李变侠,等.高分辨率图像采集与压缩系统的设计实现[J].科学技术与工程,2007,5(20):1510-1513.[5]Analog Devices.ADSP-TS20x TigerSHARC processor boot loader kernels operation[Z].2004.

[6]ISO/IEC 15444-13:2008(E).Information technology-JPEG 2000 image coding system:An entry level JPEG 2000 encoder[S].2008.

[7]BISHOP S L,RAI S,GUNTURK B,et al.Reconfigurable implementation of wavelet integer lifting transforms for image compression[C].ReConFig 2006,IEEE International Conference on:1-9.

[8]LIAN C J,CHEN K F.Analysis and architecture design of block-coding engine for EBCOT in JPEG2000[J].IEEE Transactions on Circuits and Systems for Video Teehnology,2003,13(3):219-230.

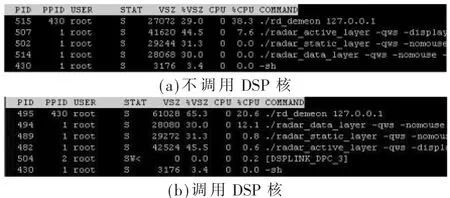

图9 CPU占有率

5 结论

本文通过设计和实现一个中间件软件,屏蔽了基于多播机制的雷达扫描单元和基于单播机制的雷达显示单元通信接口的不同,实现了多个扫描单元和多个显示单元同步相连,并可以通过裁剪中间件软件功能,让不同的显示单元有不同的功能。ARM端通过标准的API接口调用DSP核处理数据,不仅解决了单核ARM处理器处理数据时性能不足而产生的丢包现象,而且节约了宝贵的CPU资源,解决了由于硬件资源的限制而产生的顿卡现象。测试结果表明,加入中间件后雷达显示系统运行效果良好,达到了预期的效果。

参考文献

[1]杨建宇.线性调频连续波雷达理论与实现[D].成都:电子科技大学,1991.

[2]范多亮.雷达显示终端中的死点分析[J].信息化研究,2010,36(3):13-15.

[3]谢希仁.计算机网络[M].北京:电子工业出版社,2008.

[4]陈筱倩,周陬,王宏远.基于 IP组播的流媒体服务器软件设计[J].微电子学与计算机,2004(12):76-80.

[5]张云勇.中间件技术原理与应用[M].北京:清华大学出版社,2010.

[6]BOVET D P,CESATI M.深入理解Linux内核[M].陈莉君,张琼声,张宏伟,译.北京:中国电力出版社,2007.

(收稿日期:2015-01-15)

作者简介:

唐国珍(1987-),男,硕士研究生,主要研究方向:嵌入式系统、信号与信息处理。

张士宗(1988-),男,硕士研究生,主要研究方向:信号处理算法及硬件实现。

裴旭(1989-),男,硕士研究生,主要研究方向:信号与信息处理。

A real-time compression system for remote sensing image based on multi-DSP

He Wenjing,Hu Jian,Li Ziyang,Meng Fanrong,Zhou Chuncheng

(Laboratory of Quantitative Remote Sensing Information Technology,Academy of Opto-Electronics,Chinese Academy of Sciences,Beijing 100094,China)

The demand for real-time compression of high-resolution remote sensing image is becoming urgent,with the development of remote sensing technology.A multi-DSP parallel processing system for real-time image compression is designed.The system is composed of eight DSPs and two FPGAs,providing 28.8 GFLOPS operations performance.PCI-Express bus is used as external interface,providing the powerful capability of communication and expansion.To archive the high performance in data transmission,processing and large capacity storage,the loose coupled parallel architecture is used,with processors interconnected by Link Port.An application example of JPEG2000 compression based on this system is given.It is shown that the throughout speed of the system can achieve 6.2 Mpixels/s with lossless compression.Therefore,it is suitable for the compressing application of high-resolution remote sensing image.

multi-DSP;FPGA;image compression;JPEG2000;parallel process

TP752

A

0258-7998(2015)05-0046-04

10.16157/j.issn.0258-7998.2015.05.008

2014-12-08)

贺文静(1986-),通信作者,女,硕士,助理研究员,主要研究方向:嵌入式信号处理系统,E-mail:hewenjing@aoe. ac.cn。

胡坚(1972-),男,硕士,研究员,主要研究方向:信息与电子科学。

李子扬(1977-),男,博士,研究员,主要研究方向:遥感图像处理技术。

国家科技支撑计划项目(863计划)(2011BAH23B01)