一种恒流源功率管驱动电路

袁义生,朱本玉,罗 峰

(华东交通大学电气与电子工程学院,江西 南昌330013)

随着开关电源效率、功率密度的不断提高,越来越多研究及开发人员将目光投向了驱动电路。而传统的驱动电路损耗大、开关速度不可调等缺点,致使其无法实现变换器的更高效要求。一些学者针对低压大电流变换器的同步整流技术[1-3]进行了研究,并提出了一些改进型的驱动电路[4-5],但此类驱动电路存在驱动能量不可调、能量都消耗在驱动回路的阻抗上的问题,且随着开关频率增加,驱动损耗呈曲线上升趋势。因此,谐振驱动技术[6-8]被提出应用于高频变换器中以减小高频驱动损耗。文献[9]提出了适用于双MOSFET管的谐振驱动电路。为获取更低的驱动损耗,文献[10]提出一种高效能量回馈、低导通损耗谐振驱动电路。文献[11]则直接采用变压器漏感来替代谐振电感,实现更高功率密度。然而谐振驱动电路存在不能直接有效减小主功率管开关损耗的缺点。

针对这一问题,提出一种恒流源驱动电路,通过全桥结构中特定的开关组合给电感充放电,从而获得所需驱动电流,由于驱动时间短,而电感电流不能突变,从而实现恒流驱动。搭建实验电路,通过对比试验,验证了所提驱动电路的有效性。

1 拓扑结构及工作原理

1.1 拓扑结构

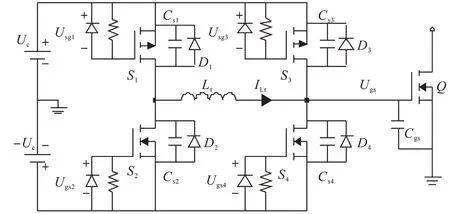

图1为所述自适应驱动拓扑结构,由1个正电源Uc、一个负电源Uc、4个MOSFET(S1-S4)和电感Lr组成。其中,4 个MOSFET 呈全桥结构,S1、S3为P沟道MOSFET,S2、S4为N 沟道MOSFET。二极管(D1-D4)为MOSFET体二极管,电容(Cs1-Cs4)为MOSFET寄生电容,iLr为电感电流。usg1、ugs2、usg3、ugs4分别为开关管S1、S2、S3、S4的驱动电压,Cgs为主管Q的前栅源极板间电容,Ugs为主开关管Q的驱动电压,方向如图1所示。

1.2 电路工作原理

图1 所提恒流源驱动拓扑结构Fig.1 Proposed topology of constant current-source drive

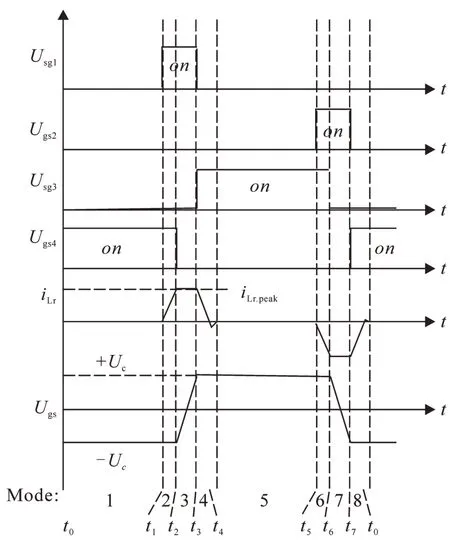

图2 主要工作波形Fig.2 Main operation waveforms

图2为驱动电路主要工作波形。调节相关开关管时序即可改变电感Lr的充放电时间,得到一个峰值电流iLr.peak,具体体现在图2中的Mode 2,4,6,8 四个阶段。实际电路中的Mode 3和7过程持续时间相当短,为ns级,电感电流在此谐振过程中几乎不变。

该驱动电路由8 个工作模态组成。前半周期与后半周期电路工作基本对称,因此仅分析半个周期的4个工作模态,各模态分析如下。

1)模态1(t0-t1):t0时刻,S4开通,电感电流iLr减小到零。驱动回路由电容Cgs、-Uc和S4体电阻组成,主功率管栅源电压Ugs被钳位在-Uc。t1时刻,该模态结束。

2)模态2(t1-t2):t1时刻,S1开通,电感电流iLr从零开始线性上升,回路为Uc-S1-Lr-S4-(-Uc)。该模态为Lr充电过程,t2时刻,充电过程结束,电感电流达峰值iLr.peak。在该过程中,Ugs仍被钳位在-Uc,保证主开关管处于有效关断状态。

3)模态3(t2-t3):t2时刻,S4关断,iLr给Cs4、Cgs充电,同时Cs3放电。由于此过程持续时间很短,且电感较大,因此,该阶段中iLr基本不变,且Cgs相对Cs3、Cs4较大,几乎以恒定的电流驱动主管Q。t3时刻,Ugs达到Uc时,该模态结束,此时,Cs4充电至2Uc,Cs3放电至0。实际电路设计中,为确保驱动电路中开关管的驱动信号的可靠性,使时间段(t2-t3)大于主管的开通时间,这样会出现一个短暂的环流过程,回路为Lr-D3-S1。

4)模态4(t3-t4):该模态分3个小阶段。t4时刻,关断S1,开通S3,此后,iLr线性下降,回路为Uc-S3-Lr-D2-(-Uc)。电流降为0后,将继续以该回路反向谐振,iLr反向增加,谐振至Cs2上电压至2Uc,使得D1导通,之后进入续流阶段,电感电流将减小至0。该模态中S3处于可双向导通状态,保证了主管Q的可靠开通。

2 电路特性分析

2.1 驱动的逻辑实现

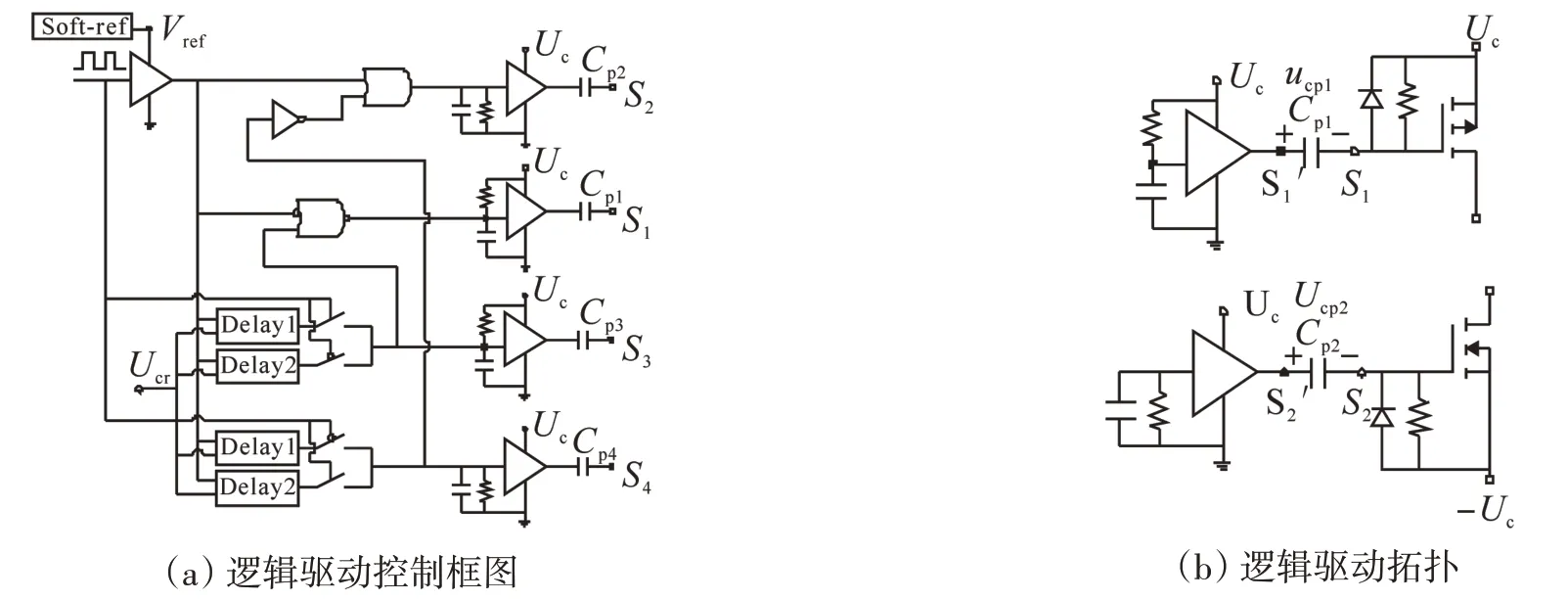

图3为逻辑驱动结构。图中通过对低电平有效的PWM信号和开关调节电压Ucr分别进行逻辑和延时处理,得到四组可调脉冲驱动信号去触发S1-S4。

采用图3(a)所示逻辑驱动控制实现四组非隔离驱动,图3(b)中仅示S1、S2逻辑驱动拓扑结构,S3驱动拓扑结构结构同S1,S4驱动拓扑结构结构同S2。Cp1、Cp2为隔直电容Soft_ref为软起结构,Delay为延时模块。逻辑驱动信号上电后,脉冲电源Vref软启动,S’1、S1电压均为Uc,使得ucp1为0;S’2电压为0,S2电压为-Uc,使得ucp2为Uc,方向如图3(b)所示。Vref软启动结束后,隔直电容上电压平衡,由于其电容值远大于MOSFET栅源电容,故不影响驱动过程。隔直电容稳定时间为

其中:Cp为隔直电容容值;Rg为栅源极并联电阻,二极管和栅源极寄生电容远小于Cp,故忽略。脉冲电源Vref软启动时间需大于隔直电容稳定时间τ,避免出现MOSFET直通现象。

图3 逻辑驱动结构Fig.3 Structure of logical drive

2.2 电感设计

主管开通过程中,有如下电路方程

设计中,Uc为12 V直流源。从图2可知,电感充电时间段(t1-t2)处于Q管关断期间,(t5-t6)处于Q管导通期间。要维持恒定的电流驱动Q,电感Lr不宜过低,因此,t12相对t23较大,理论最高驱动频率为1/(4t12),即电感电流处于连续状态。实际驱动中,iLr.peak选择安培级,假定设计iLr.peak=2 A,Lr=7 μH,由式(2)计算可知t12=583 ns,最高驱动频率fmax=428.8 kHz,故在一般的电路中,电感电流完全可以做到断续。占空比的大小取决于各管的时序安排,因此需合理配置好各管驱动信号时序。

2.3 驱动电路损耗分析

从波形图不难发现,t3时刻,主管电容电压Ugs升高到Uc,同时Cs3上电压降至0,此时开通S3、S3可获得ZVS开通;t7时刻,Ugs达到-Uc,Cs4上电压降至0,此时开通S4、S4为ZVS开通。该电路中,S1、S2未能获得软开关,但t1、t5时刻显示,电感电流从0开始线性增加,且相对较缓慢,因此S1、S2以较低电流开通,其开通损耗相对较低。

除此之外,驱动电路自身损耗主要在电感充放电阶段,充电回路(-Uc-S4-Lr-S1-Uc)为串联RL电路。令R1,R4,RL分别为S1,S4和Lr的内部等效电阻,令等效总电阻为Rz=R1+R4+RL,t12为充电时间。则电感电流满足如下方程

由上式可解得电感电流为

则可得电感充电结束时的电流

该阶段功率损耗为

由于各充放电阶段的回路参数基本相同,因此,其余充放电阶段功率损耗表达式与式(6)相同,在电路的单个工作周期内,驱动电路的充放电功率损耗为4Pch。值得注意的是,在Mode 4和Mode 8两个模式中,电感电流流向直流源,向电源输入端反馈能量。

3 实验与分析

搭建实验电路:S1、S3选择P沟道MOSFET IRF4905,其RDS(on)为20 mΩ;S2、S4选择N沟道MOSFET IRFZ44Z,其RDS(on)为13.9 mΩ。Uc、-Uc选择正负12 V 直流源,电感Lr取值7 μH;主电路开关管选择IRGP4063D,其输入电容典型值为Cies=3.025 nF。

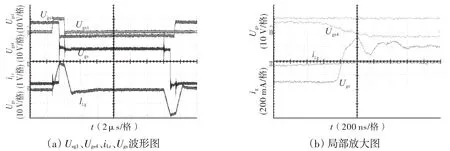

配置不同的Delay1(即t1~t2,t5~t6)值,即可获得不同的电感电流峰值iLr.peak,从而使主管Q获得所需等级的驱动电流。图4为传统驱动电路驱动波形,图4(b)显示,开通过程中,驱动电流先上升后下降,峰值达350 mA,开通时间长达700 nS。图5为采用所提电路的驱动波形。图5(a)中,Delay1 为520 nS,可计算知iLr.peak=1.8 A,从图5(b)中可知,Ugs从-Uc上升到+Uc用时20 ns,与图4(b)中对比,驱动电流增加,驱动时间大幅度减少,从而减少主开关管开关损耗。

图5 ilr.peak=1.8 A时的波形图Fig.5 Waveforms under ilr.peak=1.8 A

将所提驱动电路与普通驱动电路应用在Boost 电路上,测试该电路在不同驱动电路下的系统总效率,所测得两者的效率对比曲线如图6所示。从测试结果可知,在额定负载附近,采用所提驱动电路的系统的效率提升了1%以上;轻载时,效率提升幅度更大,高达2.2%。

图6 效率对比曲线图Fig.6 Comparison curves of efficiency

4 结论

提出了一种恒流源功率管驱动控制电路,设计了相应的驱动管开关逻辑关系与电路实现,电路具有以下特征。

1)利用电感电流不能突变原理实现恒流驱动主开关管的开通与关断。

2)驱动电路中部分开关管可做到软开关。

3)电感电流工作于断续状态,减少了不必要的通态损耗。

4)可实现能量回馈。

该电路的主要缺点是驱动过程中存在一个环流过程,但该环流电流较小,持续时间较短。通过实验验证了所提驱动电路的可行性及有效性,相比传统驱动电路,在不同输出功率下,电路效率均有所提高。

[1] 胡宗波,张波.同步整流器中MOSFET 的双向导电特性和整流损耗研究[J].中国电机工程学报,2002,22(3):88-93.

[2] 胡宗波,张波.新型栅极电荷保持驱动同步整流器的研究[J].电工技术学报,2003,18(2):45-50.

[3] 黄占伟,周娟,谢承旺.一种优化同步整流AC/DC变换器的应用研究[J].华东交通大学学报,2012,29(2):36-40.

[4] 顾亦磊,黄贵松,章进法,等.一种新颖的同步整流驱动电路[J].中国电机工程学报,2005,25(5):74-78.

[5] 顾亦磊,黄贵松,章进法,等.一种适用于模块并联的同步整流驱动电路[J].中国电机工程学报,2005,25(4):25-29.

[6] FUJITA H.A resonant gate-drive circuit capable of high-frequency and high-efficiency operation[J].IEEE Trans Power Electron,2010,25(4):962-969.

[7] WIEGMAN H L N.A resonant pulse gate drive for high frequency applications[J].Proc Appl Power Electron Conf,1992(23-27):738-743.

[8] 郭晓君,林维明.新型双功率MOSFET管谐振驱动电路[J].中国电机工程学报,2011,31(33):44-51.

[9] DWANE P, SULLIVAN D O, EGAN M G.An assessment of resonant gate drive techniques for use in modern low power dc-dc converters[J].Proc IEEE APEC,2005(3):1572-1580.

[10] EBERLE W,SEN P C,LIU Y F.A new resonant gate drive circuit with efficient energy recovery and low conduction loss[C]//Proceedings of Industrial Electronics Society,Raleigh,USA:IEEE,2005:650-655.

[11] XU KAI,LIU YANFEI,SEN P C.A new resonant gate drive circuit utilizing leakage inductance of transformer[C]//Proceedings of IEEE Industrial Electronics,Paris,France:IEEE,2006:1933-1937.