基于FPGA实现OmniVision图像传感器的SCCB总线协议

王水鱼,王 欣(西安理工大学 自动化与信息工程学院,陕西 西安 7100048)

基于FPGA实现OmniVision图像传感器的SCCB总线协议

王水鱼,王 欣

(西安理工大学 自动化与信息工程学院,陕西 西安 7100048)

基于Atera公司的FPGA芯片对OmniVision图像传感器进行图像采集前的准备工作,通过FPGA的GPIO端口模拟SCCB(串行摄像机控制总线)总线协议对传感器的寄存器进行配置,从而完成对传感器的初始化,使得摄像头得以正常运行。

FPGA;OmniVision图像传感器;SCCB

0 引言

视频信号处理系统的前端部分是视频图像采集,是视频监控、信息处理等系统的前端需要,对后端图像处理系统的性能有着直接的影响。近年来,随着通信技术和计算机技术的发展,人们对视频采集的要求越来越高,正在向高速、高分辨率、高集成化、高可靠性方向发展。现场可编程门阵列(FPGA)具有规模大、集成度高、可靠性高等优点,对于视频采集是非常理想的选择与趋势[1]。

OmniVision图像传感器具有独有的传感器技术,通过减少或消除光学或电子缺陷(如固定图案噪声、托尾、浮散等),提高图像质量,得到清晰稳定的彩色图像,并具有软件可编程性,从而决定了此系列的传感器应用越来越广泛。传感器正常工作的前提是对寄存器进行配置,使其按照需要的输出方式、图像质量和数据格式进行输出,即对其初始化。OmniVision传感器的初始化是通过SCCB总线协议的方式实现的,利用FPGA实现图像采集的关键是在FPGA中实现SCCB总线协议[2-3]。

1 SCCB总线协议

串行摄像机控制总线(Serial Camera Control Bus,SCCB)由OmniVision公司开发,广泛应用于 OV系列图像传感器上,是一种串行3线的总线,它由时钟信号SIO_C、数据信号SIO_D和使能信号SCCB_E组成,可实现一个主器件对多个从器件的控制,如图1所示。本文把芯片的引脚缩减为两根,只用数据信号SIO_D和时钟信号SIO_C,但是省去SCCB_E后的SCCB总线只能实现一个主器件对一个从器件的控制,如图2所示。在本文中FPGA为主控件,OV系列传感器为从器件[4]。

1.1 SCCB起始和终止时序

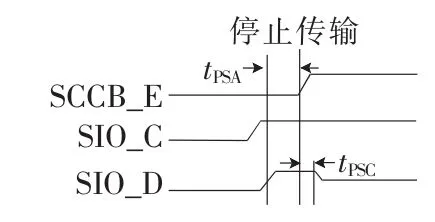

起始信号和终止信号都是由FPGA产生的,当SIO_C是高电平时,SIO_D从高电平转到低电平时产生起始信号,如图3所示;当SIO_C是高电平时,SIO_D从低电平转到高电平时产生终止信号,如图4所示。

图2 2线SCCB功能框图

图3 SCCB起始信号

图4 SCCB终止信号

1.2 SCCB写时序

相(Phase)是SCCB进行数据传递的基本单位,一相由连续传输的8位数据与其后的第9位(共9位)组成。第9位在读数据和写数据时分别为自由位(Don′t care bit)和NA位(Ninth bit of a Read phase)。写时序由3相构成,先写设备地址,再写寄存器地址,最后再写需要配置的寄存器的数据,即ID-Address+SUB-Address+WData,如图5所示。

图5 SCCB3相写传输周期

1.3 SCCB数据传输有效性

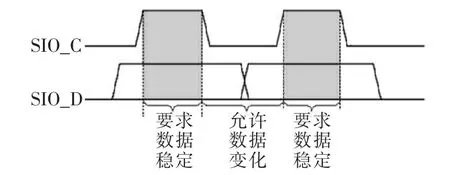

SCCB总线进行数据传送时,SIO_C为高电平期间,SIO_D上的数据必须保持稳定,只有在SIO_C为低电平期间,SIO_D的高低电平状态才允许变化。其时序图如图6所示。

图6 SCCB数据传输有效图

2 模块设计

基于FPGA通过SCCB总线对OV7670初始化就是对摄像头的寄存器进行配置,使其按照设定的输出要求进行数据输出[5]。摄像头寄存器配置流程图如图7所示。SCCB控制模块分为3个子模块:分频器、SCCB状态控制模块、数据查找表。这几个模块都是在QuartusII环境中用Verilog设计完成的。下面分别介绍这3个子模块。

图7 摄像头寄存器配置流程图

2.1 分频器

由于系统时钟频率与SCCB控制模块的数据传输频率不一致,因此要对系统时钟进行分频达到SCCB总线模块SIO_C的频率,并且通过调整分频模块中的分频系数来进行更换[6]。

2.2 SCCB状态控制模块

FPGA作为SCCB的主机,SCCB状态控制模块采用同步状态机的设计方法来模拟SCCB的写时序,从而完成对传感器寄存器的配置。

2.3 数据查找表

将需要配置的传感器寄存器地址和寄存器的配置数据都存放在数据查找表中,根据SCCB的时序规范顺序送给SCCB状态控制模块。

3 硬件实现及仿真

硬件调试工作所选用的FPGA是Altera公司FPGA芯片,Verilog综合及仿真平台是QUARTUSII13.0。将本实例中所设计的SCCB控制模块的Verilog源代码通过QuartusII编译后,并在QuartusII环境下编写TestBench文件,从而利用与Modelsim的无缝链接对SCCB总线模块进行功能仿真。仿真波形如图8所示,可以明确看出:当SIO_C位高时SIO_D由高变低时表明开始位;经过8位传感器地址位、1位Don′t care、8位寄存器地址位、1位Don′t care、8位寄存器配置数据、1位 Don′t care的数据传输;当SIO_C位高时SIO_D由低变高时表明结束,其时序符合SCCB总线时序规范。

图8 仿真波形图

4 结论

本文利用FPGA模拟SCCB总线的时序对OmniVision图像传感器的寄存器进行配置,使其可以按照特定的要求进行图像输出。该设计对OV系列的传感器具有通用性,对图像采集前端的设计具有重要意义。

[1]方彩婷,叶盛,汪雪峰,等.基于FPGA的数字高清 CMOS遥感成像技术[J].电子技术应用,2015,41(4):43-45.

[2]苑玮琦,汤永华.OmniVision图像传感器的SCCB总线协议在DSP中的实现[J].仪器仪表学报,2006(z2):1687-1688.

[3]OmniVision Serial Camera Control Bus(SCCB)Functional Specification,Document Version;2.1[Z].www.vot.com.

[4]张欢,汪红,王芳芳.基于FPGA的实时图像处理实验平台设计[J].微型机与应用,2014,33(11):26-28.

[5]杨光耀.基于FPGA的图像采集及处理系统设计[D].呼和浩特:内蒙古大学,2014.

[6]陈景,李建华.基于FPGA的I2C读写控制器的设计与实现[J].自动化技术与应用,2010,29(2):86-88.

The implementation of SCCB bus of OmniVision image sensor based on FPGA

Wang Shuiyu,Wang Xin

(School of Automation and Information Engineering,Xi′an University of Technology,Xi′an 710001,China)

Based on the FPGA chip of Atera company,do the preparatory work before the image acquisition of OmniVision image sensor.Through the GPIO port of FPGA analog SCCB(serial camera control bus)bus protocol to configure sensor registers,so as to complete the initialization of the sensor,and make the camera normally operate.

FPGA;OmniVision image sensor;SCCB

TP336

A

1674-7720(2015)20-0031-02

王水鱼,王欣.基于FPGA实现OmniVision图像传感器的SCCB总线协议[J].微型机与应用,2015,34(20):31-32,35.

2015-07-29)

王水鱼(1958-),男,硕士,副教授,主要研究方向:信号采集系统与电子测量。

王欣(1988-),女,硕士研究生,主要研究方向:信号采集系统与电子测量。