DNxHD视频编码的码率控制算法及其FPGA实现

薛炜澎,肖铁军,喻金华

(江苏大学 计算机科学与通信工程学院,江苏 镇江 212013)

DNxHD视频编码的码率控制算法及其FPGA实现

薛炜澎,肖铁军,喻金华

(江苏大学 计算机科学与通信工程学院,江苏 镇江 212013)

码率控制是视频编码中的关键问题,而码率控制实质上是对给定码率要求下的率失真进行优化的问题。为了满足高速场合实时性需求,采用流水线结构,以及运算器时分复用策略,改进了DNxHD编码的码率控制算法,以使其适合在FPGA上实现。实验结果表明,该算法在FPGA上运行稳定,并有较好的码率控制效果。

DNxHD;FPGA;码率控制;流水线

Avid DNxHD(Digital Nonlinear Extensible High Definition)是由艾维德公司独立开发的高清视频压缩编码算法,主要应用于广电行业后期制作。2009年4月,国际SMPTE(Society of Motion Picture and Television Engineers)协会正式将DNxHD编码确定为VC-3(Video Compression)标准的基础格式[1],推动了高清后期制作和高清广播电视发展的行业标准化。与摄像机输出的原始数据相比,DNxHD占用的带宽和存储资源更少,使得在高清节目制作中用网络化的环境来取代线性编辑流程成为可能;与其他编码标准相比,DNxHD拥有解码后更好的画质。

目前包括中央电视台在内的众多国内外电视台将DNxHD用于后期高清节目后期制作。由于高清视频原始数据量大,直接进行记录是不现实的,因此在大部分情况下摄像机采集后记录在硬盘或磁带上的视频素材是经过压缩的,若摄像机的压缩格式与后期处理的压缩格式不同,则在后期处理之前还要经过一个解码再编码的过程,这个过程无疑会造成数据丢失。为制作出图像更精美的视频节目,有必要保持前端与后端码流的一致性,这就需要一种能够便携、实时进行DNxHD编码的解决方案。由于专业领域不同于民用领域,目前市场上没有针对DNxHD编码的专用芯片。随着技术的发展,图像传感器的分辨率越来越高,基于单片机的方案对于高分辨率视频数据无法满足实时处理的要求。FPGA(Field-Programmable Gate Array)由于其自身的特点适合进行视频相关的处理,目前国外有厂商推出了采用FPGA实现DNxHD编码功能的知识产权核[2],但其硬件实现处于技术封锁状态;国内针对这方面的研究才刚刚起步。因此研究DNxHD编码的FPGA实现具有一定意义。本文主要对DNxHD编码算法中的码率控制算法[3]进行了研究和改进从而适合在FPGA上实现。

1 码率控制算法

在编码过程中,若连续多帧图像的输出比特数总大于期望比特数,会导致不必要的跳帧;相反,若连续多帧图像的输出比特数总小于期望比特数,既浪费信道传输带宽又可能导致缓冲区下溢[4]。

一幅待压缩的图像被分成N个编码单元,对N个编码单元中的系数进行离散余弦变换和量化;使用量化参数Qi量化之后的数据进行编码得出的码率为Ri,编码数据在解码端数据重建与原始数据之间存在失真Di,假设一帧中所有的编码单元的失真Di具有可加性,则整幅图像的失真可表示为[5]

整幅图像编码后的码率可表示为[6]

给定码率限制的码率控制的目的是在满足码率要求的前提下达到失真最小,即

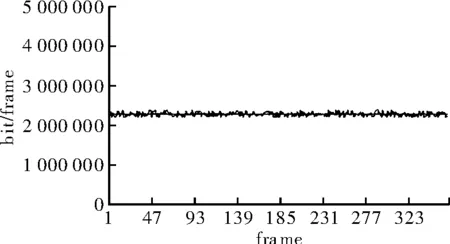

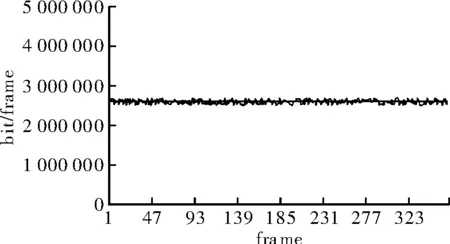

minDtotal{Rtotal 针对像这样受限的优化问题有一个解决方法,即拉格朗日算子优化法[7],即该问题等同于式(4)最小 J=Rtotal+λDtotal (1) 而对于式(1)的最小化问题可归结为每个编码单元的最小化问题,即对每一个编码单元找到一个Qi使得式(2)最小 (2) 但拉格朗日算子优化法只给出了针对固定的λ的优化方法,并未给出λ的产生方式,在DNxHD编码中通过二分搜索来产生合适的λ[8]。 1.1 基于二分法的率失真截取 根据信息率失真理论D(R)对R具有非负性和严格下凸性[9],图1中标注的即为率失真曲线。 图1 率失真曲线 如图连接点P1、P2求出直线斜率λ,以λ为算子进行拉格朗日算子优化,得到新的点P3(R3,D3),根据拉格朗日定理可知这一点也在率失真曲线上[10],如图R3 1.2 压缩后率失真优化 为实现正确的二分搜索,需接近理论值的率失真曲线。在DNxHD编码算法中,每个编码单元在不同的编码参数下的码率通过编码进行准确计算,失真则是利用如式(3)的失真模型[11]进行估计,其中χ为失真模型参数,Dmin、Rmax为率失真曲线最接近R轴的点的坐标值,Dmax、Rmin为率失真曲线最接近D轴的点的坐标值 (3) 1.3AvidDNxHD中的码率控制过程 AvidDNxHD编码算法中的码率控制算法步骤如下: 步骤1 使用1~128之间为2的整数次幂的量化值进行编码,并计算其对应的编码消耗Rtotal。 步骤2 将得出的编码消耗与编码消耗上限Rbudget进行比较,得出编码消耗与Rbudget最接近的量化值,并计算该量化值与前后量化值的几何平均值作为新的量化值Qi_new。 步骤3 使用插值计算估计Qi_new的编码消耗。 步骤4 进行压缩后率失真优化,为每一个编码单元分配编码参数。 步骤5 根据编码参数进行编码并监控缓冲区,若溢出转步骤6,若一帧编码结束不溢出则结束。 步骤6 使用Qi_new进行编码,计算准确的编码消耗,转步骤4。 DNxHD视频编码的码率控制算法中的一些策略不适合FPGA实现,本文结合FPGA特点作出一些改进,使其在不影响编码效果的前提下适合FPGA实现。 在原算法中的步骤3使用插值计算估计两个Qi_new的编码消耗,步骤5中若缓冲区溢出转至步骤6进行编码计算准确的编码消耗,这样做的目的是减少计算实际编码消耗的次数从而提高算法执行速度。但对FPGA而言,这样的策略不仅无法提高算法执行速度,还会导致资源消耗的增多。因此,在计算二的整数次幂的编码消耗的同时计算非二的整数次幂的编码消耗,作为输入进行率失真优化,若编码过程中缓冲区溢出则弃帧从而避免了不必要的系统延迟。改进后的算法不进行编码消耗估计值的计算,节约了FPGA资源,由于使用的是编码消耗的准确值,与使用估计值相比率失真曲线的准确度更高,从而率失真优化能得到更好的结果。 算法中涉及大量的乘法和除法运算,乘法器和除法器会消耗大量的FPGA资源,由于一些运算在进行时间上没有重叠,对乘法器和除法器进行时分复用节约FPGA资源。 设计在Xilinx公司的ISE14.4软件环境下,使用VerilogHDL对码率控制电路进行描述,并以Xilinx公司XC7K160T-1FFG676为核心芯片的Kintex7FPGA开发板对其进行了硬件实现及功能验证,其中虚线框内为码率控制部分。 图2 验证系统框图 SDI(Serial Digital Interface)信号经过解串解扰得到YCbCr4∶2∶2的视频数据,视频数据经过宏块划分模块、离散余弦变换模块、量化模块、Zigzag扫描模块和码率计算模块的处理后得到各量化等级下的码率,作为码率控制模块的输入进行计算得出最优的编码参数,控制编码模块进行编码,经过码流打包模块实现视频编码输出。 整个码率控制部分可分为4个模块:次值计算模块、拉格朗日优化模块和控制模块。 为了加快算法的执行速度,在拉格朗日优化模块中采用流水线结构。流水线各级间相互独立,处理完数据后可立即接受下一个数据进行处理,由此提高系统处理数据的速度。 (1)次值计算模块。次值计算模块以前一次拉格朗日优化计算的得出的码率和失真作为输入,计算出的结果作为下一次拉格朗日优化计算的参数,通过不断的迭代实现码率和失真的优化。其中乘法器和除法器分别采用Xilinx公司的IP(Intellectual Property)核来实现,其中乘法器与除法器与其他模块时分复用。次值计算模块的结构如图3所示。 图3 次值计算模块结构图 (2)拉格朗日优化模块。拉格朗日优化模块由拉格朗日算子计算模块和十输入最小值滤波两部分组成。 在原算法中涉及平方运算,在FPGA中实现时通过预先计算出平方值来减少不必要的资源消耗。拉格朗日计算模块结构如图4所示。 图4 拉格朗日计算模块结构图 在完成拉格朗日计算后对其计算结果进行最小值滤波,模块中的十输入最小值滤波有两个五输入最小值滤波和一个二输入最小值滤波组成,经两个时钟可得出结果,十输入最小值滤波结构如图。最小值所对应的编码参数就是使得这个宏块失真最小的编码方案。 模块采用5级流水线,需5个时钟,能得到源源不断的编码参数。流水线结构如图5所示。 图5 十输入最小值滤波模块结构图 图6 流水线结构图 (3)控制模块。控制模块实现对码率控制算法执行流程的控制,使用状态机实现。状态机接收到模块外部送来的码率控制起始信号后开始状态机的运转,首先进入次值计算状态,通过次值计算模块计算出一个拉格朗日算子,状态机判断到计算完成信号后跳转到拉格朗日优化状态,通过拉格朗日优化模块进行拉格朗日优化,计算完成后跳转至二分比较状态,比较拉格朗日优化后与期望的码率和失真值实现,若与期望值足够接近则码率控制完成,否则进入次值计算开始新一次的优化。 实验使用视频播放盒输出1080i50制式的HDMI视频信号,视频信号转换器转换成SDI信号,通过SDI接口输入给搭载一片Xilinx公司XC7K160T-1FFG676 FPGA芯片的开发板进行编码,通过Chipscope捕捉数据,整个实验平台如图。 针对1080i50制式的视频,设置编码器输出码率为17 269 kbit·s-1,通过FPGA对每一帧的码率进行统计,使用Chipscope捕捉连续400帧的码率,结果如图7和图8所示。 图7 试验平台 图8 试验平台连接示意图 通过使用细节较丰富的视频数据如电影《Chinese Zodiac》中森林片段和细节信息相对较少的视频数据如《Life of Pi》中大海片段进行测试,如图9和图10所示,无论图像细节是否丰富,每帧码率在2 500 000 bit/frame附近波动,通过使用电影片段、演唱会视频、纪录片片段和运动会视频等大量视频数据进行测试,压缩后码率在14 648~18 310 kbit·s-1范围输出,证明该设计可有效控制码率。 图9 视频Life of Pi码率输出情况 图10 视频Chinese Zodiac码率输出情况 DNxHD编码算法广泛应用于广电行业后期制作中,但由于其算法复杂性,绝大部分应用集中在PC机上,而由于前端拍摄与后期处理所使用的编码不一致会导致数据丢失。本文研究了基于FPGA的DNxHD编码算法,不但能够满足高速场景下的实时性要求而且保持从前端到后端编码的一致性,避免了数据损失。对结合FPGA特点算法进行了改进,软件算法中先使用插值计算出编码消耗的估计值,若估计值不能达到良好控制效果再通过编码计算出编码消耗的实际值,这种策略对FPGA来说不仅无法加快算法的执行速度还会造成资源的浪费,因此本设计结合FPGA的特点,在码率控制之前就计算出编码消耗的实际值,在保证算法正确的同时加快算法执行速度;采用了流水线结构提高系统运行效率;同时采用了运算器时分复用的策略,节省资源。实验结果表明码率得到了控制并运行稳定。 [1] The Society of Motion Picture and Television Engineer.SMPTE 2019-1-2008,VC-3 Picture Compression and Data Stream Format [S].America:SMPTE,2008. [2] Antonio Ortega,Kannan Ramchan dran.Rate-distortion methods for image and video compression[J].IEEE Signal Processing,1998,11(8):23-50. [3] LI Xiang.Laplace distribution based lagrangian rate distortion optimization for hybrid video coding[J].IEEE Signal Processing,2009,11(3):118-143. [4] Yang Enhui.Distortion program-size complexity with respect to a fidelity criterion and rate distortion function[J].IEEE Transactions on Information Theory,1997,7(13):688-703. [5] Taubman D.High performance scalable image compre ssion with EBCOT[J].IEEE Transactions on Image Processing,2000,9(7):344-348. [6] Hu Sudeng,Wang Hanli.Rate control optimization for temporal-layer scalable video coding[J].IEEE Transactions on Circuits and System for Video Technology,2011,21(8):1152-1162. [7] Cho Yongjin,Liu Jiaying,Do-Kyoung Kwon,et al.H.264/SVC temporal bit allocation with depend ent distortion model[C].Teipei,Taiwan:Proceeding of International Conference on Acoustics,Speech and Signal Processing(ICASSP),2009. [8] Santosh Sanjeevannanavar.Efficient design and FPGA Implementation of JPEG Encoder using Verilog HDL[J].IEEE Transactions on Image Processing,2011,2(11):584-588. [9] Pradeepthi T.Pipelined architecture of 2D-DCT,Quantization and zigzag process for jpeg image compression using VHDL[J].International Journal of VLSI Desi gn& Communication Systems,2011,2(3):99-110. [10]Lain E G Richardson.Video codec design[M].England:John Wiley&Sons Ltd,2002. [11]刘庆,陈金强.基于FPGA的高速二维DCT变换的研究与实现[J].计算机工程与科学,2012,34(3):103-107. FPGA Implementation of Rate Control Algorithm for DNxHD Video Codec XUE Weipeng,XIAO Tiejun,YU Jinhua (School of Computer Science and Communication Engineering,Jiangsu University,Zhenjiang 212013,China) Rate control is the key problem in video codec.In essence,it is rate distortion optimization under the constraint of a given rate.In order to meet high-speed applications,the DNxHDcodec rate control algorithm was designed and implemented on the platform of Kintex7 Xilinx FPGA.This design takes the advantage of the pipeline structure and time division multiplexing strategy.The experiment result shows that the design gains good control result and runs stable on FPGA. DNxHD;FPGA;rate control;pipeline 2014- 09- 02 薛炜澎(1990—),男,硕士研究生。研究方向:FPGA图像处理。E-mail:824478757@qq.com。肖铁军(1963—),男,教授,硕士生导师。研究方向:嵌入式。喻金华(1984—),男,硕士。研究方向:FPGA视频音频处理。 10.16180/j.cnki.issn1007-7820.2015.04.013 TN919.3+1 A 1007-7820(2015)04-046-05

2 改进的码率控制算法

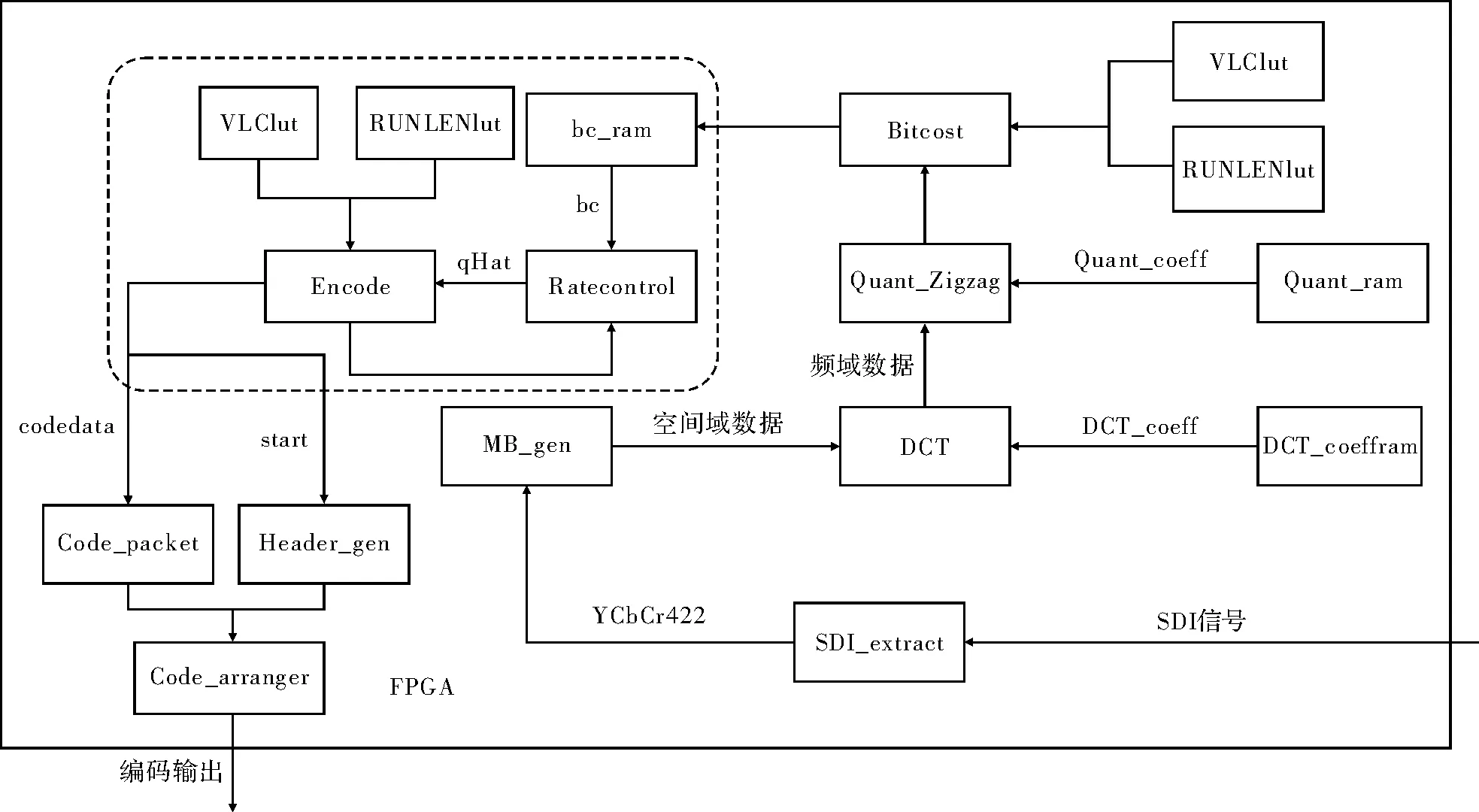

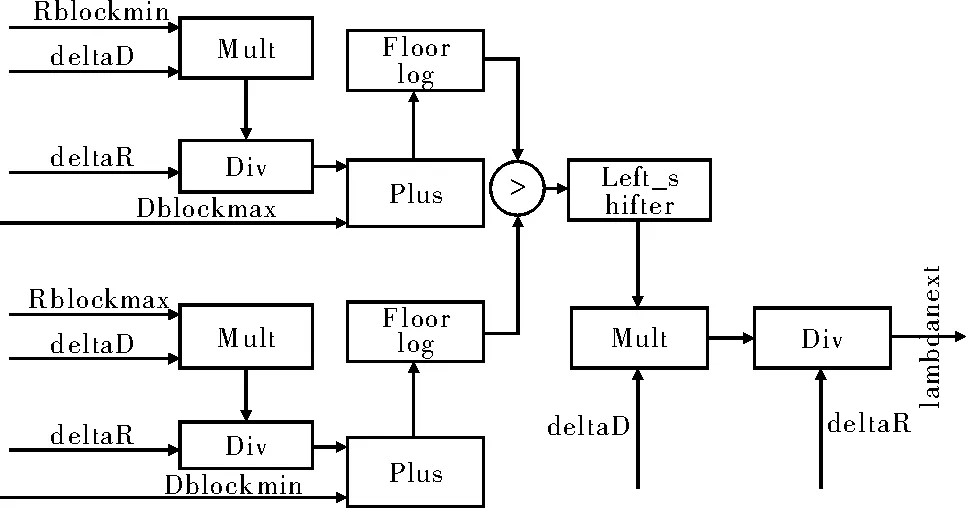

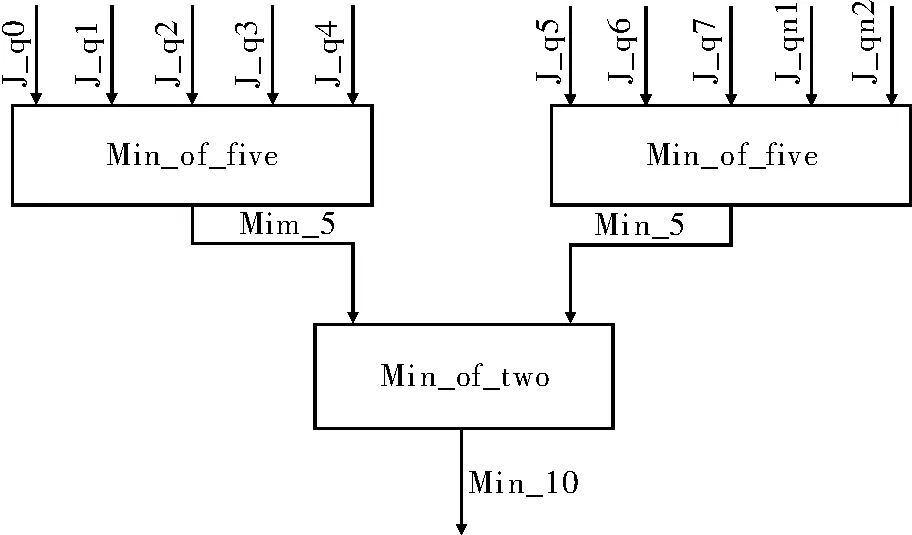

3 码率控制算法的FPGA实现

4 实验结果与分析

5 结束语