Design of High-Speed Acquisition and Storage System Based on FPGA

REN Yongfeng,ZHANG Kaihua,CHENG Hailiang

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China; 2.The Vehicle Research Institute of Aerospace Long March,Beijing 100076,China)

Design of High-Speed Acquisition and Storage System Based on FPGA

REN Yongfeng1*,ZHANG Kaihua1,CHENG Hailiang2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China; 2.The Vehicle Research Institute of Aerospace Long March,Beijing 100076,China)

For the mission of aircraft to identify the external environment and record the parameters,a method of the high-speed data acquisition and storage solutions was proposed based on FPGA.Through the reasonable circuit design of the AD9254,realized the high-speed acquisition of the video signal,the sampling rate is 132 Msample/s.Correcting the logic control of FPGA by the use of static simulation,and the problem of wrong data caused by the distortion clock in FPGA was solved.Two-stage pipeline of operation would be used at the storage of data,it can be written at a speed of 62 Mbyte/s.This system has been tested successfully in an engineering practice with high reliability and stability.

high speed data acquisition;video signal;static simulation;logic control;data storage

高速数据采集系统主要是针对视频图像信号的高速采集和数据存储。采集记录装置应用于飞行器在特定飞行状态下对视频信号的采集和记录,可以完成模拟信号的采样和采样数据的保存系统,属于采集存储测试领域和高速固态记录器的研究范畴[1]。

1 方案设计

采集记录装置由采编器、存储器及传输电缆共同组成。采编器在配套地面测试台控制信号(S1、S2、S3、S4)的控制下,负责I、Q通道视频信号的高速采集、转换,数字量信息包括时间参数等经FPGA编码后由LVDS传送至存储器存储。设计采用14位ADC,高8位进行采样,采样速率为132 Msample/s,精度为0.4%。高速的数据采集能力对数据存储提出了较高要求。存储器接收LVDS传输的高速数据流,经接口电路还原,优化,解串后通过FPGA逻辑控制存入FLASH芯片,存储器容量为8 Gbyte,存储速度为62 Mbyte/s,其外壳采用高强度,抗过载的合金钢,确保飞行器落地后能够有效回收,采编器不进行回收处理[2]。方案设计原理框图如图1所示。

2 高速数据采集电路设计

根据采编器的功能需求,主处理器选用FPGA,可有效实现对ADC采集数据的接收、分组及编码。选用ADI公司的AD9254芯片[3],该芯片具有单通道模拟输入,14位数字输出,采用外部时钟源,最大时钟频率为150 MHz,有模拟和数字电源引脚,是一种低功耗器件。

图1 方案设计原理框图

采编器接收模拟信号,其输入形式可以采取以下几种:

(1)单端输入,模拟信号经阻抗匹配、滤波加载到ADC输入正极,正负极同时配置直流工作在AVDD/2。其优点是节约设计成本,缺点是不能抑制共模噪声,不能对输入信号幅度进行缩放。

(2)运放配置成差分输入,模拟信号采用差分输入形式,通过前端运放把单路信号转换成差分信号,经阻抗匹配、滤波后传送给ADC,共模电压同样配置成AVDD/2。其优点是采用差分输入形式,有效抑制了共模噪声的影响;若采用倍数可调的运放还可以增大输入信号的幅度范围;缺点是运放在放大信号的同时也放大了噪声。

(3)射频变压器配置成差分输入,前端通过变压器把单路信号转换成差分信号,匹配滤波后传送给ADC,共模电压同样配置成AVDD/2。优点是采用差分输入,有效抑制了共模噪声的影响,不会影响ADC的性能参数,且电路简单。缺点是不能对输入信号幅度进行缩放。

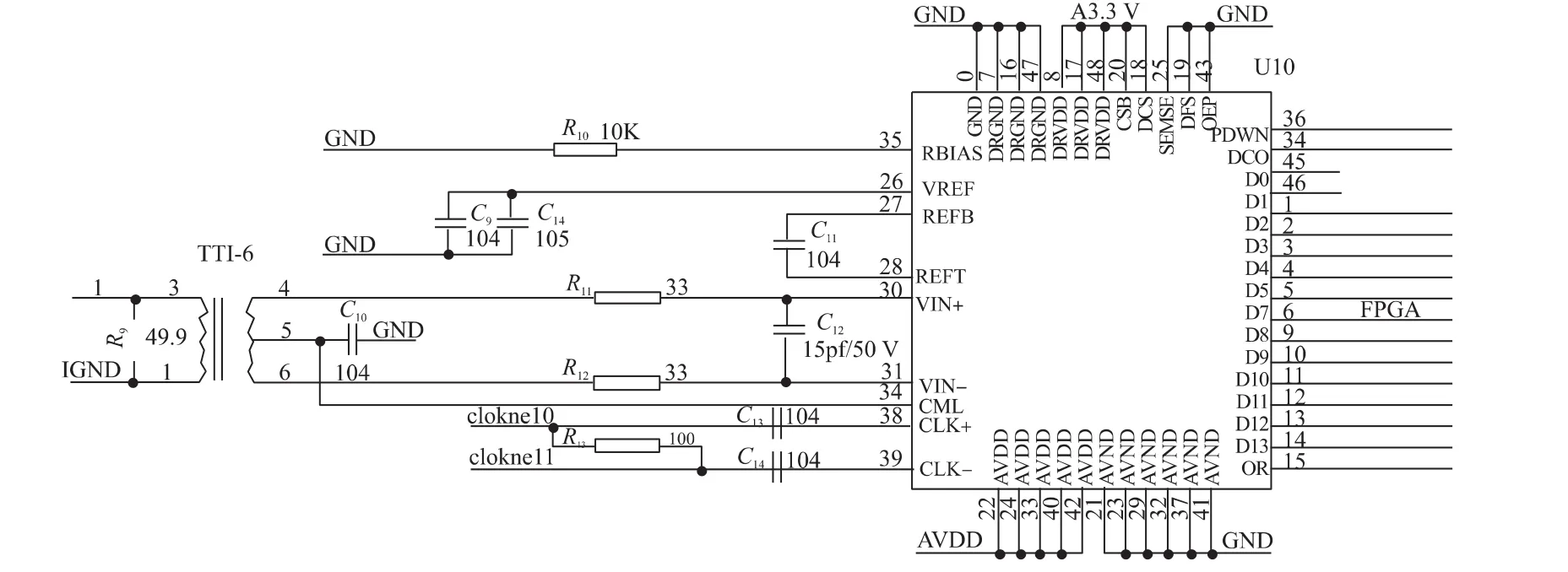

经上述3种方式综合比较,选用电路简单,性能稳定的射频变压器配置成差分信号输入方式。采集通道I、Q均采用一片AD9254实现,设计电路图如图2所示:clocknet0、cloclknet1为外部时钟差分信号。

影响ADC数据采集的因素除了模拟信号的输入外还有时钟输入。采集过程需要保证FPGA接收采样数据时钟和两路ADC进行模数转换的时钟一致,为此采用时钟管理芯片AD9513。该款芯片具有多种电平模式及多路输出接口,并且具有极低的时钟抖动性能,有助于提高系统稳定性。采集电路时钟信号由地面测试台提供,经电气隔离及滤波传送给AD9513,AD9513将时钟信号一分为三,同时提供给FPGA和两片AD9254。FPGA再在S1~S4信号的控制下将数字量数据缓存、分组、编码后发送至存储器存储。

图2 视频信号输入接口电路

3 逻辑控制

采编器采集模块主要功能是数据的接收、分组、编码及输出。FPGA需要完成对ADC采集数据的缓存和读取,由于ADC采用高8位传送数据,系统每周期采样时间为30 μs,传送数据量为3 960 byte,设计采用4 kbyte FIFO实现,写FIFO的时钟与数据接收时钟一致为132 MHz,读FIFO时钟为采编器提供124 MHz,采用8位数据写入,8位数据读出的方式,读取时间为31.9 μs,满足下一周期采集数据到来之前将FIFO中的数据全部读取。

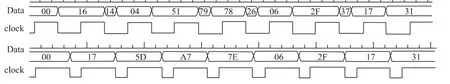

采用上述方案对视频模拟信号进行采集,回读存储器数据后发现数据文件中有个别字节的误码出现,通过ChipScope Pro对写FIFO内部时钟信号和数据信号进行观测,如图3所示。

图3中,clock在芯片内部传输时出现占空比失真的情况[4],缩短了数据建立的时间,进而保存了亚稳态期间的数据,因此要对clock添加约束[5],达到优化时钟信号传输质量的目的,同时会增加逻辑用时以及布线用时。为减少地址线操作频率,修改为16位数据写入,8位数据读出的操作方式。调整后的FIFO控制时序如图4、图5所示。

图3 FPGA内部数据和写FIFO内部时钟信号

图4 FIFO写时序

图5 FIFO读时序

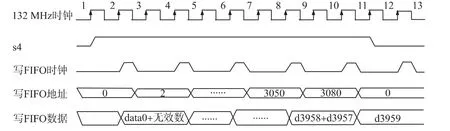

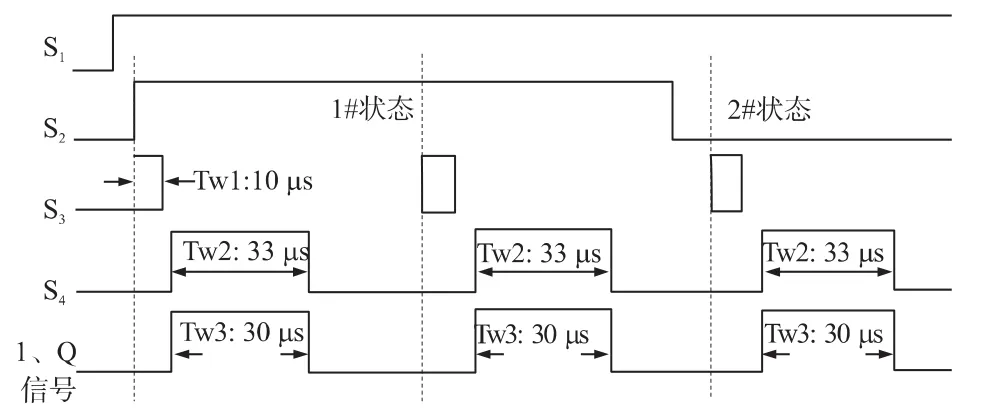

采集模块工作是在S1~S4控制信号的时序配合下进行的,时序同时被编码到数据流中作为帧结构[6]与采集数据一起记录到存储器中,用于数据文件的辨识。视频信号采集的时序关系如图6所示。

图6 信号采集时序关系

采集模块初始为预采集状态,S1为高电平时启动视频信号采集。采集状态显示为1#状态和2#状态,当S2为高电平时处于1#状态,为低电平时处于2#状态。S3信号同步每周期采样的起始时刻。FPGA检测到S4的上升沿时刻开始接收ADC芯片输出的数据,采样时间保持30 μs。FPGA将每周期采样数据编为一帧,并在尾部加入帧结构,内容代表S1~S4信号的时间参数。

4 数据高速存储

数据存储部分设计双存储器分别用来存储I、Q路的采集数据,为保证数据的高速存储,每个存储器都包含两片Flash芯片[7],存储方式采用二级流水线操作,这种操作方式是将一条指令分解成若干步骤,每个步骤的响应在时间上是相互重叠的,可以在同一时刻执行多条指令,显著加快指令的响应时间。两片Flash芯片存储的FPGA内部逻辑框图如图7所示。

图7 存储器FPGA内部逻辑框图

在时序控制信号S4的控制下,存储器将接收的数据分组,交替写入FIFO1#和FIFO2#,在写Flash1#的同时完成FIFO2#的缓存,在写Flash2#的同时完成FIFO1#的缓存,存储速度提高两倍。单片Flash操作采用典型的双片选交替双平面编程的方式[8],写入速度约为30.9 Mbyte/s,单个存储器存储速度约为62 Mbyte/s。

5 实验结果

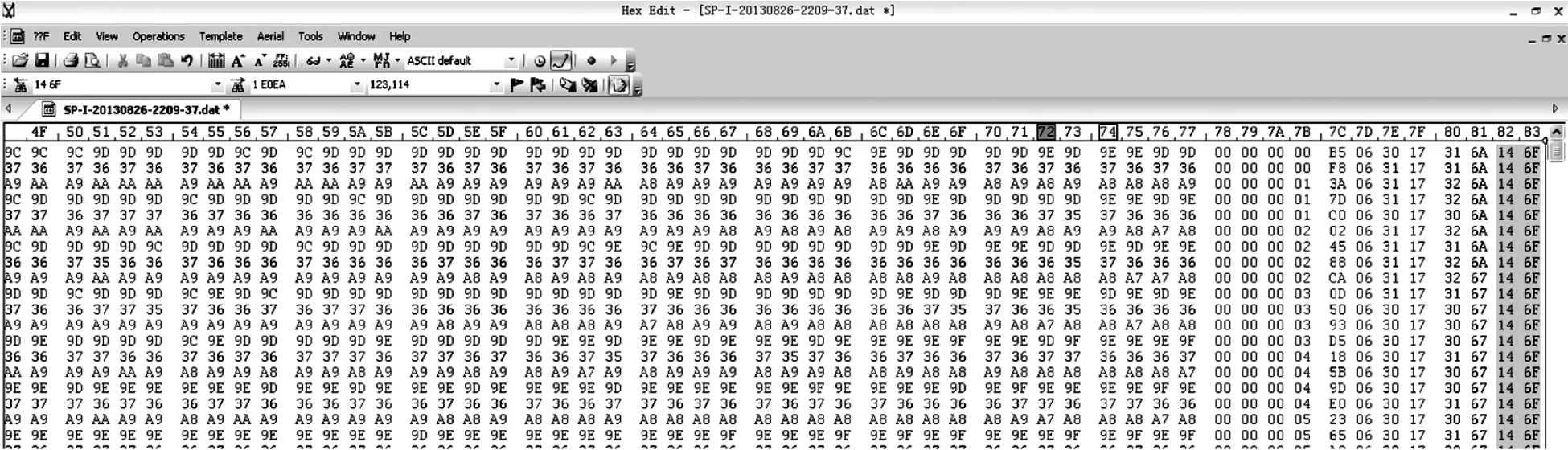

视频信号采集记录装置应用于弹上工作系统,主要完成对脉冲信号的采集存储,在试验阶段利用I、Q路通道同时采集由信号源产生的正弦信号,经高速数据采集电路存储在记录器中,将记录器中的数据由上位机软件回收,得到数据文件SP-I-20130826-2209-37.dat,如图8所示。

图8 正弦信号回收数据

观察数据帧格式正确,操作软件对该数据文件进行分析并绘制图形如图9(a)所示,为采集到的正弦信号波形图,观察图形波形稳定,采集无异常。图9(b)所示为针对飞行器在实际环境对脉冲信号的采集、存储后的数据还原图形,满足采集记录装置对脉冲信号的采集要求,I、Q路信号相位一致性良好。

图9

6 结论

目前,飞行器在军事领域的发展越来越快,在飞行试验中需要采集和记录的数据量也越来越大,对采集记录装置的数据采集速度和存储速度提出了较高要求,基于FPGA的高速数据采集记录系统在这样的环境下应运而生,经过完整的地面联试试验,该系统已成功应用于测试项目,圆满完成任务,验证了其设计的优越性和可靠性,具有广泛深远的应用和研究价值。

[1]焦亚涛,李娜娜.一种高速固态存储系统的设计与实现[J].电测与仪表,2011,48(11):76-79.

[2]宋丹,任勇峰,姚宗.一种低功耗水下多通道实时采集存储装置的设计[J].电子器件,2013,36(4):502-505.

[3]李永丽.多通道高速数据采集及大容量存储系统设计[D].西安电子科技大学,2009.

[4]周海斌.静态时序分析在高速FPGA设计中的应用[J].电子工程师,2005,31(11):41-44.

[5]林昌辉,樊晓桠.FPGA设计中优化时序的原则与方法[J].微处理机,2007(3):6-13.

[6]储成群.基于LVDS接口的高速数据记录器的设计[D].中北大学,2011.

[7]舒文丽,吴云峰,孙长胜.基于NAND Flash的海量存储器的设计[J].电子器件,2012,35(1):107-110.

[8]郭小兵,李圣昆,贾兴中.基于弹载存储系统的高速固态数据记录器设计[J].微电子学与计算机,2013,30(2):25-28.

张凯华(1991-),男,汉族,山西临汾人,中北大学测试计量技术及仪器专业在读硕士研究生,研究方向为电子测试仪器与系统,kai.hua2008@163.com;

任勇峰(1968-),男,汉族,山西中阳人,教授,博士生导师,主要从事弹载固态记录器和自动测控台等方向的研究工作。

EEACC:7210G10.3969/j.issn.1005-9490.2015.01.029

基于FPGA的高速数据采集存储系统设计

任勇峰1*,张凯华1,程海亮2

(1.电子测试技术国家重点实验室,中北大学,太原030051;2.北京航天长征飞行器研究所,北京100076)

针对飞行器在飞行状态下需要对外部环境进行识别和参数记录任务,提出基于FPGA的高速数据采集存储方案。通过对AD9254芯片前端电路进行合理设计,实现其对视频信号的高速采集,采样速率为132 Msample/s。利用FPGA静态仿真实现逻辑控制的修正,解决了因内部时钟传输占空比失真而导致误码产生的问题。数据存储采用二级流水线的操作方式,写速率可达62 Mbyte/s。系统设备经地面联试试验已成功应用于工程实践,具有较高的可靠性和稳定性。

高速数据采集;视频信号;静态仿真;逻辑控制;数据存储

TN92

A文献标识码:1005-9490(2015)01-0135-05

2014-02-19修改日期:2014-03-10

- 电子器件的其它文章

- The Implementation of CRC Algorithm Based on FPGA

- A Bandgap Reference with High Temperature Performance*

- The Relationship between Excessive Leakage Current,Large Thermal Resistance and Voids Rate*

- A Method of Bottleneck Detection of Semiconductor Assembly and Test Production Line*

- Suppression of Spurious Radiation of Patch Antenna Based on Microstrip Spiral-Defected Resonant Cells*

- An Ultra-Wideband Low Noise Amplifier Based on Noise Cancellation Technique*