The Relationship between Excessive Leakage Current,Large Thermal Resistance and Voids Rate*

TAN Xi,PU Niannian,XU Dongmei,CUI Weibing,WANG Lei,ZHU Yupeng,CHAI Yanke,LIU Su*

(1.Institute of Microelectronics of LanZhou university,LanZhou 730000,China;2.Huatianelectroniccompany,TianShui Gansu 741000)

The Relationship between Excessive Leakage Current,Large Thermal Resistance and Voids Rate*

TAN Xi1,PU Niannian1,XU Dongmei2,CUI Weibing2,WANG Lei2,ZHU Yupeng2,CHAI Yanke1,LIU Su1*

(1.Institute of Microelectronics of LanZhou university,LanZhou 730000,China;2.Huatianelectroniccompany,TianShui Gansu 741000)

Commercialized VDMOS failed to meet designed values for many reasons.Usual problems are excessive leakage current and large thermal resistance.Failed VDMOS was characterized using X-RAY,SEM and EDS.The relationship between excessive leakage current,large thermal resistance and voids rate was acquired.The results show leakage current and thermal resistance increase in direct proportion to voids rate when voids rate keeps in a low level,while the ratio changes.We attribute this to different dilatation coefficient and thermal conductivity of each material,as well as low thermal conductivity of air.Moreover,large thermal resistance will facilitate migration of Al and polluted ion,which causes increasing leakage current in turn.

VDMOS;excessive leakage current;large thermal resistance;void rate;X-RAY;SEM;EDS

功率VDMOS器件具有输入阻抗大,开关速度快,驱动电流和损耗小,体积小的诸多优点,近年来,功率VDMOS器件被广泛应用于各类民用、工业、军用产品中。功率VDMOS器件存在塑料、金属、陶瓷、玻璃等封装形式,塑封器件因为体积小、重量轻、结构简单、工艺方便、耐化学腐蚀、电绝缘性好、机械强度高等优点在各类封装形式中所占比例最大。但塑封VDMOS器件在使用中仍存在较多失效,如湿气、分层、划伤、软焊料空洞等造成大漏电,热阻过高等多种失效模式。塑封料器件容易因为诸多原因造成早期失效的缺点限制了其良性率提高和器件的广泛使用,而失效的根源主要包括器件结构设计问题、材料不合适、工艺上的缺陷等。塑封VDMOS失效数据表明,器件大漏电、热阻过高、EAS雪崩测试不良是最主要的3种失效模式。本次研究了塑封VDMOS器件后道工艺的主要流程:切晶→上芯→压焊→塑封→后固化→电镀→编带再测试,并测试了塑封VDMOS器件经后道工艺后漏电流和热阻值的大量数据,发现广泛应用的VDMOS器件中,大漏电和高热阻问题并行出现的几率较大。对后道工艺中存在的各种失效机制进行了研究,最终发现软焊料中空洞率与塑封VDMOS热阻高低和漏电流大小直接相关。整个流程中存在污染、划伤、分层、虚焊、银胶上溢、软焊料空洞等诸多失效机制。

已经有大量研究从器件设计,材料匹配、制造工艺等多方面分析了大漏电和热阻过高的失效机理。关于漏电流过大的成因,李新的研究表明[1]后道工艺中的湿气中含有大量离子玷污物,与芯片键合区甚至与芯片的金属化层发生化学反应会带来漏电流的增大;陆宁的研究表明[2]钝化层质量是产生大漏电的主要原因,钝化层不平整,含有杂质等均将增大漏电流;刘侠的研究通过高温反偏试验提出[3]进入硅表面的二氧化硅薄膜中的杂质离子,在N型掺杂硅中会引起电子的积累,在P型掺杂硅会引起材料表面反型,另外半导体或绝缘体材料中的电子、可动离子等会在电场的作用下有向分布,温度影响漏电流大小;江清明的研究通过对Al通孔试验样品进行高温恒定电流加速电迁移寿命实验,提出高温条件下电迁移寿命会降低、漏电流会增加。关于高热阻问题,广泛存在于软焊料中的空洞是主要影响因素。施建根的研究中提出[4]空洞率过高或存在大型空洞时会引起器件热阻过高;谢鑫鹏的研究表明[5]对于功率器件而言,长期处于功率循环中,界面系统的温度膨胀系数CTE的失配会加速界面疲劳,最终导致软焊料中很小的气泡会有扩散和增大的趋势;唐穗生的研究表明[6]随着空洞率的增加会带来ΔVds增加以及EAS失效。以上研究统计结果表明,从不同角度均有对大漏电、高热阻问题的讨论。然而对于广泛存在的空洞问题是否影响到大漏电、较小空洞率下热阻是否依然受空洞率影响却鲜有研究。本文着重于从测试数据出发分析软焊料中空洞率较小时,VDMOS器件空洞率与大漏电和高热阻问题的相关关系。并解析空洞率改变造成以上问题的主要原因。

1 相关理论

1.1VDMOS器件

VDMOS(Vertical Double-Diffusion Metal-Oxide-Semiconductor)垂直双扩散金属氧化物晶体管,通过平面自对准双扩散制成,以N型沟道为例,其单胞结构图如图1所示。正常工作时,VGS正偏、VDS正偏,在P型区形成导电沟道,电子流向如图中箭头所示。这种结构具有较短沟道,因此栅源开启电压Vth小;具有纵向漏极,故而耐压大。同时,VDMOS器件是由多个图1所示的单胞并联构成。因为这种多单胞的结构,VDMOS的电流较大。

图1 VDMOS单胞结构

1.2软焊料空洞

软焊料空洞普遍存在,主要产生于上芯过程中[7]。通过软焊材料即焊锡材料粘结引线框架和芯片。整个上芯过程中,充斥N2、H2于整个环境中,N2作为惰性气体赶走活性气体,H2还原已被氧化的Cu引线框架。通过电脑程序以及光学和传感系统确定芯片位置,放置好引线框架。通过加热引线框架的同时,使焊锡靠近引线框架,焊锡因高温熔化滴在引线框架中央位置。焊锡融化时,顶针将晶圆上切割好的芯片上顶、真空吸嘴吸住芯片,芯片被放置于熔融的焊锡上,使两者完整粘结。整个上芯过程中,由于焊锡材料中含有挥发性物质,引线框架上氧化物均可在高温条件下挥发,导致在焊锡材料中形成气泡;另外温度控制不合适、放置芯片时力度不够、N2、H2充斥速度过大等均可造成软焊料中空洞。因此,软焊料空洞广泛存在,这种广泛存在的空洞与大漏电和高热阻两种主要失效模式之间的相互关系是此次研究的重要内容。通过X-RAY检测仪对软焊料中空洞率进行分析检测,X-RAY不可以通过软焊料,却可以通过空气。故通过X-RAY可以得出软焊料中空洞几率。

1.3漏电流

正常情况下,对于塑封VDMOS器件,只有当VGS>0,VDS>0时,导电沟道形成,漏源(DS)之间才有可能形成导通电流。当VGS<0或者VDS<0时,DS之间仍存在电流时,或栅源(GS)之间存在电流,当这个电流超过一定范围时,称为漏电流。漏电流又分为栅源漏电流和漏源漏电流。

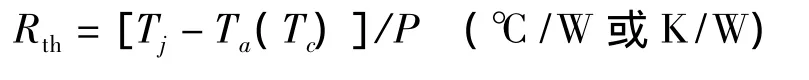

1.4热阻

热阻指的是热流(功率)流过导热体所受到的阻力。定义为器件热流通道上温度差与产生温差的耗散功率的比。

其中T

j

表示结温,T

a

表示环境温度,T

c

表示器件表面壳体温度,P表示耗散功率,分别代表R

thja

和R

thjc

两种类型的热阻。对于器件热的传递包括3种主要形式:热传导、热辐射、热对流。其中热传导约占60%,热对流约占25%~30%,热辐射只占10%~15%。热传导属于R

thjc

的范畴,热辐射与热对流属于R

thja

的范畴。R

thja

与R

thjc

之间的区别如图2(a)所示。

图2 Rthja与Rthjc异同

从测试原理区分,功率VDMOS的热阻分为稳态热阻[8]和瞬态热阻[9]两种。稳态热阻是在提供器件连续脉冲且器件温度达到稳定的条件下测量的,而瞬态脉冲是在提供器件单一脉冲的温度不稳状态下测量的。稳态热阻是考核器件设计对器件性能的影响,而瞬态热阻更多考核工艺对器件可靠性造成的影响。本次研究测试的是瞬态热阻,通过瞬态功率脉冲较为迅速的测试出功率VDMOS器件的热阻,判断出器件散热能力的高低。热阻测试原理如图2(b)所示,通过加瞬态单一脉冲测试等效二极管两端压降DVDS来反应温度变化,等效二极管I-V特性与温度的关系:,则,其中为常数,温度变化ΔT=αΔU,可得出热阻。选择这种方式作为瞬态热阻测试,一方面是因为瞬态温度获取的不方便,更为重要的是体二极管是漏源(DS)一部分,其电压变化可以表征整个DS间电压变化。

2 实验数据采集与分析

从生产工艺出发,采集大量大漏电、高热阻样品的直流参数、热阻、空洞率数据,另外对部分器件进行了SEM和EDS分析检测。对于直流参数采集,使用STA2100测试机,主要关心IDSS和ISGS两个关于漏电流的参数的测试。对于热阻测试,使用DM2000测试机,主要关心Rth这项数据。另外,X-RAY检测仪测试空洞率,SEM拍照观测表面形态,EDS能谱分析检测污染离子聚集。

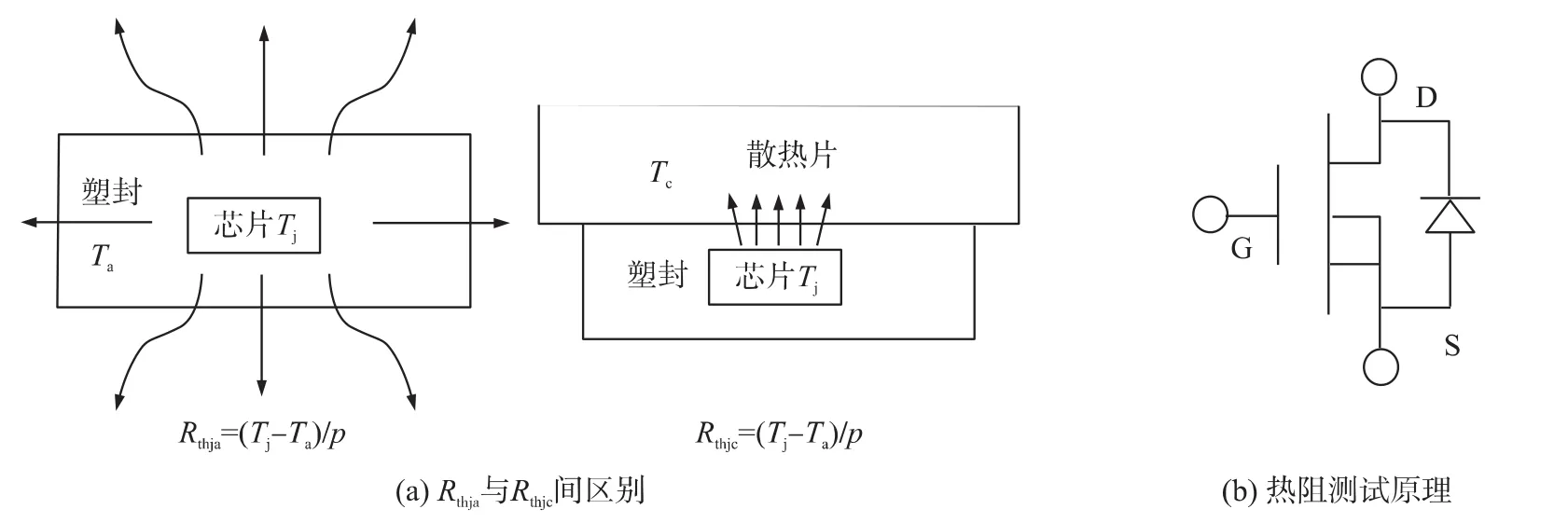

2.1热阻与空洞率

在§1.4中已提到,芯片的3种主要传热方式中热传导约占60%,热对流约占25%~30%,热辐射只占10%~15%。作为主要传热方式的热传导的主要途径是通过软焊料连接芯片和引线框架散热。而空洞正好存在于作为重要连接材料的软焊料中。一般而言,软焊料主要材料为锡铅合金,而锡铅以及Cu引线框架的导热率远高于空气的导热率,具体相关材料的导热系数如表1所示。

表1 300K下锡、铅、铜、硅、空气导热率

由表1可知锡、铅、铜、硅的导热率均远高于空气导热率,故而当软焊料中含有空洞时,空洞将给芯片通过软焊料到Cu引线框架的散热路径带来严重阻碍,数值上的表现即带来热阻值的增大。当软焊料中空洞造成热阻过大,带来散热不良,进一步造成芯片局部高温,高温会进一步造成电流增大,而根据PN结间IV关系,可知电流增大会继续增大器件功耗带来结温上升。在这样的正反馈情形下,器件恶化的几率大大增加。另外一个重要原因,作为功率VDMOS器件,需要长期工作于功率循环中,也加速了I与T之间的正反馈。故判断热阻会随着空洞率的增大而增大。另外因为芯片的3种主要传热方式中热传导约占60%,热对流约占25%~30%,热辐射只占10%~15%。因此空洞率较小时,由于空洞所造成的热传导路径上的阻力可以通过热辐射和热对流得到缓解,故判断空洞率较小时,热阻随空洞率的增长速度远不如空洞率较大时的增长速度。

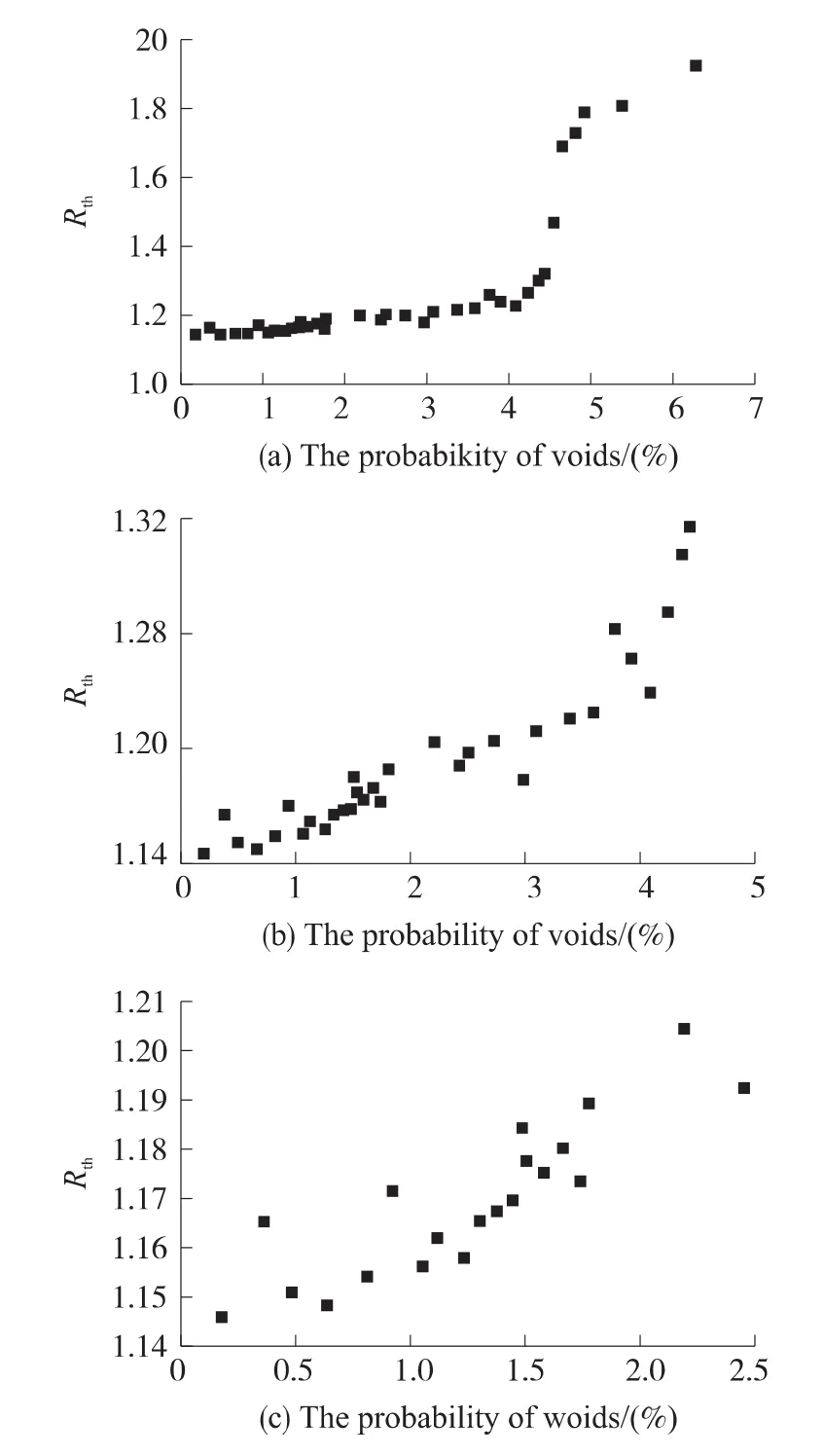

已有研究表明空洞率较大时会引起Rth的增大,本次研究推测不仅空洞率较大对器件热阻有影响,当空洞率较小时,Rth与空洞率之间依然存在正相关关系,只是空洞率越小时Rth随空洞率增长速度不如空洞率大的时候Rth的增长速度,并且空洞率较小时,Rth随着单位空洞率的浮动较大,规律性不强。为验证较小空洞率时,热阻随空洞率变化,选取某产品数据进行拟合,如图3所示。

图3 Rth与空洞率相关关系

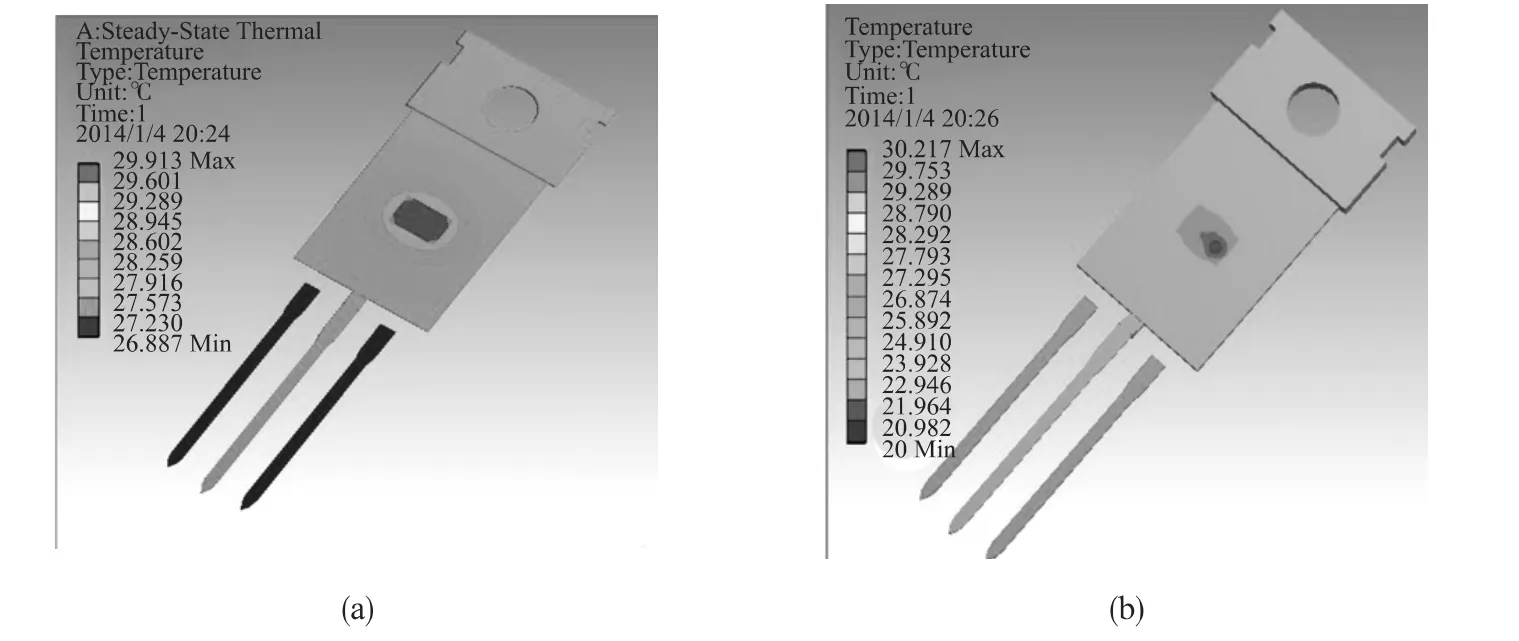

由图3(a)数据拟合结果可知,随着空洞率的增大,Rth呈现增长趋势;但空洞率<4.5%时的Rth增长速度落后于空洞率>4.5时的Rth增长速度。另外,大部分数据点集中在空洞率<4.5%的情形下,因此将空洞率<4.5%范围内,Rth随空洞率增长的趋势进一步作图,将该范围的数据进行拟合,结果如图3(b)所示。由图3(b)可知,空洞率=2.5%前后Rth随空洞率增大的速度有所不同。当空洞率<2.5%时,Rth会在1.14~1.19这个较小的范围变化;而当2.5%<空洞率<4.5%时,Rth会在1.19~1.32之间变化,变化幅度较空洞率<2.5%时进一步增大。所测芯片中,空洞率<2.5%时的芯片占到所有测试样品的52.6%,故进一步将空洞率<2.5%时的,Rth与空洞率之间的相关关系进行拟合,如图3(c)所示。由图3(c)可以看出,虽然Rth随空洞率的变化有一定范围内的浮动,但在空洞率<2.5%这种空洞率特别小的情形下,Rth与空洞率之间仍存在正相关关系。因为上芯过程中压焊温度控制不当、惰性气体注入速度过快、载体氧化物挥发等原因带来的软焊料中的空洞,热阻值体现出随空洞率增长而增长的趋势。热阻值升高是因为空洞存在带来的早期失效,另一方面,功率VDMOS长期处于功率循环中,如果相连材料间温度膨胀系数不同,则长期高温以及功率循环环境下,小型的孔洞也会膨胀扩大,使得器件空洞率上升、大型空洞增加,这必然带来器件热阻值的增加和其他性能的进一步恶化,即由于空洞存在带来的后期失效。芯片、软焊料、Cu引线框架主要材料锡、铅、铜、硅的温度膨胀系数如取自表2所示。

表2 锡、铅、铜、硅、空气温度膨胀系数

由表2可知,锡、铅、铜、硅以及空气间的线膨胀系数相差较大,故长期工作于功率循环下的VDMOS器件,如果存在小型空洞,也是器件潜在的危险。因此由于小型空洞存在给器件早期测试出厂和后期使用中带来极大影响,所以严格控制后道工艺上芯过程中空洞的产生是亟待解决的问题。

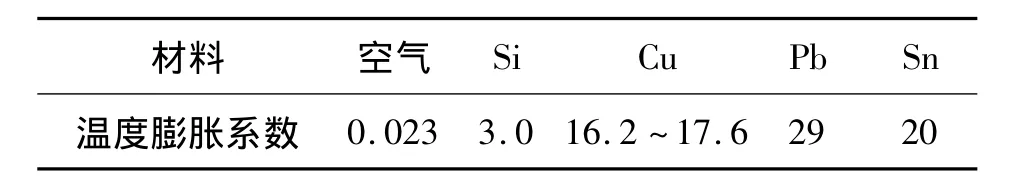

图4 ANSYS热模拟

为直观体现空洞存在给期间带来的工作温度的改变,使用ANSYS热分析软件[10]对含有空洞的不良品与不含空洞的良品进行了热模拟,其模拟结果如图4所示。

由图4可知,空洞的存在将带来器件整体工作温度的升高以及空洞处的温度急剧提升,而这样的不均匀的温度分布以及温度升高即体现在热阻值的升高上。

2.2ISGS、IDSS与空洞率之间关系

引言中已提到大漏电的来源有很多方面,而通过研究得到其主要来源有两方面:可动污染离子运动,Al的电迁移[11]。后道工艺中从切晶到塑封,芯片一直裸露于环境中。切晶到塑封中任意环节工作环境控制不当,去离子水不洁净,原材料不纯净等均将带来离子污染。造成大的漏电流的可动污染离子,随着温度的升高而加剧定向运动,因此推断随着温度的升高,温升较高的地方会聚集可动污染离子带来的漏电流的增大。另一方面,Al的电迁移是指在高温或大电流下的质量输运现象,结果在一定区域形成Al的空洞,一定区域形成Al的堆积。Al的空洞造成开路,Al堆积造成短路。Al的堆积将带来漏电流的增加[12]。而Al电迁移的寿命模型可以用BLACK方程描述:。其中,MTF为电迁移样品寿命,J为电流密度,Ea为激活能,k为波尔兹曼常数,T为绝对温度。由方程可知,随着温度T的增大,器件的电迁移寿命MTF将减小。同时Al质软、机械强度差在工艺中易划伤等特点进一步促进了Al在高温和大电流下的电迁移。由于随着空洞率升高,将导致器件热阻升高,在器件工作过程中会导致芯片散热不良或局部过热,而理论分析,高温环境下应该会带来可动污染离子运动和Al的电迁移加剧造成漏电流增大。因此,推断漏电流与空洞率之间应该存在正相关关系,故将数据拟合如图5所示。

图5 ISGS与空洞率相互关系

由图5数据拟合得到的曲线可知当空洞率较小时,漏电流ISGS、IDSS的大小与空洞率之间亦存在正相关关系。由图5(a)、5(b)可判断出栅源漏电流∝空洞率。并且由图5(a)可知,空洞率=2.5%约为ISGS随空洞率增大速度改变的一个中间点。同时因为空洞率<2.5%的芯片占了整个测试芯片的大部分,因此将空洞率<2.5%条件下,ISGS与空洞率之间进一步拟合,如图5(b)所示。由图5(b)可知,当空洞率较小时,ISGS与空洞率之间也表现为在一定范围内波动增大。因此我们推测空洞率较小时,空洞率的大小也正相关于栅源漏电流ISGS的大小。由图5(c)可知,IDSS也体现出随空洞率增加而增加的趋势,我们仍然可以发现空洞率=2.5%可以作为IDSS随空洞率增大速度的一个分界点。空洞率<2.5%时,IDSS随空洞率的变化如图5(d)所示。综上所述,通过图5,得出随着空洞率的增大,漏电流ISGS、IDSS均会随着空洞率的增加而增加;只是空洞率=2.5%作为分界点,当空洞率<2.5%时漏电流增大速度不如空洞率>2.5%时快。同时对比3.1所得出的Rth与空洞率之间关系发现,随着空洞率的增大,Rth、ISGS、IDSS增长的趋势很相似,均在2.5%前后表现出增长速度不同。随着空洞率增大的增大ISGS、IDSS均会增大,而通过2.1已知空洞的增大会造成Rth增大,散热能力的下降。故判断ISGS、IDSS随空洞率增大的原因主要来自于Rth增大造成的散热能力的下降,结温的升高[13]。

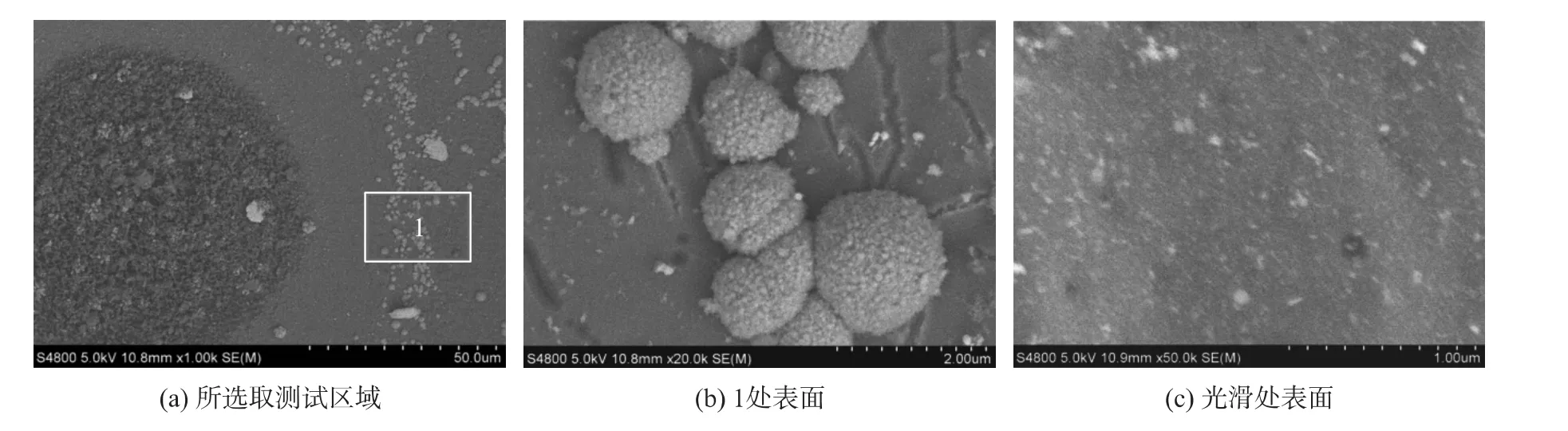

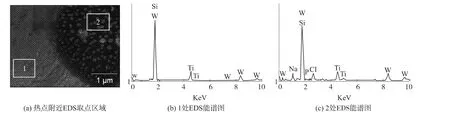

以上研究结果已表明,ISGS、IDSS会随空洞率增大而增大,符合高温带来Al的电迁移和可动污染离子移动的推断。为进一步证明因为空洞存在造成的器件散热不良导致的结温升高,会进一步导致可动污染离子运动加剧,并且Al的电迁移现象也会更明显。所以接下来采取SEM以及EDS观测高温热点周围Al的电迁移和可动污染离子聚集现象。通过SEM观测了存在烧伤热点的芯片的热点及其周围的Al堆积现象。如图6所示。

图6 烧伤热点及其周围Al堆积现象

由图6可知热点周围存在堆积的Al,而不存在热点的其他Al表面较为平整。可见Al会朝着高温区域运动,带来高温区域的Al堆积。存在空洞的VDMOS塑封器件,因为空洞存在,带来热分布不均匀,空洞处温度较高形成小型过热区域,加速此区域的Al堆积,而Al堆积带来的器件性能不良主要体现在直流参数IDSS和IGSS上。关于可动离子污染运动,对热点及其周围区域进行了EDS能谱分析,如图7所示。

图7 热点附近EDS取点区域及EDS能谱图

由以上能谱分析结果可知,烧毁热点处存在Na、P、Cl离子聚集,而在烧毁热点0.5 μm~1 μm的区域已完全检测不到污染离子的存在。软焊料存在的空洞造成塑封VDMOS器件工作时温度分布不均,使得可动污染离子朝着温度较高区域聚集,而可动污染离子浓度在该区域的增高也将引起该区域漏电流的增大。

综上所述,在高温循环工作情形下,小型的空洞也会带来器件温度分布不均,进一步带来高温处Al的电迁移和可动污染离子的堆积,从而增大漏电流。空洞改变漏电流与热阻随空洞变化的规律一致,均可以空洞率<2.5%为分界点,较小空洞率时,其随空洞率增长的趋势较缓慢,而随着空洞率上升,漏电流等增长趋势会增加的更明显。

3 结论与分析

通过直流参数,热阻参数以及X-RAY、SEM、EDS分析检测证明了,当空洞率较小时,热阻依然随空洞率的增加而增加,并且此次研究表明,空洞率=2.5%作为分界点,当空洞率<2.5%时,Rth、ISGS、IDSS随空洞率增大变化较缓慢,而空洞率>2.5%增速较快。推断Rth随着空洞率增加而增加是因为空气导热率远不如锡、铅、铜、硅导热率,而空洞较小时Rth增长速度较慢是因为热传导只是器件散热途径之一,而同时由于锡、铅、铜、硅、空气温度膨胀系数相差甚远,故而小型空洞也会成为功率VDMOS器件的潜在危害。关于漏电流随着空洞率的增长表现出了与Rth随空洞率增长的相同增长趋势,判断漏电流随着空洞率的增长实际上是空洞存在造成器件工作时温度分布不均,引起高温区域Al堆积以及污染离子聚集,最终带来的漏电流的上升。通过此次研究,可知软焊料中空洞的存在严重影响到了器件性能,寻找温度膨胀系数更接近、导热率更高的软焊料,选择较好的芯片背材和控制工艺条件是上芯过程尤其要主要的问题。

[1]李新,周毅,孙承松.塑封微电子器件失效机理研究进展[J].半导体技术,2008,33(2):98-101.

[2]陆宁.关于VDMOS栅源漏电问题的研究[J].电子与封装,2010,10(12):27-31.

[3]刘侠,夏晓娟,孙伟锋.钝化层质量对高压功率器件可靠性的影响[J].固体电子学研究与进展,2009,29(3):465-468.

[4]施建根,孙伟锋,景伟平,等.车载IGBT器件封装装片工艺中空洞的失效研究[J].电子与封装,2010,10(2):23-27.

[5]谢鑫鹏,毕向东,胡俊,等.空洞对功率芯片粘贴焊层热可靠性影响的分析[J].半导体技术,2009,34(10):960-964.

[6]唐穗生.功率MOSFET的封装失效分析[J].电子元器件应用,2008,10(1):78-80.

[7]潘少辉,何伦文,汪礼康,等.VDMOS器件贴片工艺中气泡的形成机制与影响[J].半导体技术,2007,32(5):436-439.

[8]董晨曦,王立新.功率VDMOS稳态热阻测试的关键影响因素[J].电子器件,2013,36(2):143-148.

[9]孙铣.功率器件的瞬态热阻测试[J].中国集成电路,2012 (12):62-66.

[10]华庆,殷景华,焦国芹,等.基于ANSYS的功率VDMOS器件的热分析及优化设计[J].电子器件,2009,32(2):354-356.

[11]陈军,毛昌辉.铝铜互连线电迁移失效的研究[J].稀有金属,2009,33(4):530-530.

[12]万延树.塑料封装可靠性问题浅析[J].电子与封装,2007,7(1):8-13.

[13]Barletta G,Currò G.Junction Leakage Current Degradation under High Temperature Reverse-Bias Stress Induced by Band-Defect-Band Tunnelling in Power VDMOS[J].Microelectronics Reliability,2005,45(5):994-999.

谭稀(1991-),女,兰州大学物理科学与技术学院微电子与固体电子学在读硕士研究生,主要研究方向为半导体器件与集成电路及其相关研究,tanx13@lzu.edu.cn;

刘肃(1953-),男,教授,博士生导师,主要研究方向为半导体器件与集成电路,宽禁带半导体薄膜材料及器件,有机发光器件等。

EEACC:2570F10.3969/j.issn.1005-9490.2015.01.009

功率VDMOS器件漏电流、热阻与软焊料空洞率的关系*

谭稀1,蒲年年1,徐冬梅2,崔卫兵2,王磊2,朱宇鹏2,柴彦科1,刘肃1*

(1.兰州大学微电子研究所,兰州730000;2.华天微电子股份公司,甘肃天水74100)

现在被广泛应用的VDMOS器件存在诸多失效模式,主要表现为直流参数大漏电和热阻过高问题,限制了器件应用。通过对其失效器件进行X-RAY、SEM、EDS分析表征得到相关规律。研究结果表明空洞率相对较小时,漏电流大小、热阻值高低均与空洞率成正相关关系,只是随空洞率增长的趋势有所变化。构成器件的不同材料膨胀系数与导热率不同以及空气导热率较低是空洞率引起热阻值改变的主要原因;高热阻加速了Al的电迁移和可动污染离子移动,最终导致器件漏电流增大。关键词:VDMOS;大漏电;高热阻;空洞率;X-RAY;SEM;EDS

TN305.94;TN386.1

A文献标识码:1005-9490(2015)01-0037-07

2014-01-07修改日期:2014-02-13

项目来源:甘肃省科技重大专项项目(1203GKDE008)

- 电子器件的其它文章

- The Implementation of CRC Algorithm Based on FPGA

- A Bandgap Reference with High Temperature Performance*

- A Method of Bottleneck Detection of Semiconductor Assembly and Test Production Line*

- Suppression of Spurious Radiation of Patch Antenna Based on Microstrip Spiral-Defected Resonant Cells*

- An Ultra-Wideband Low Noise Amplifier Based on Noise Cancellation Technique*

- Onboard DME Jitter Frequency Signal Generator Design and Implementation Based on FPGA*