基于FPGA的配电网故障行波采样及降噪设计

史洪华,钟 俊(四川大学电气信息学院,成都610065)

基于FPGA的配电网故障行波采样及降噪设计

史洪华,钟俊

(四川大学电气信息学院,成都610065)

行波信号的有效提取是配电网接地故障分析的前提,针对配电线路接地故障,行波信号具有带宽高、背景噪声强的特点,设计以FPGA为主控芯片的行波采样及降噪处理系统。针对行波电压幅值变化大的特点提出双路采集行波方案,采用Verilog HDL编程实现FPGA对AD7626的采样时序控制,并通过FIR数字滤波器对行波信号进行降噪处理,采样数据最终存入RAM中供DSP读取进行定位运算。经过对各模块进行仿真和实际测试,表明该采集系统工作稳定,数据采集准确,降噪后效果理想,具有工程应用价值。

行波采样;FPGA;FIR;降噪

四川省科技支撑项目(No.2011GZ0004)、四川省智能电网示范工程关键技术研究(No.2012GZ0009)

0 引言

配电网作为电力系统的重要组成部分,其安全、稳定、正常运行关系到用电企业的经济利益,人民群众的安定生活。随着经济的发展,社会对电力需求越来越大,配电网出现故障风险也在增大,当出现故障时,需要及时确定故障点位置,派遣人员赶到现场实行抢救和修复,以减少因电力故障而造成的损失。由此,很多学者开始研究定位算法,包括阻抗法[1]、行波法[2]、S注入法[3]、基于人工神经网络法[4]等,其中基于行波法的故障定位方法因模型简单,不受系统运行参数、故障过渡电阻的影响,测距精度较高而受国内外关注。高准确性的行波信号是故障定位算法能否应用的前提条件,这就需要稳定高效的行波采集系统对行波信号进行实时数据采集,行波采集系统也是故障定位装置的重要组成部分[5]。本文针对配电网发生故障时产生暂态行波,设计了行波采样系统。设计中以FPGA作为主控制器,FPGA具有控制能力强、逻辑资源丰富、I/O接口广泛、并行数据处理等特点,并且开发周期短,灵活性好,效率较高。

1 系统结构及硬件组成

1.1系统整体结构

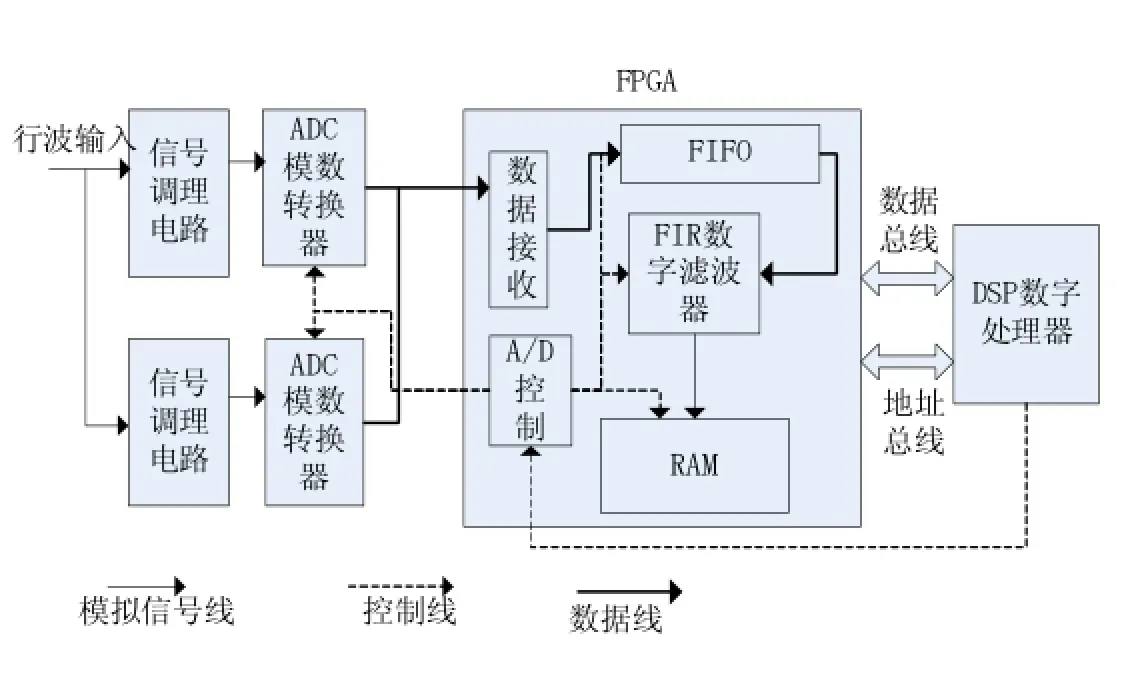

本文设计的行波采集系统主要由信号调理模块、ADC模数转换模块、FPGA控制器等组成,系统整体结构如图1所示。信号调理模块主要实现对行波信号进行滤波、单端输入转换为差分输入等方面的工作;ADC模数转换模块主要实现对行波信号进行数字转换,并将转换结果有序输出等工作;FPGA控制器主要完成对ADC转换频率控制、数据接收、数字滤波、数据存储等方面的工作。由于行波信号幅值范围在几十毫伏到几十伏之间不定,设计中采用将单路行波信号分双路进行采集,一路实现对高幅值信号采集,另一路实现对低幅值信号采集。在第一路调理电路中,先对行波信号进行分压,以符合ADC输入标准,然后接入带通滤波器进行滤波处理,经差分转换输出;另一路调理电路中,将行波信号直接接入滤波器,滤波器后端接稳压管,使低压信号通过,然后经差分转换输出。

图1 系统整体结构

1.2FPGA器件

本次设计选用的FPGA器件为Altera公司生产的Cyclone IV E系列芯片EP4CE15E22C6,这是一款低功耗、低成本的数字芯片。这款芯片具有以下特点:

●外接50M时钟,具有内部PLL,可满足对高速时钟的需求;

●内部逻辑资源丰富,满足了多种采样频率控制时序生成的需求,在此基础上,还可以对采样数据进行一定的数据处理;

●I/O接口充足,并且具备一定数量的差分接口,可实现与多个ADC的连接、与DSP数据交互及扩展外围通信接口;

●具有一定容量的存储空间,可以存储大量采样数据。

1.3ADC器件及电路设计

采集芯片选用Analog Devices公司的AD7626,这是一款16位、100MSPS的电荷再分配逐次逼近型模数转换器,具有无与伦比的抑制噪声性能和线性度。AD7626的数据输入输出和控制接口均采用差分模式,模数转换过程受CNV±信号控制,每个CNV±信号上升沿开始转换,最高转换频率可达10MHz,转换数据以串行形式输出。AD7626工作模式分为回波时钟接口模式和自时钟接口模式。回波时钟接口模式下,AD7626与数字主机之间需要三个LVDS引脚(D±、CLK±和DCO±),时钟DCO±是时钟CLK±的缓冲副本,与数据D±同步,D±在DCO±的上升沿更新输出,数字主机可根据DCO±信号对数据锁存;自时钟接口模式下,多个AD7626器件可共享同一个CLK±信号,并且数字主机不需连接DCO±引脚,这样可以减少数字主机上的LVDS连接数,数据锁存依据CLK±信号完成。

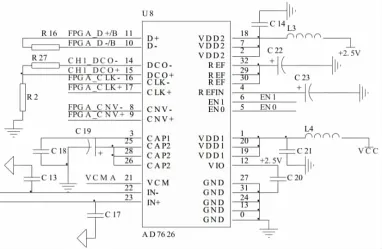

设计中考虑到需要对两路信号进行采集,AD7626工作模式选为自时钟接口模式,AD7626电路图如图2所示。AD7626正常工作需要2.5V和5V电源,电源引脚处分别连接去耦电容,并且使用电感代替氧化铁磁珠实现电源滤波。EN0和EN1为使能引脚,工作在2.5V逻辑电平下,当EN1=1,EN2=1,AD7626工作模式为采用内部基准源和内部基准缓冲器,不需要对REFIN引脚施加外部基准电压,本次设计就是采用这种模式。当DCO+接地时,AD7626选择工作模式为自时钟接口模式,电路中R2为0欧姆。AD7626与FPGA相连的三对LVDS信号之间都连接差分阻抗,电阻值为100Ω。AD7626采用内部基准源,这样不必另设外部基准源电路,REF和REFIN引脚均通过去耦电容接地。

图2 AD7626电路

1.4信号调整电路

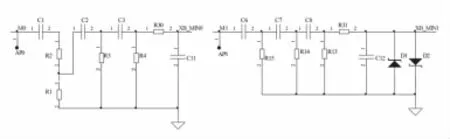

信号调理电路由滤波电路和差分驱动电路组成。配电网发生故障时暂态行波信号的频谱主要分布在10KHz到100KHz之间[6],滤波电路为无源带通滤波器,主要用来抑制低频尾波,使故障行波波头更明显,降低高频噪声和浪涌冲击等的影响,滤波电路如图3所示。

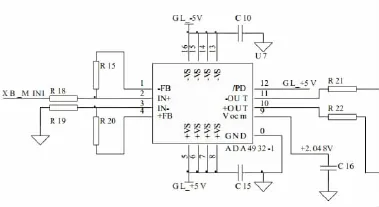

差分驱动电路以ADA4932作为差分驱动芯片,其具有很高的性能和较低的噪声及功耗,非常适合用作驱动高性能ADC的单端转差分放大器。其内部共模反馈环路产生的输出在较宽的频率范围内仍可保持高度平衡,无需紧密匹配的外部元件,从而差分输出非常理想。差分驱动电路如图4所示。

图3 滤波电路

图4 差分驱动电路

2 FPGA逻辑设计

FPGA是采样系统的控制器,其内部模块主要有A/D控制模块、数据接收模块、FIR数字滤波器模块等。程序在Quartus II集成环境下,采用Verilog HDL语言编程实现[7]。

2.1A/D控制模块

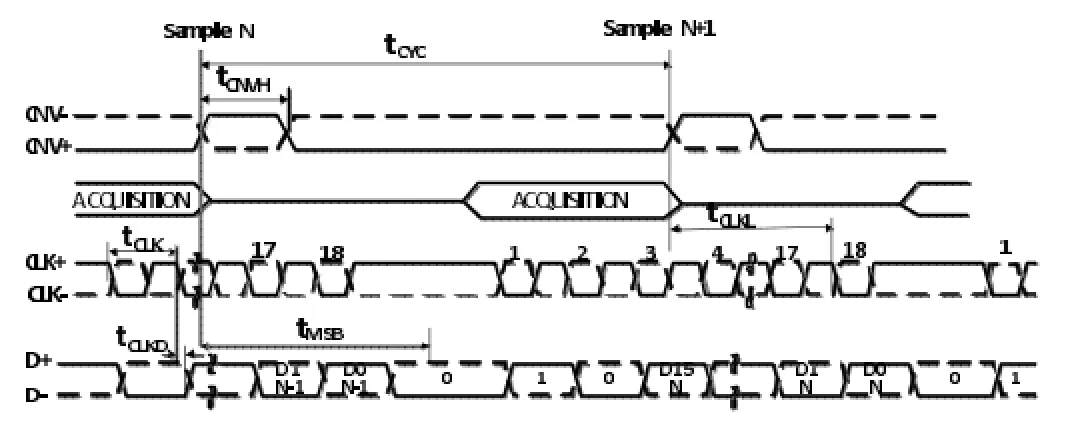

A/D控制模块主要作用是FPGA生成不同频率的采样时序,由频率寄存器决定具体采样频率时序差分输出,实现可调的变频采样控制。AD7626工作模式为自时钟接口模式,图5为该模式采样时序。AD7626工作过程为:在CNV上升沿开始对数据进行模数转换,转换时间tMSB最大为100ns,转换完成后,数字主机输出时钟CLK,AD7626在CLK的每个下降沿将一位转换结果输出,总共输出18位,前两位为标头“10”,后16位为有效数据。

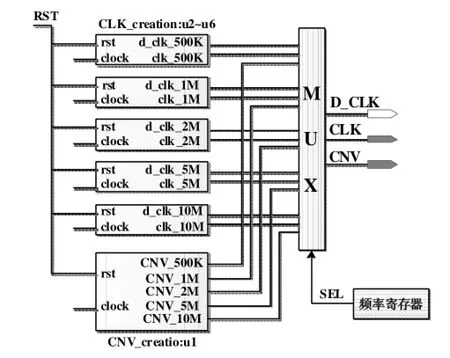

FPGA输入时钟为50MHz,具有内部PLL,可产生250MHz、125MHz等内部高速时钟。A/D控制模块逻辑结构如图6所示,CNV_creation模块产生5种频率的CNV信号,CLK_creation产生相对应的CLK信号和D_CLK信号,频率控制器选择当前采样频率,输出一组CNV、CLK、D_CLK信号,其中CNV和CLK信号通过FPGA接口差分输出到AD7626芯片,D_CLK为时钟信号,其与采样周期相同,接入数据接收模块,用于同步并行数据输出。

图5 自时钟接口模式时序图

图6 A/D控制模块逻辑结构

2.2数据接收模块

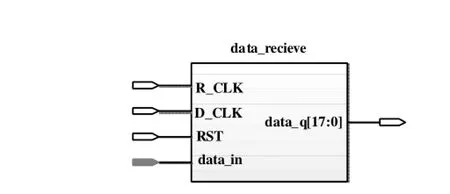

AD7626的转换结果通过D±引脚串行输出,数据接收模块作用就是对采样结果进行串并转换。如图7所示,A/D控制模块的输出CLK和D_CLK分别接入R_CLK和D_CLK,FPGA差分接口将D±转换为单端信号接入data_in,data_q[17:0]为输出。模块内部为一个移位寄存器,在R_CLK信号的上升沿读取data_in,18个时钟后,移位寄存器完成一轮存储,在D_CLK信号上升沿data_q输出转换结果。数据输出模块的输出结果接入深度为128,宽度为16位的FIFO模块缓存,FIFO模块通过Quartus II中的IP核生成。

图7 数据接收模块

2.3FIR数字滤波器实现

在故障定位过程中,故障引起的突变波头是故障定位算法的重要依赖数据,波头的准确性直接影响着故障定位的精度[8]。行波信号在传输过程中能量会受到损耗,能量的损耗会引起电压波和电流波的衰减,使得行波信号幅值可能会很低。在行波的采集过程中,由于涉及到模数变换和PCB板线路传输等环节,高频噪声和各种干扰不可难免,这些噪声会影响到低幅值行波波头的识别,这使得对采样值进行降噪处理必不可少[9]。

本文设计中选用有限冲激响应(FIR)滤波器对行波进行降噪处理,常系数FIR滤波器是一种线性时不变滤波器,稳定和线性相位是其特点,其也是FPGA进行数字滤波的常用方法[10]。

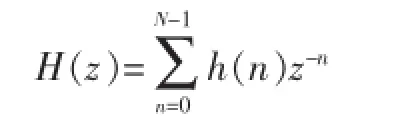

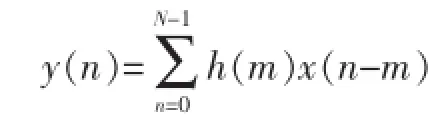

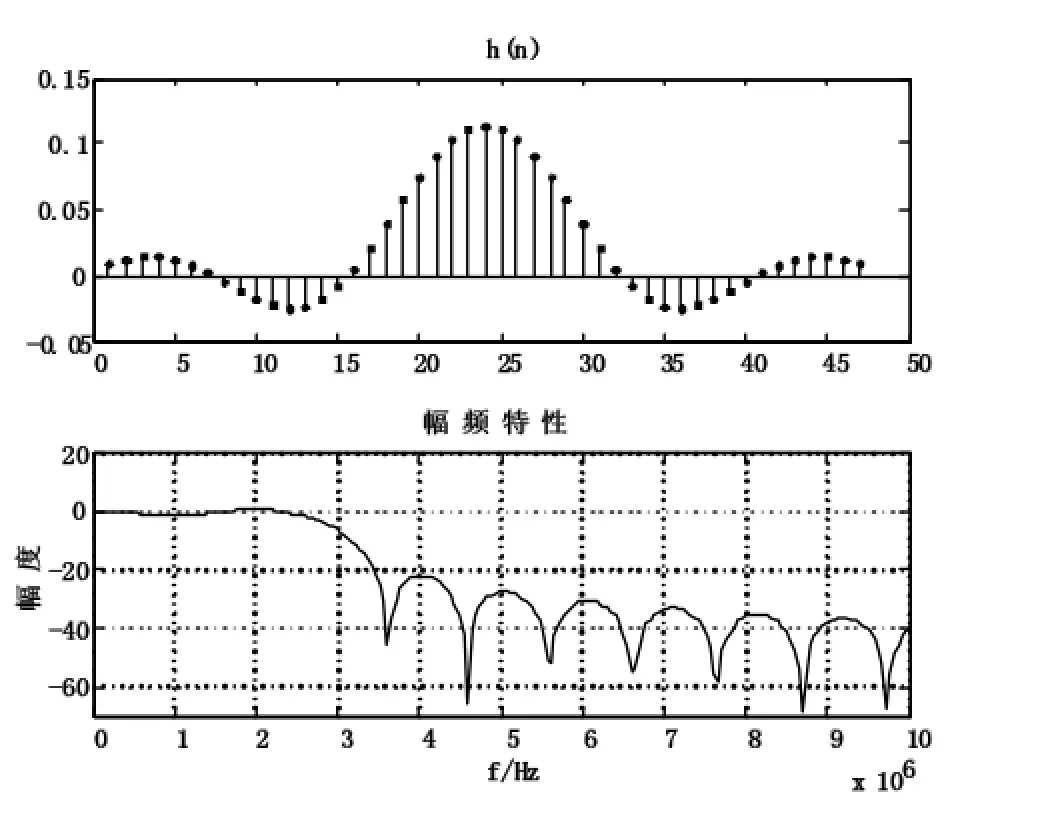

设FIR滤波器的单位冲激响应为h(n),0≤n≤N-1。其系统函数为:

差分方程形式为:

线性相位FIR滤波器的时域约束条件为单位脉冲响应为实数,且具有偶对称或奇对称性,即:

滤波器的设计借助MATLAB软件辅助完成,滤波器指标如下:

●低通滤波器;

●通带截至频率fp=2.5MHz,阻带截止频率fs= 3.5MHz;

●阻带最小衰减αs=20dB;

●滤波器阶数要小,便于硬件实现。

根据滤波器指标,选用最常用的窗函数法进行滤波器设计,由于滤波器对阻带最小衰减要求不高,且要求阶数要小,选用矩形窗较为合适。最终得到47阶滤波器,图8给出了所设计的FIR滤波器的单位冲激响应h(n)和幅频特性曲线。

图8 滤波器h(n)和幅频特性

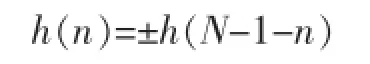

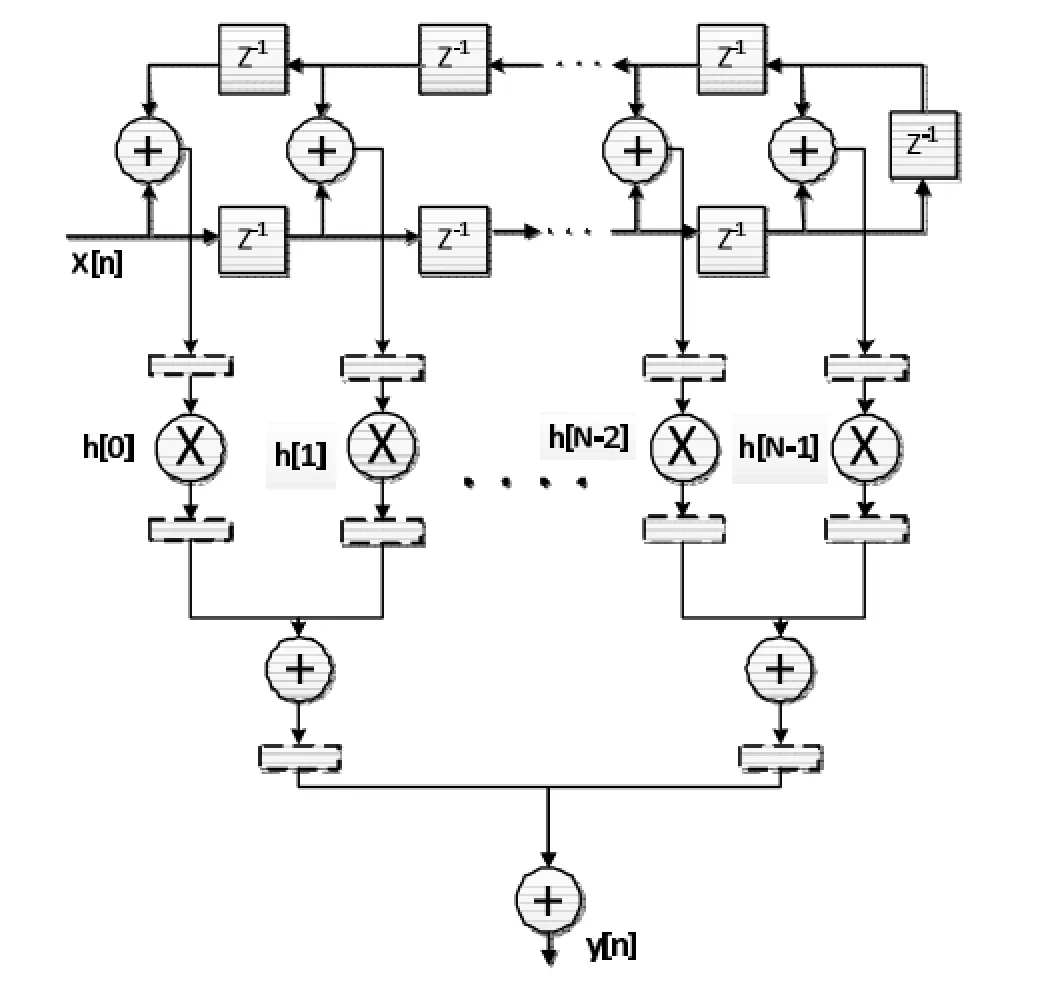

FIR滤波器的硬件实现采用并行流水线结构[11],该结构如图9所示。该结构利用滤波器系数的对称性,先将相同系数的输入值进行相加运算,再同系数进行乘法运算,最后累加输出,这样可以节省逻辑资源[12]。FPGA采样频率为可调的,并行流水线结构滤波器一个时钟周期完成一次滤波,适合数据流动速度变化的情况。

图9 滤波器并行流水线结构

FIR数字滤波器主要由输入延时模块、预相加模块、乘法器模块和累加输出模块组成,输入时钟为D_CLK。输入延时模块主要功能是对滤波器所需要的历史数据进行储备,在结构上可以看作是一个由47个16位寄存器串联在一起的存储结构,47为所设计的滤波器阶数。在每个D_CLK周期内输入一个新数据,原数据集体向后移一个存储单元,最后一个数据溢出。预相加模块主要功能是根据对称性将对应相同系数的历史数据进行相加运算,每个相加结果放入一个17位寄存器,为下一步的乘法运算提供数据支持。乘法器模块主要实现数据与系数的乘法运算。滤波器系数h(n)需要进行量化处理,量化过程就是将小数转换为有限位的硬件识别的二进制整数。将每个系数都乘以212,对结果四舍五入,得到与原始数据误差最小的整数。累加输出模块是将乘法结果进行累加,累加过程可增加流水线,累加数据有24个,将它们分为4组,对每组数据累加得到结果放入寄存器,再将4组结果累加输出,最终得到滤波结果。滤波后的数据存入双口RAM中,RAM中数据可由DSP芯片读取进行故障定位分析。

3 结果测试

利用ModelSim软件验证A/D控制模块的工作情况,图10给出了各采样频率下CNV、CLK、D_CLK信号的仿真结果,结果符合AD7626采样时序要求。

图10 各采样频率时序仿真

借助示波器对FPGA差分输出的CNV±、CLK±和D±信号进行实时监测,验证AD芯片工作情况,示波器为Tektronix公司的DPO4104B型号,其具有高速差分探头,可直接对LVDS信号进行实时监测。FPGA输出10MHz采样频率下CNV±和CLK±信号,示波器显示结果如图11所示,对比仿真结果,输出波形正确。

图11 CNV±和CLK±示波器监测图

图12为电路板在未接入任何输入情况下D±和CLK±信号示波器监测结果,观察发现D±信号输出比CLK±延迟大约3ns左右,D±的两组输出为“2FF8A”即“10_1111_1111_1000_1010”和“2FF87”即“10_1111_ 1111_1000_0111”,换算成电压约为-15mV,结果相对合理。

图12 D±和CLK±示波器监测图

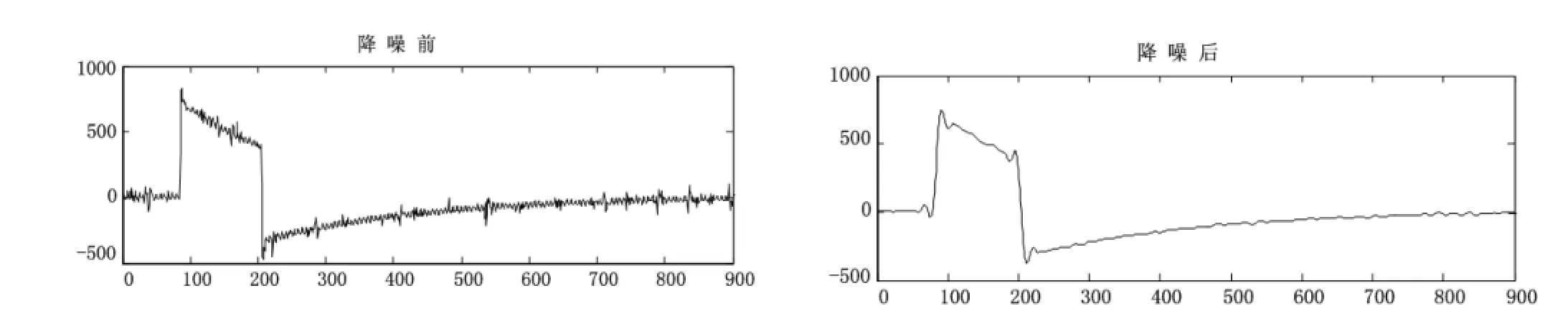

外围电路产生矩形脉冲作为行波信号接入采样系统,FPGA控制AD7626进行采样并存入RAM,DSP读取数据传入计算机。利用MATLAB将数据恢复成波形,如图13所示,上图为FPGA未进行滤波处理的波形,下图为FPGA滤波处理后的波形。可以看出,采样结果准确,经过滤波后,效果更佳理想,系统达到了预期要求。

4 结语

本文针对配电网中行波特点,利用FPGA和AD7626芯片设计了行波采样系统。该系统可实现变频采样,最高采样频率可达10MHz,并根据行波噪声特点,设计了FIR数字滤波器,滤波器通过FPGA硬件实现,保证了行波数据的完整性和有效性。测试过程中,模拟行波信号输入到采样系统,数据经MATLAB还原为波形,证实了采样精确,降噪后效果理想,系统工作稳定性强,采样误差小,具有工程实用性,可成为故障定位装置的重要组成部分。

图13 波形恢复及降噪前后对比图

[1]Grajales-Espinal C,Mora-Florez J,Perez-Londono S.Single Phase Fault Locator Based on Sequence Impedance for Power Distribution Systems[C].Transmission&Distribution Conference and Exposition-Latin America(PES T&D-LA),2014 IEEE PES.IEEE,2014: 1~5

[2]Zhao X,Qi Y,Li G.Research and Implementation of PLC for Multiport Traveling Wave Fault Location in the Medium Voltage Distribution Network[C].Electric Utility Deregulation and Restructuring and Power Technologies(DRPT),2011 4th International Conference on.IEEE,2011:614~617

[3]张慧芬,潘贞存,桑在中.基于注入法的小电流接地系统故障定位新方法[J].电力系统自动化,2004,28(3):64~66

[4]刘文轩,严凤,田霖,等.基于LVQ神经网络的配电网故障定位方法[J].电力系统保护与控制,2012,40(5):90~95

[5]Dianrui Z,Mingli W,Mingchao X.Study on traveling Wave Fault Location Device for Electric Railway Catenary System Based on DSP [C].Sustainable Power Generation and Supply,2009.SUPERGEN'09.International Conference on.IEEE,2009:1~4

[6]季涛,孙同景,徐丙垠,等.利用配电变压器获取行波信号[J].电力系统自动化,2006,30(16):66~70

[7]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2013

[8]张峰.输电线路行波故障测距优化算法研究[D].山东大学,2010

[9]叶睆.高压输电线路行波定位系统的设计与开发[D].华中科技大学,2007

[10]高西全,丁玉美.数字信号处理[M].西安:西安电子科技大学出版社,2008:196~-217

[11]徐远泽,戴立新,高晓蓉,等.FIR滤波器的FPGA实现方法[J].现代电子技术,2012,22:64~67

[12]U.Meyer-Baese著.刘凌译.数字信号处理的FPGA实现[M].北京:清华大学出版社,2011

Traveling Wave Sampling;FPGA;FIR;Denoising

Design of Distribution Network Fault Traveling Wave Sampling and Denoising Based on FPGA

SHI Hong-hua,ZHONG Jun

(School of Electrical Engineering and Information,Sichuan University,Chengdu 610065)

Traveling wave signal effective extraction is the precondition of analyzing distribution network grounding fault,in view of the distribution circuit ground fault,traveling wave signals have the characteristics of high bandwidth and strong background noise,designs traveling wave sampling and denoising processing system which used FPGA as main control chip.According to the characteristics that traveling wave’s voltage changes big,proposes dual acquisition traveling wave solution,FPGA controlled the AD7626 sampling by using Verilog HDL programming,and through the FIR digital filter to complete the traveling waves denoising processing,stores the sample data into RAM for DSP to read.Through simulation and actual test,it shows that the acquisition system works stable,collects data accurately,and has good effect after denoising processing,it has the engineering application value.

1007-1423(2015)14-0074-07

10.3969/j.issn.1007-1423.2015.14.018

史洪华(1989-),男,河北唐山人,硕士研究生,研究方向为嵌入式、无线传感器网络

钟俊(1972-),男,重庆人,博士,副教授,研究方向为信号与信息处理、嵌入式

2015-03-26

2015-04-30