同时基于预知信息和预测机制的SDRAM动态页策略*

吕 晖,谢向辉

(数学工程与先进计算国家重点实验室,江苏 无锡214125)

1 引言

随着集成电路技术的发展,片上计算资源的集成度越来越高,片上所能集成的计算核心数量已经从单核、多核一直发展到数百甚至数千核心[1,2]。但是,存储技术的发展速度远不能满足计算能力的发展需求。特别受芯片信号引脚数量和数据传输率两方面因素的限制,访存带宽已经成为系统性能的最主要瓶颈。如何充分发掘有限的访存带宽资源,成为系统设计者需要重点考虑的问题之一。

基于成本和性能等多方面因素的考量,SDRAM成为构建现代主存系统的基础。从用于通用计算系统的DDR系列存储技术(DDR、DDR2、DDR3、DDR4),到用于嵌入式/手持计算系统的LPDDR系列存储技术(LPDDR2、LPDDR3、LPDDR4),以及用于显存领域的GDDR系列存储技术(GDDR3、GDDR5),甚至混合存储立方体HMC(Hybrid Memory Cube)等新型存储技术[3],SDRAM都是其中最重要的组成部分。

SDRAM的结构特征和工作原理,决定了页策略是提升实际访存效率的重要因素之一。传统上,页策略分为页打开策略和页关闭策略。一般情况下,页打开策略适用于页命中率较高的访存序列,而页关闭策略适用于页命中率相对较低的序列。这样,无论固定采用页打开策略,还是固定采用页关闭策略,均存在性能相对较差的情况。因此,如何将两种页策略相结合,就成为研究者们的关注点[4~12]。

在上述研究工作中,绝大多数均基于预测机制[4~10]。调度器记录访存序列的历史信息,对未知的访存请求的行为特征进行预测,然后依此动态确定采用何种页策略。这类基于预测机制的页策略,其性能取决于页策略切换时机是否能够精确契合访存序列的行为特征。受限于应用程序访存行为的复杂程度以及硬件预测机制的实现代价,基于预测机制的动态页策略对访存性能的改善程度有限。

文献[11,12]则采用了基于预知信息的页策略。文献[11]所使用的预知信息由处理器提供,当存储控制器中的访存请求缓冲为空时,方可进行页策略转换。该方法使用单独的“预充电”命令关闭页,而不是采用“带预充电功能的读/写”命令,这就导致无法有效降低对命令总线带宽的需求。

文献[12]所使用的预知信息由存储控制器内部的访存请求缓冲提供。当请求队列非空时,该方法能够根据请求调度缓冲中的待处理请求的地址信息,直接计算出后续访存请求的页命中情况,存储控制器可依此动态决定采用何种页策略;当请求队列为空时,该方法则固定采用页打开策略。尽管文献[12]是迄今为止相对最理想的动态页策略之一,但却并未对预知信息对不同页策略的系统性能优化程度进行全面研究。此外,当访存请求较为稀疏,导致请求队列为空时,该方法不具备对后续访存序列页命中情况的有效预测能力。

基于以上分析,本文系统研究了使用预知信息对多种页策略的性能优化效果,并提出了一种同时基于预知信息和预测机制的动态页策略。该策略能够更好地适用各类不同类型的访存序列,有效提升实际访存效率。该策略的关键思想是,若请求队列非空,则最适宜当前请求的页策略可以精确获知;若请求队列为空,则依据历史信息对最适宜当前请求的页策略进行预测。

为了系统研究基于预知信息的多种动态页策略的性能优化效果,并证实本文所提出的动态页策略的有效性,作者采用SPEC2006中的部分测试程序分别在1核、2核、4核、8核环境下进行了36项测试。每项测试完成六种页策略实验,其中,三种使用传统页策略,三种使用基于预知信息的动态页策略。从实验结果可以看出,基于预知信息的页策略均优于不基于预知信息的页策略,最好情况下,实际访存带宽可提升42%。此外,对于三种基于预知信息的页策略而言,三者性能差异相对较小,而本文所提出的“同时基于预知信息和预测机制的动态页模式调度策略”的多数情况下性能较优,能够较好地适应各类不同的访存序列。

2 研究背景与研究目的

2.1 SDRAM 页策略

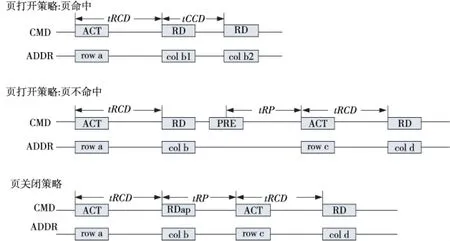

在现代SDRAM系统中,每个存储颗粒由若干存储体(Bank)组成,每个存储体由存储阵列、页缓冲以及附加逻辑等组成。在访问SDRAM时,需要先使用激活ACT(Active)操作将SDRAM的存储阵列中的内容读入页缓冲,然后才能使用读RD(Read)或者写 WE(Write)命令对其进行访问,访问完毕后可以使用预充电命令PRE(Precharge)将页缓冲的数据写回SDRAM的存储阵列。当预充电命令紧随读命令(或者写命令)之后时,可以使用一条“带预充电的读命令(或者写命令)”替代由“读命令(或者写命令)和预充电命令”组成的命令序列。其中,“带预充电的读命令”简记为RDap,“带预充电的写命令”简记为WEap。

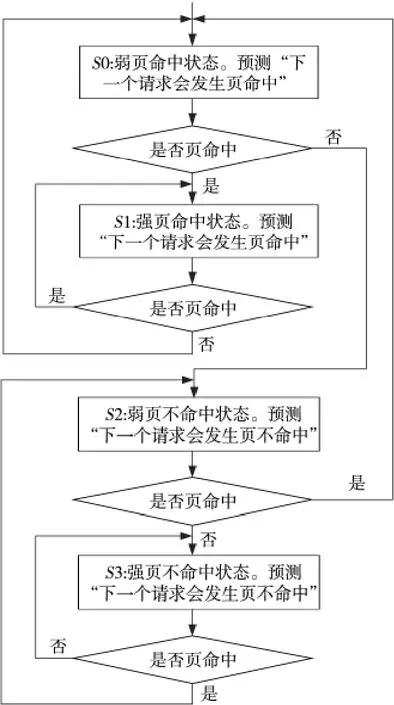

如果在一次读写访问之后,将数据继续保持在页缓冲中,而不是将其写回至存储阵列,那么这种页策略就称为“页打开策略”;如果在一次访问之后,将页缓冲中的数据写回SDRAM的存储阵列,那么这种页策略就称为“页关闭策略”[2]。访存序列如图1所示。

页打开策略和页关闭策略拥有各自的优缺点。对于页打开策略,若后续访问能够命中页缓冲中的数据,则能减少访存延迟、减少访存命令数量,有利于增加访存带宽;但是,若后续访问不命中页缓冲的数据,则增加访存延迟、增加访存命令数量,不利于提升访存带宽。对于页关闭策略,其访存延迟、所耗用的访存命令数量均与是否命中页缓冲无关,其好处是访存延迟、访存带宽不受页命中率高低的影响;其不足是当页缓冲命中率较高时,无法使访存延迟、访存带宽最优化。

图1 SDRAM页打开策略和页关闭策略的访存命令序列图Figure 1 SDRAM command sequence for the page open/close policy

2.2 研究目的

无论固定采用页打开策略,还是固定采用页关闭策略,都无法使访存性能在各类情况下均获得最优。因此,根据访存行为的特征,混合使用页打开和页关闭策略组成的动态页策略,是提升系统访存性能的有效手段之一。

根据策略选择依据的不同,动态页策略可分为两类:一类是基于预测的页策略,一类是基于预知信息的页策略。在能够获知后续访存请求的地址信息的条件下,基于预知信息的页策略能够更精确地对页模式进行调度,对访存性能的优化效果更为显著。在无法获知后续访存请求的地址信息的条件下,若基于合适的预测机制对页模式进行调度,则有可能获得更好的优化效果。

总之,动态页策略对于访存延迟、访存带宽、主存系统功耗等都会产生显著影响,有必要对其进行深入研究。

3 系统结构

为了能对基于预知信息的动态页策略进行系统的分析,本文设计并实现了一个能以较低的硬件代价同时支持六种页策略的SDRAM存储控制器。

该存储控制器由以下几个主要功能模块构成:访存请求缓冲、请求解析状态机、数据写入缓冲、数据读出缓冲等。其中,访存请求缓冲用于存放用户访存请求;请求解析状态机则负责将访存请求缓冲的模块依次取出,并将其翻译成SDRAM命令序列;数据写入缓冲,用于接收用户数据,并在合适的时机将其送入SDRAM;数据读出缓冲,用于接收来自SDRAM的数据,并将其以约定的格式送回用户。总体结构如图2所示。

Figure 2 Architecture of the memory controller图2 存储控制器总体结构

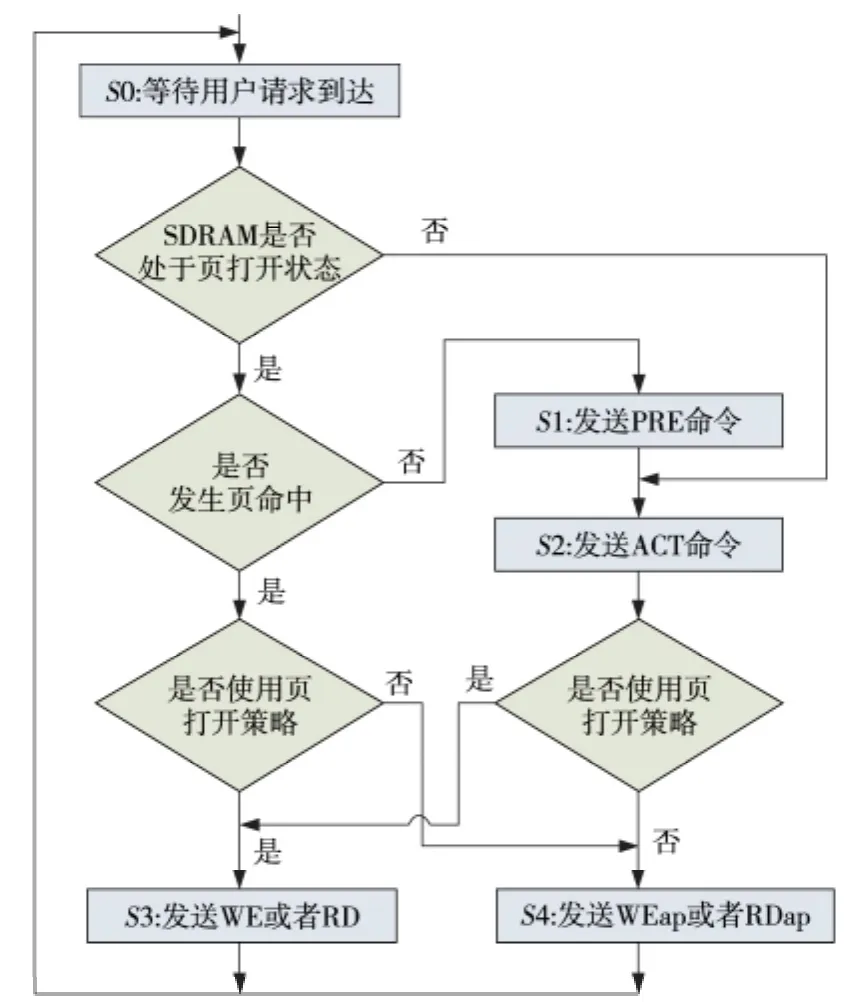

3.1 请求解析状态机

请求解析状态机是存储控制器的核心模块。该状态机根据SDRAM页缓冲中的数据是否有效、访存请求地址是否命中页缓冲等信息,决定是否在SDRAM读写命令之前发送激活命令、预充电命令;然后,根据页策略控制信息,决定是发送带预充电功能的SDRAM读写命令,还是发送不带预充电功能的SDRAM读写命令。请求解析状态机的算法状态图如图3所示。

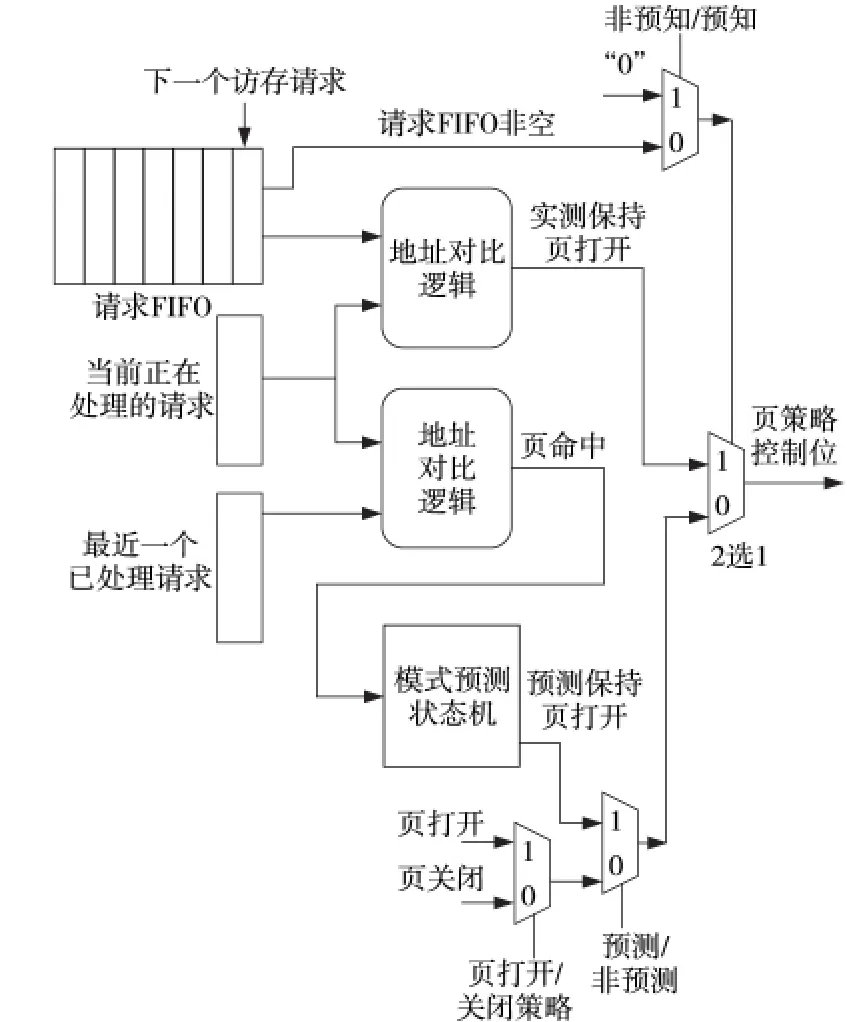

3.2 页策略控制信息的生成

为了实现基于预知信息的SDRAM动态页策略,需要由访存请求缓冲模块向请求解析状态机提供页策略控制信息。该信息为位宽为1的控制位,当其取值为1时,表示需要采用页打开策略;当其取值为0时,表示需要采用页关闭策略。该控制位的取值可由所采用的页策略、后续请求的页命中情况动态确定。其生成逻辑的实现结构如图4所示。

Figure 3 Algorithm state diagram of the request decomposing state machine图3 请求解析状态机的算法状态图

Figure 4 Generation of the page controlling policy图4 页策略控制信息的生成

在上述结构中,“非预知/预知”开关用于选择是否采用“基于预知信息的页策略”,“预测/非预测”开关用于选择是否采用“基于预测机制的页策略”,“页打开/关闭策略”开关用于选择是采用页打开策略或是采用页关闭策略。

当“非预知/预知”开关取值为1时,所控制的2选1逻辑输出为0,该输出将作为下一级选择逻辑的控制开关值,因此,由地址对比逻辑所生成的“实测保持页打开”信息将被忽略,此时,将采用“非预知”类型的页策略。

当“非预知/预知”开关取值为0时,所控制的2选1逻辑输出为“请求FIFO非空”值,该输出将作为下一级选择逻辑的控制开关值。当请求FIFO非空时,由地址对比逻辑所生成的“实测保持页打开”信息将被选中,此时可精确预知后续请求的页策略需求;当请求FIFO为空时,将采用页打开、页关闭或者基于预测的动态页策略。

各个页策略的配置编码表如表1所示。

Table 1 Configuration codes for page policies表1 页策略的配置编码表

其中,模式预测状态机的算法状态图如图5所示。

Figure 5 Algorithm state diagram of the mode-prediction state machine图5 模式预测状态机的算法状态图

3.3 硬件实现代价分析

请求FIFO是已有结构,2个地址对比逻辑、4个2选1选择器、1个模式预测状态机和用于存放“当前正在处理的请求”和“最近一个已处理请求”的两个寄存器是新增结构。其中,各新增结构的硬件实现代价分析如下:

(2)2选1选择器。其逻辑表达式可记为:a[i]=a[i]·(~s)+b[i]·s。其中,c为逻辑的输出,a、b为逻辑的输入,~为“逻辑非”操作,·为“逻辑与”操作,+为“逻辑或”操作。对于位宽为1的“2选1选择器”而言,使用2个与门、1个非门、1个或门即可完成逻辑的搭建。

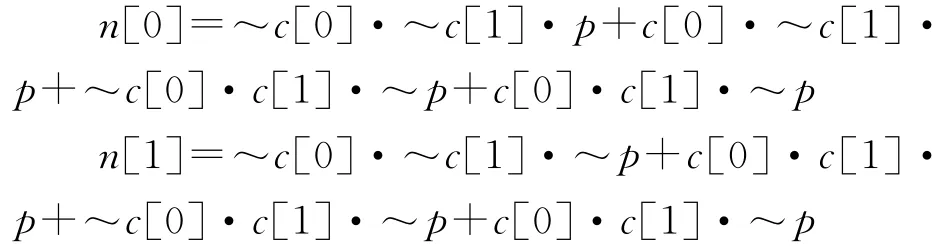

(3)模式预测状态机。模式预测状态机由一个位宽为2的当前状态寄存器及其对应的次态生成逻辑构成。该状态寄存器记为c,其次态生成逻辑的输出记为n,页命中标记记为p,根据模式预测状态机的工作原理图,可以得到次态生成逻辑的表达式如下:

其次态生成逻辑使用16个与门、6个或门、12个非门即可搭建完成。

由以上分析可知,所需要的新增硬件结构实现代价很小。

4 实验

4.1 实验方法

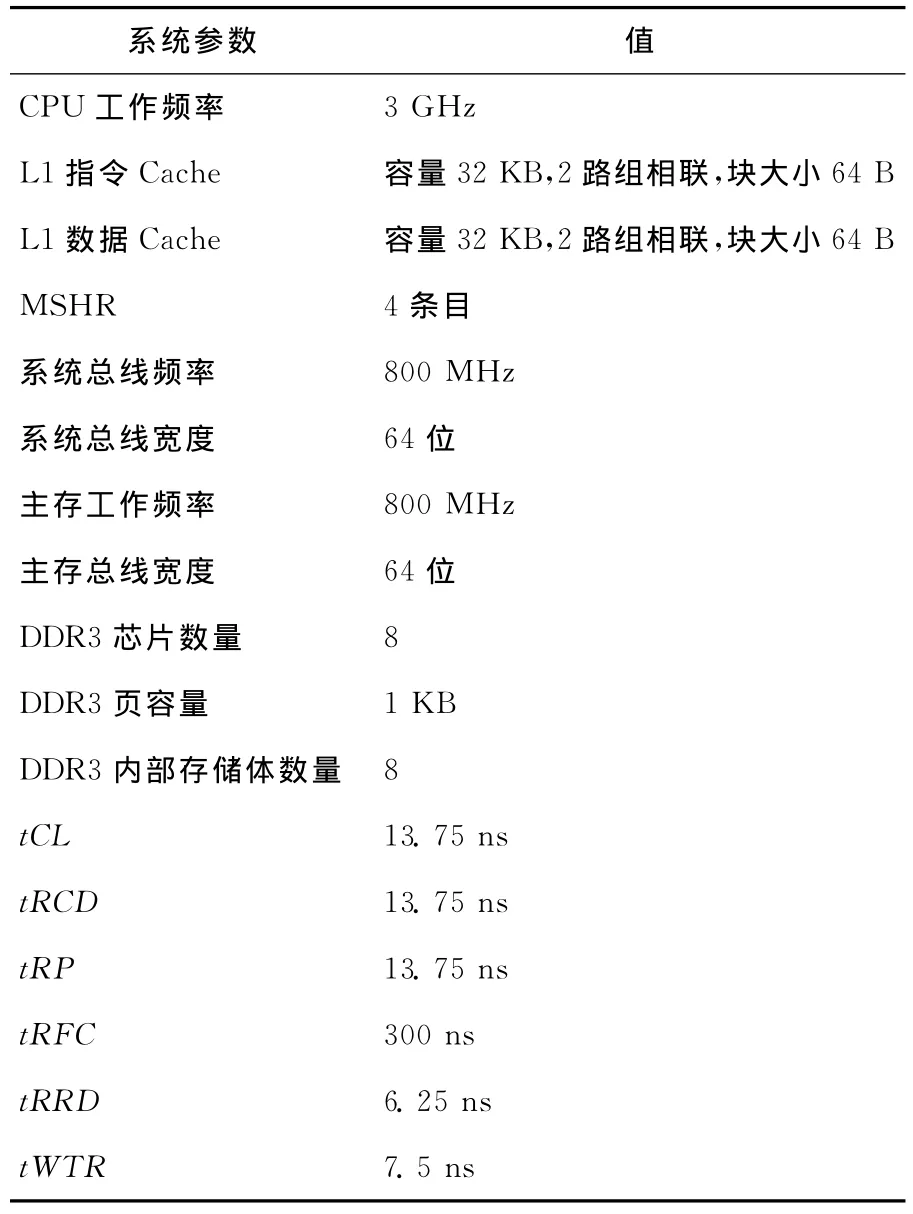

为了深入分析基于预知信息的SDRAM动态页策略优化效果,作者使用Gem5模拟器搭建了1核心、2核心、4核心、8核心等四个不同核心数量的实验系统。各个核心通过总线相连,共享同一个访存通路。各系统中每个核心的主要硬件参数如表2所示。

本文采用SPEC cpu2006测试套件作为测试激励。本文随机选取了9个测试程序,运行在四个不同核心数量的实验系统上。每个系统均对页关闭策略、页打开策略、基于预测的动态页策略、基于预知信息的页关闭策略、基于预知信息的页打开策略、同时基于预知信息和预测机制的页策略等六种策略进行测试。

Table 2 Hardware parameters of the experimental system表2 实验系统的硬件参数

对于实验结果,本文重点关注未施加/已施加预知信息的页策略之间的访存带宽差异。例如,“页关闭策略”和“基于预知信息的页关闭策略”之间的性能差异、“页打开策略”和“基于预知信息的页打开策略”之间的性能差异、“基于预测的动态页策略”和“同时基于预知信息和预测机制的页策略”之间的性能差异。

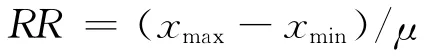

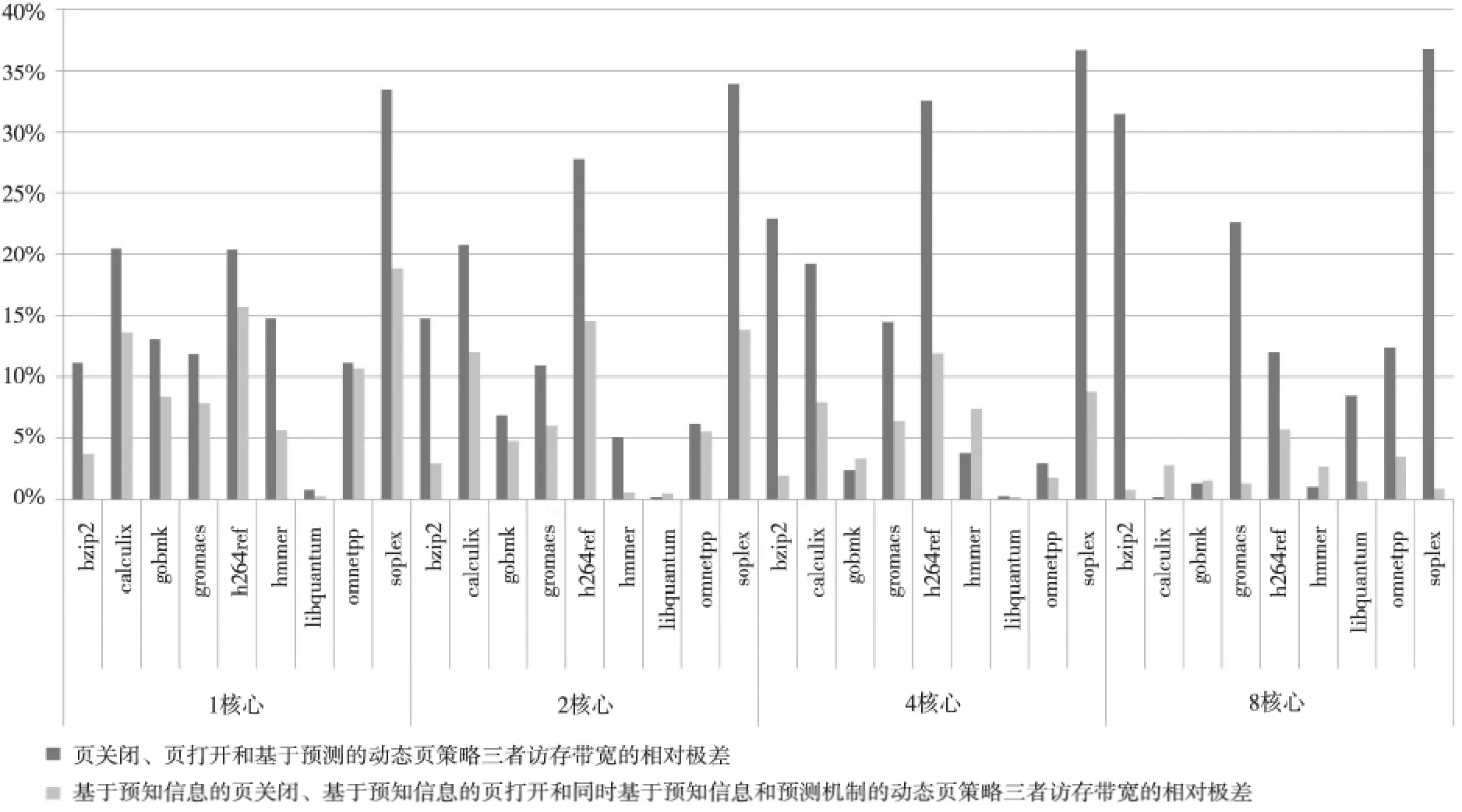

此外,为了衡量未施加/已施加预知信息的两组页策略各自的性能数据的离散程度,本文引入“相对极差”这一统计学当中的常用统计指标。该指标主要用于比较不同组别数据的离散程度,其取值越大,表示该组数据的离散程度越大;其取值越小,表示该组数据的离散程度越小。计算方法为:

其中,RR表示相对极差,xmax和xmin分别表示测量数据中的最大值和最小值,μ表示测量数据的平均数。

4.2 实验结果

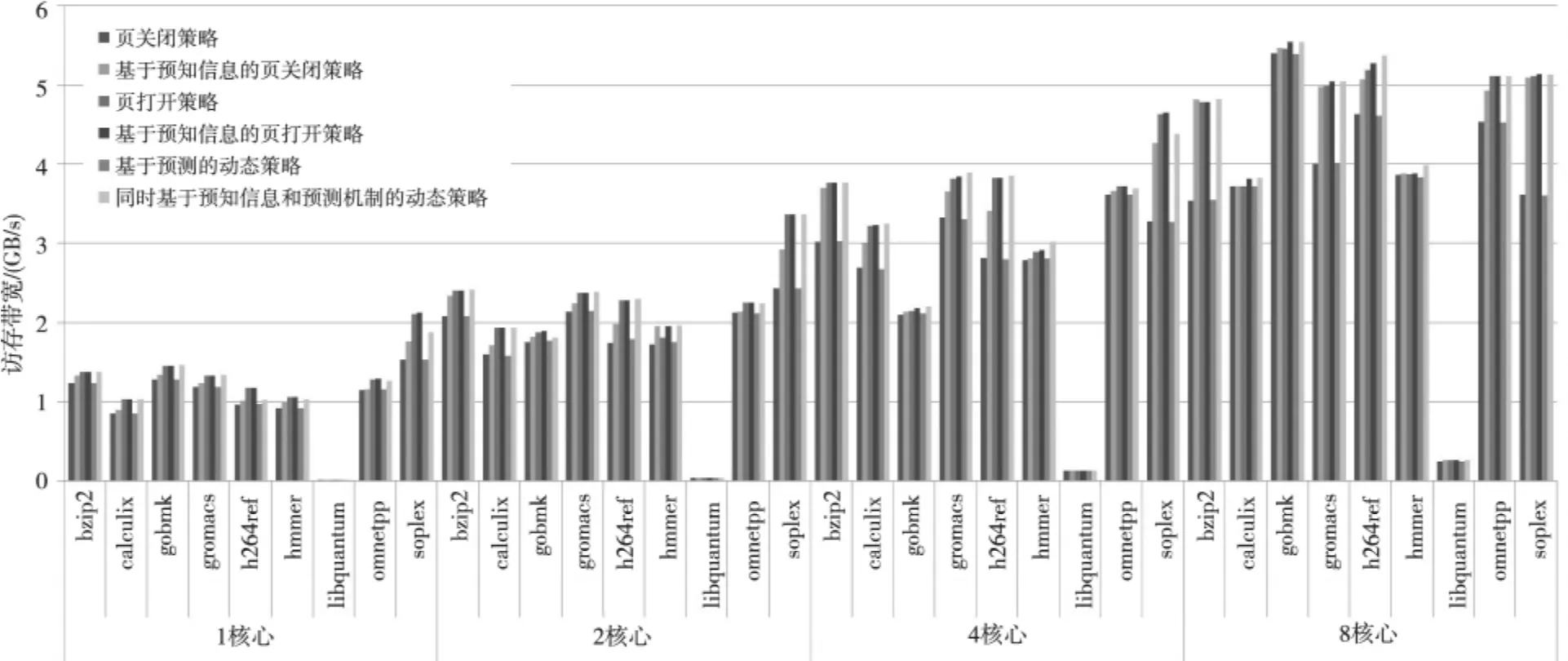

实验结果如图6所示。图6的纵坐标为不同页策略所获得的访存带宽,横坐标为不同核心数量下的测试激励。其中,每一项测试激励都使用六种页策略进行测试,其测试结果从左至右分别对应着页关闭策略、基于预知信息的页关闭策略、页打开策略、基于预知信息的页打开策略、基于预测的动态页策略、同时基于预知信息和预测机制的动态页策略。

Figure 6 Experimental results图6 实验结果

Figure 7 Relative range of memory bandwidth of the two page policies图7 两组页策略访存带宽的相对极差

从上述实验数据中可以看出,当在基础页策略上施加预知信息进行优化后,访存带宽均获改善,最好情况下,实际访存带宽可提升42%强。此外,对于未施加预知信息的页关闭、页打开、基于预测的动态页策略,三者之间的访存性能差异较大,其相对极差最大可达37%;而对于基于预知信息的页关闭、基于预知信息的页关闭页打开、同时基于预知信息和预测机制的动态页策略,三者之间的性能差异普遍显著降低,均不超过19%。特别地,对于8核心系统,后三者的相对极差最大仅为6%,如图7所示。这说明三种基于预知信息的页策略之间的性能差异不大,均可获得较理想的实际访存带宽。

对于每一项测试激励而言,基于预知信息的三种页策略(页打开、页关闭、基于预测的动态页策略)的性能相对优劣如表3所示。

Table 3 Performance comparison of the three page policies based on advance information表3 三种基于预知信息的页策略性能比较

从表3中可以看出,对于大多数测试激励,同时基于预知信息和预测机制的动态页模式调度策略最优,基于预知信息的页打开策略性能略差,基于预知信息的页关闭策略性能最差。

综上所述,基于预知信息的三类页策略均能有效提升系统访存性能。三者之中相对而言,“同时基于预知信息和预测机制的动态页模式调度策略”性能最优,带宽最高的测试项数最多,即适应范围最广。

5 相关工作

对于SDRAM页策略,已经有若干相关研究工作。除了最基本的页打开、页关闭两种固定页策略[2]以外,还出现了若干混合使用页打开/页关闭两种页策略的动态页策略。

这些动态页策略可分为三类。基于预测的动态页策略、基于定时器的动态页策略、基于预知信息的动态页策略。

文献[4~10]都是基于预测的动态页策略。基于预测的动态页策略可分为两种,第一种基于历史访存序列进行预测,第二种是基于定时器机制进行预测。基于历史访存序列的动态页策略,其基本原理是利用访存序列的历史信息,对后续访存请求的页命中情况进行预测,以选择合适的页策略。其中,文献[4]使用有限状态自动机记录历史信息,最多记录4个历史访存请求的页命中情况;文献[5]则是仅记录历史访存序列中的页不命中次数,所记录的历史页不命中最大次数动态可调整;文献[6,7]可记录连续16个以上的历史访存请求的页命中情况;文献[8]则是利用周期采样技术对历史访存请求的页命中情况进行分析。

文献[9,10]都是基于定时器的动态页策略,该策略的基本原理是每次访存之后,保持页打开一定时间(该时间长度由定时器决定),如无新的请求到来,则页关闭。其中,文献[9]中的定时器取值固定不变,文献[10]中的定时器的取值随着访存序列特征的变动而动态变化。

文献[11,12]则采用了基于预知信息的动态页策略。该策略不再利用访存序列的历史信息对后续访存请求的页命中情况进行预测,而是直接观察后续访存请求的页命中情况,以选择合适的页策略。其中,文献[11]由处理器核心向存储控制器提供后续访存请求的页命中情况,文献[12]则由存储控制器内部的访存请求缓冲自行计算后续访存请求的页命中情况。

上述混合使用页打开/页关闭两种页策略的动态页策略的效果,和对访存序列行为特征的契合程度密切相关。总体来说,基于预知信息的动态页策略的适应面相对较广,但是仍对相当数量的访存序列适应性较差,因此本文进行了进一步的深入研究。

6 结束语

本文对三类主要的基于预知信息的动态页策略进行了系统研究,并提出了一种同时基于预知信息和预测机制的SDRAM动态页策略。该策略可充分利用缓存在FIFO中的待处理访存请求的地址信息,对后续页命中情况进行精确判断,并以之对页策略进行管理;而当没有待处理访存请求可预知时,则利用所记录的历史信息对后续页命中情况进行预测,为后续请求选择合适的页策略。

经实验证实,总体而言,三类基于预知信息的动态页策略之间的性能差异较小,均能获得较理想的访存带宽。其中,同时基于预知信息和预测机制的动态页策略的性能在三者之中最优,适应面最广泛。

[1] Sodani A.Intel Xeon Phi processor“knights landing”architectural overview[EB/OL].[2015-11-17].http:∥ www.nersc. gov/assets/uploads/KNL-ISC-2015-Workshop-Keynote.pdf.

[2] Johnson D R,Johnson M R,Kelm J H,et al.Rigel:A 1,024-core single-chip accelerator architecture[J].IEEE Micro,2011,31(4):30-41.

[3] Ahn J,Yoo S,Choi K.Dynamic power management of offchip links for hybrid memory cubes[C]∥Proc of the 51st ACM Annual Design Automation Conference,2014:1-6.

[4] Park S,Park I.History-based memory mode prediction for improving memory performance[C]∥Proc of the 2003IEEE International Symposium on Circuits and Systems,2003:185-188.

[5] Miura S,Ayukawa K,Watanabe T.A dynamic-SDRAM-mode-control scheme for low-power systems with a 32-bit RISC CPU[C]∥Proc of the ACM 2001International Symposium on Low Power Electronics and Design,2001:358-363.

[6] Xu Y,Agarwal A S,Davis B T.Prediction in dynamic SDRAM controller policies[C]∥Proc of the 9th International Workshop on Embedded Computer Systems:Architectures,Modeling,and Simulation,2009:128-138.

[7] Awasthi M,Nellans D W,Balasubramonian R,et al.Prediction based DRAM row-buffer management in the many-core era[C]∥Proc of the 11th IEEE International Conference on Parallel Architectures and Compilation Techniques,2011:183-184.

[8] Xie M,Tong D,Feng Y,et al.Page policy control with memory partitioning for DRAM performance and power efficiency[C]∥Proc of the 2013IEEE International Symposium on Low Power Electronics and Design,2013:298-303.

[9] Kahn O D,Wilcox J R.Method for dynamically adjusting a memory page closing policy:U.S.Patent 6799241[P].2004-9-28.

[10] Sander B T,Madrid P E,Smaus G W.Dynamic idle counter threshold value for use in memory paging policy:U.S.Patent 6976122[P].2005-12-13.

[11] Huan D,Li Z,Hu W,et al.Processor directed dynamic page policy[C]∥Proc of the 11th Asia-Pacific Computer Systems Architecture Conference,2006:109-122.

[12] Binkert N,Beckmann B,Black G,et al.The gem5simulator[J].ACM SIGARCH Computer Architecture News,2011,39(2):1-7.