基于JPEG2000的视频压缩技术研究

李 波,何 亮

(成都大学 电子信息工程学院,四川 成都 610106)

0 引 言

传统的静态图像压缩标准技术(如GIF、JPEG等图像格式)应用于医学成像、数据库、多媒体、因特网及移动通信网等领域时,主观质量下降明显,已经难以满足某些方面的需求[1].新一代图像压缩标准JPEG2000,以其优良的压缩特性,适应于多个相关领域,但由于其算法实现复杂、耗时较长,其推广和 应 用 受 到 一 定 影 响[2-7].对 此,本 研 究 在JPEG2000 图像压缩技术研究的基础上,基于ADV212 设计了一种图像压缩编码系统.

1 JPEG2000 编码原理

JPEG2000 生成的压缩码流同时具有分辨率可分级性和质量可分级性,支持图像的渐进传输,且具有较好的抗误码性能,JPEG2000 对每帧视频均采用JPEG2000 编码.

JPEG2000 压缩过程如图1 所示,如果是多颜色分量的输入图像,则首先进行颜色分量间去相关变换,然后将图像/图像成分分割成大小相等(边缘除外)、相互不重叠的矩形图像片(Tile)[8],在进行DWT 变换前要进行直流电平位移操作,去除图像的直流分量.JPEG2000 的DWT 变换中,浮点数9/7 滤波器主要用于高压缩率有损压缩,短整数5/3 滤波器用于实现可逆的无损压缩[3].对小波变换产生的系数进行量化,小波子带b 的每一个变换系数通过式(1)进行标量量化,

图1 JPEG2000 原理框图

其中,△b 为量化步长,量化会使系数的精度降低.若采用整数5/3 小波变换进行无损压缩,量化步长为1.

量化后的系数被分割成码块(Code-blocks)进行第一层编码(Tierl),主要包括产生上下文(Context)和待压缩的位数据(Decision),以及用二进制算术编码器MQ-Coder 进行算术编码.产生的数据流又进入第二层编码(Tier2),主要用于进行率失真优化和使用Tag Tree 对压缩码流进行打包.码率控制模块则用于对编码过程产生预期码率.

2 视频采集压缩的实现

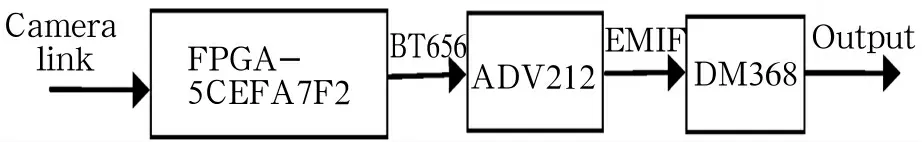

视频采集压缩系统的硬件结构如图2 所示.视频输入和压缩芯片分别使用了ADI 公司的ADV212以及FPGA-5CEFA7F27I7N 芯片,压缩后的数据通过TMS320DM368 传输到本地计算机解码播放.

图2 视频采集压缩硬件原理图

2.1 视频输入模块

系统上电或复位之后,FPGA 通过Camera link接口获得高清视频输入.FPGA 为了解决视频输入与输出的速率匹配问题[5],通过外部DDR 存储器缓存1 帧视频来实现数据高速传输.FPGA 缓存1 帧完整的数据后,通过BT656 接口,传输到ADV212 数字编码芯片压缩,接口使用8 bits 并行数据线,54M像素时钟,内嵌同步方式.

2.2 视频压缩模块

ADV212 是针对视频和高带宽图像压缩应用的一款JPEG2000 编解码芯片,它提供了一个基于空间高效滤波SURF(Spatial Ultra-eltleient Recursive Filtering)技术的专用小波变换器,支持多达6 级的9/7 和5/3 小波变换.在3 分量4∶ 2∶ 2 隔行模式,能够处理的图像,片(Tile)宽度最大为2 048 像素.工作于可逆模式时,它的处理速率达到40 Mb/s,不可逆模式下可达65 Mb/s.

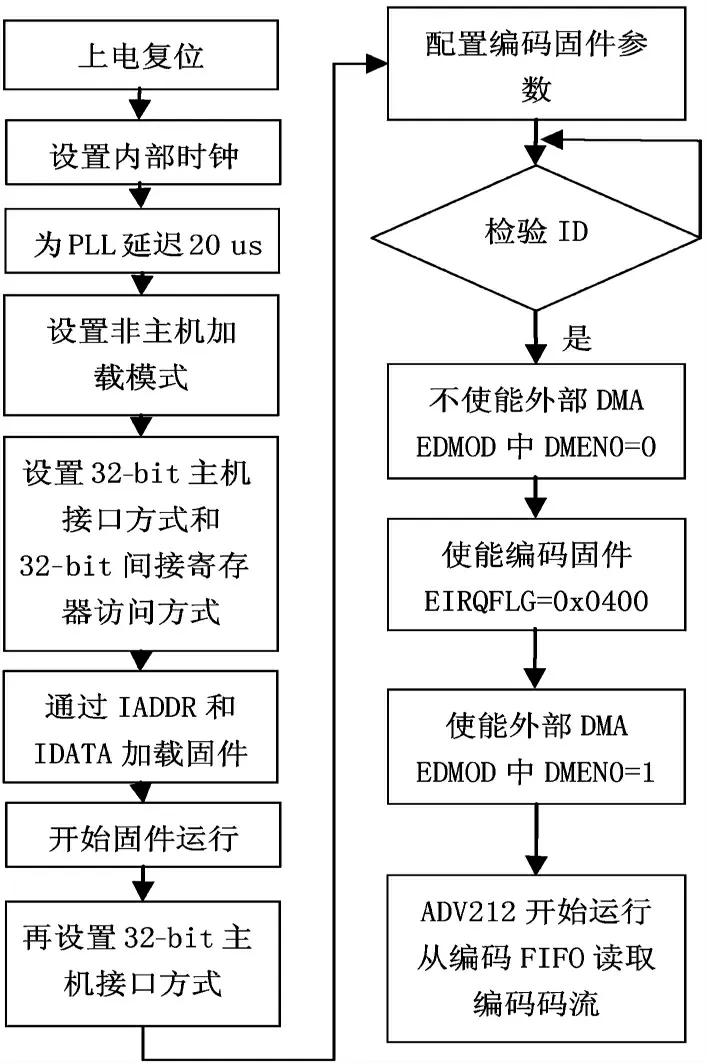

ADV212 芯片共有16 个直接寄存器、28 个可设置间接寄存器141.对ADV212 寄存器访问是通过ADDR[3∶ 0]、HDATA[31∶ 0]、CS、RD、WE 和ACK管脚实现,间接寄存器起始地址为0xffff0000.在特定模式如用户自定义模式下,需要通过IADDR、IDATA 寄存器访问设置间接寄存器.ADV212 的初始化流程为:①初始化直接寄存器(0x00-0x0F),设PLLLO,PLLHI 和总线宽度为16 bits;②软件重新启动,将0x8A 写到启动直接寄存器;③通过HDATA总线上载(Upload)ADV212 固件,大小为32 Kbytes[间接地址(0x00050000)];④配置固件参数,间接地址(0x00057F00-0x00057FFF);⑤再次初始化直接寄存器(0x00-0x0F),设PLLLO,PLLHI 和总线宽度(Bus size)为16 bit;⑥软件重启(Reboot)设PLLLO,PLLHI 和总线宽度(Bus size)16 bits,将0x8D 写到启动直接寄存器;⑦使能ADV212 中断并检查应用ID写0x0400 到外部中断使能直接寄存器(EIRQIE register)(直接地址为0x05 的软件中断0 位)来使能软件中断;通过读软件标识直接寄存器(SWFLG register,其地址为0x07)来检查应用ID 的正确性;⑧ADV212将如下值写到软件标识寄存器(SWFLG register):编码等于0xFF82;通过读取看这些值是否正确来判断固件是否;⑨正确导入ADV212;⑩清ADV212 中断;写0xFFFF 到外部中断标识直接寄存器(EIRQFLG register,地址为0x06)来清除所有的中断标识.

通过设置合适的中断使能位来使能外部中断使能寄存器(IRQ IE register),例如0x0002.系统的固件程序ADV212.sea 从ADI 公司网站下载获得[7],在本系统中通过USB 接口下载到ADV212 的间接存储器中,其地址段为0x00050000 ~0x0005EFF,数据宽度32 bit.采用C 语言的ADV212 程序编码流程如图3.

图3 ADV212 程序编码流程

2.3 码流加密及发送分模块

码流加密及发送分模式由数字信号处理器DSP(lTI 公司TMS320DM368 型DSP)和SDARM 组成,主要完成对ADV212 输出的标准JPEG2000 码流加密、存储、发送等操作.其硬件结构如图4 所示.

图4 压缩流存储及发送系统结构

ADV212 编码后产生的JPEG2000 格式码流首先送入DSP 进行算法加密,加密算法可以同接收端预先约定好[2].加密操作是必要的.对于码流的安全发送具有重要意义.加密后的码流存入图4 所示的SDRAM 中等待接收“传输”指令.TMS320DM368 型DSP 具有强大的挂接外设能力.本系统总共配备了512 Mbytes 的SDRAM,可以存储多帧图像的码流.

使用多线程及双队列缓存技术处理数据的接收与发送.接收线程查询空队列,当空队列有buffer时,从EMIF 接口接收压缩数据并存放在buffer 中,当接收完一帧新的压缩数据,将该buffer 加入满队列中.发送任务查询满队列,将满队列中的压缩数据通过以太网组播方式发送给计算机,计算机接收后解码播放显示.

2.4 记录格式与载体

1)ADV212 压缩码流格式.

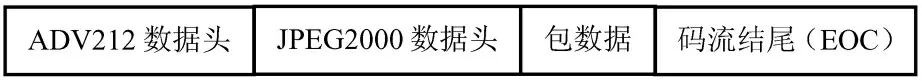

图5 压缩数据格式

ADV212 压缩数据组织形式如图5 所示,其中ADV212 数据头包含以下信息:场标记(Field identification);场数;文件格式;视频格式;数据头版本信息(Header version);压缩数据字数;属性数据字数.

2)JPEG2000 数据头包含整幅图像主文件头和图像块对应的头标记(Head makers).

SOC,码流开始 0xFF4F;EOC,码流结尾OxFFD9;COD,编码方式0xFF52;PLM,包长度,整幅图像的数据头0xFF57;PTL,包长度,每个图像块的头0xFF58;PPM,打包数据的头,整幅图像的数据头0xFF60;PPT,打包数据的头,每个图像块的头OxFF61;包数据(Packet data)即打包的数据流;码流结尾(EOC),每个码块由0x00 来填补,以达到32 bits 长的队列.

3 实 验

在实验中,对比了2 种不同码率下的效果.1.22 Mbps 码率(28.3∶ 1 压缩比)(见图6),283 K 码率(128∶ 1 压缩比)(见图7).

图6 压缩图(1.22 M)

图7 压缩图(283 K)

通过实验测试发现,基于JPEG2000 的压缩算法在128 K 码率下图像清晰、流畅、延迟小,具有良好的低比特率压缩性能,视觉失真很小,压缩率比较高.

测试验证了本硬件系统的可用性和正确性.

4 结 论

本研究设计了一个能对高分辨力图像进行实时压缩的系统.该系统结合DSP 的高度灵活性以及ADV212 的高效压缩特性,满足了系统高效灵活编码、码率控制等一系列复杂要求,很好解决了图像质量与实时性之间的矛盾.

[1]侯俊.Motion JPEG2000 视频编码技术研究[D].上海:上海交通大学,2007.

[2]路建方,王新赛,贺明,等.杜云基于ADV212 芯片的红外视频无损压缩研究[J].红外,2013,34(1):21-24.

[3]阮秋琦.数字图像处理学[M].北京:电子工业出版社,2001.

[4]张晓林,姚远.无人机载SAR 图像压缩传输中的关键技术研究[J].航空科学技术,2008,20(3):34-39.

[5]陈柠檬,刘雷波,张利.基于THJ2K 的JPEG2000 图像压缩系统[J].电视技术,2007,31(6):81-83.

[6]杨俊,鲁新平,李吉成.基于ADV212 芯片的视频压缩系统应用设计技术[J].微处理机,2010,31(4):119-122.

[7]Analog Devices Inc.ADV212 JPEG2000 video processor user's guide(revision 1.1)[S].Norwood,MA,USA:Analog Devices Inc.,2006.

[8]Taubman D S,Marcellin M W.JPEG2000 image compression fundamentals,standards and practice[M].MA:Kluwer Academic Publishers,2002.