基于CD4512逻辑数据选择器设计

喻文倩

摘 要:以CD4512八选一数据选择器作为核心元件,利用74LS161产生二进制的信号,当产生的信号与所需要的信号相同时,4512输出高电平(1),若与要求不相符则输出低电平(0)。文章就是以实验设计逻辑数据选择器的过程讲述了74LS161同步加法计数器与八选一数据选择器。

关键词:CD4512八选 一数据选择器 74LS161同步加法计数器

中图分类号:TN702 文献标识码:A 文章编号:1672-3791(2015)05(b)-0036-01

逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号相当于对数据进行塞选,选出符合要求的输送到下一级,其余的则被阻挡在上一级。还可以用于产生任意一种组合逻辑函数。

1 电路设计及计算

1.1 74LS161同步加法计数器

74LS161是常用的四位二进制可预置的同步加法计数器,一片74LS161可以组成16进制以下的任意进制分频器。时钟CP和四个数据输入端P0~P3;清零/MR;使能CEP,CET;置数PE;数据输出端Q0~Q3;以及进位TC.(TC=Q0·Q1·Q2·Q3·CET)。当CR=“1”且LD=“0”时,在CP信号上升沿作用后,输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样为同步置数功能。

1.2 CD4512八选一数据选择器

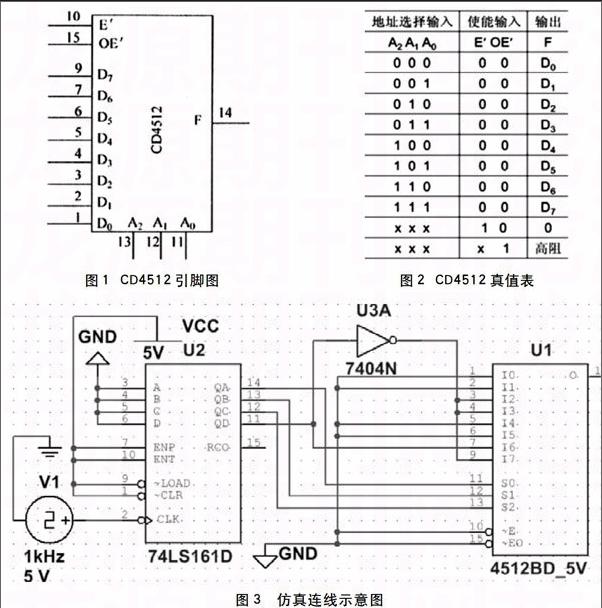

CD4512有8个数据输入端口D7—D0,一个数据输出端为F,A2,A1,A0为地址选择输入端,E'为使能输入端,OE'为三态输出使能端。当使能输入E'=0时,且当三态使能输出OE'=0时,数据选择器进入工作状态。其引脚图见图1,功能表见图2。

2 逻辑设计,仿真及结果

首先知道8选1逻辑数据选择器CD4512的逻辑输出函数表达式为

F=A2'A1'A0'D0+A2'A1'A0D1+A2'A1A0'D2+A2'A1A0D3+A2A1'A0'D4+A2A1'A0D5+A2A1A0'D6+A2A1A0D7由于题目要求当输入为2,3,7,14时输出为高电平,转换为二进制表达就是当CD4512输入端口接受的数据为0010,0011,0111,1110,是输出高电平。换成逻辑函数,也就是F=A2'A1A0'D2+A2'A1A0D3+A2A1A0D7。D2=D3=D7=1,D0= D1=D4=D5=D6=0这样只满足了题目要求的一部分,当输入为2,3,7时,输出为高电平,而当输出为1110,十进制数的14的时候,没有对应的输出,不满足题目要求。

考虑到74LS161计数器有是个4输出端口,但是CD4512只有3个输入端口,即是说,输入的数字范围在000~111,之间,即为0~7,不能符合要求,所以要把74LS161输出端的最高位Q3,接入CD4512的数据输入端口中。

通过观察输入的数据可以发现最高位除了14是1以外,其余的全部为0,所以考虑将Q3,接到CD4512中可以转换为14的数据上,即是0110十进制数为6的输入端口上。同时,将Q3的输出都过非门链接到需要输出高电平的数字上,即是说数据输入端口D2,D3,D7。这样接线图如图3所示:

这样一来,当74LS161产生的输出为0010,0011,0111时,由于最高位是0,又通过的非门连接到CD4512的数据输入端口上,这样输入端的数值就变味了1,也就是说,当输入为2,3,7时,CD4512的输出为1。当74LS161的输出为1110时,Q3由于直接与D6 相接,为高电平。而CD4512接收到的实际二进制数为110,十进制数6,此时,依旧会输出高电平。而当输入为1010,1011,1111时,有与最高位连接了非门,所以对应的CD4512上的端口数据为低电平,将不会有输出,避免了误操作,从而完成了题目的要求。按上述示意图连接后,仿真结果如图3所示:其结果与题目要求相符合,当输入为2,3,7,14时,输出为高电平,其余情况输出为低电平。

3 结语

利用CD4512,8选1逻辑数据选择器对数据进行选择性输出,同时还要考虑与其他元件的配合使用,就像该例中的, 74LS161的输出端口数目与4512输入端口的数目不相等,以及输入与输出数值的范围不一样时,要灵活运用一些基本的逻辑关系,与,或,非,进行适当的配合,最终达到题目的要求。

参考文献

[1] 惠永琴,汪希时.两种不同结构可修的ATP系统可靠性分析和比较[J].铁道学报,1995(S2):41-47.

[2] 姬小利,孟凡丽.面向供应链的ATP系统分析与计算[J].工业工程与管理, 2009,14(3):50-54.

[3] 陈宝安.芬兰铁路引进新型ATP系统──EBICAB900[J].铁道通信信号,1995(11):33-36.