星载测控数传一体化平台中CAN总线接口的FPGA实现

王 杰,李志强,朱文明,汤吉波

星载测控数传一体化平台中CAN总线接口的FPGA实现

王 杰1,2,李志强1,2,朱文明1,2,汤吉波1,2

(1.解放军理工大学通信工程学院,南京 210007;2.卫星通信与导航协同创新中心,南京 210007)

测控数传一体化是一种新的测控模式,该模式采用空间数据系统咨询委员会(CCSDS)的高级在轨系统(AOS)建议,将测控与数传功能合二为一,能够有效提高卫星的有效载荷比。针对应用于测控数传一体化应答机中的CAN总线,以FPGA为主控制器,SJA1000为CAN通信控制器实现其硬件接口电路,并采用VHDL语言进行CAN总线接口模块的设计与实现,仿真与测试结果表明,在该硬件平台上CAN总线的通信速率能达到500 Kbps,较好地满足了系统需求。

测控数传一体化;FPGA;CCSDS;CAN总线

0 引 言

CAN(Controller Area Network)即控制器局域网,是一种有效支持分布式控制与实时控制的串行通信网络。目前,由于其低成本、高可靠性、实时性、抗干扰能力强等特点,CAN总线在航空航天领域得到了越来越广泛的应用[1]。文献2在阐述微纳卫星测控通信统一系统的星上模块设计时简要介绍了CAN总线在微小卫星上的应用,论证了在微小卫星上应用CAN总线方案的可行性[2]。

为了满足卫星测控的多任务需求,新型的测控数传一体化应答机具备三种工作模式,工作模式的切换要求电路具有可重构性,因此选用可重复编程的FPGA作为主控制器,增强了硬件电路设计的灵活性和可扩展性。为限制硬件电路的体积、功耗,CAN总线接口模块的设计也通过FPGA实现[3]。文献3阐述了基于FPGA的CAN总线通信节点设计,由于应用场合的不同,该设计方案不满足星上数据传输的实时性要求且处理机制需要进一步完善。

在此背景下,本文针对应用于测控数传一体化应答机中的CAN总线,采用VHDL语言进行CAN总线接口模块的设计与实现,实现星上CAN通信数据的高速、实时、可靠传输。

1 测控数传一体化简介

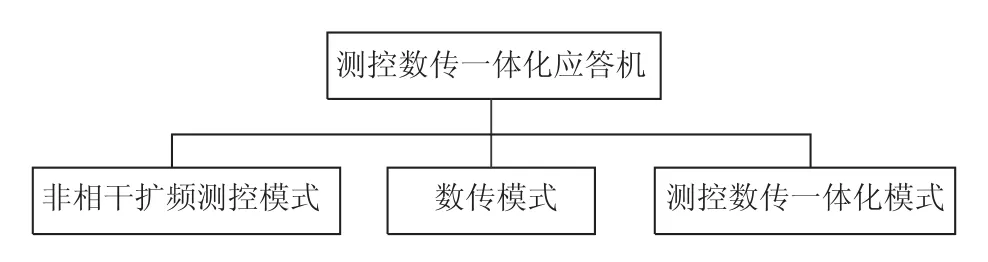

星载测控数传一体化应答机工作模式如图1所示,测控数传一体化应答机包含非相干扩频测控模式、数传模式和测控数传一体化模式,可根据指令完成工作模式的切换。

图1 测控数传一体化应答机工作模式

非相干扩频测控模式上、下行链路采用的调制方式都为PCM-CDMA-BPSK。数传模式上行链路采用非相干扩频测控体制,下行链路采用PCM-DQPSK调制方式。测控数传一体化模式内部集成了非相干扩频测控功能与高速遥测功能,上行链路仍采用非相干扩频测控体制,与非相干扩频测控体制相比,主要区别在于下行链路,测控数传一体化模式将2路下行发射通道改为1路测控数传综合信道[4],调制方式为PCM-BPSK,下行信息速率可达10 Mbps。该模式采用CCSDS AOS建议中定义的数据帧格式先将遥测信息、数传信息以TDM方式合路,测量信息采用CCSDSAOS建议的插入业务与遥测信息、数传信息合路为下行信息帧通过测控数传综合信道下行传输,这样可以同时满足遥测参数多样化以及遥测实时性越来越高的要求。

2 CAN总线在星上的应用

随着遥测参数多样化以及遥测实时性要求越来越高,考虑将高速、高可靠性的CAN总线引入卫星系统工程中,实现星上数据的高速率、高可靠性、实时传输以及卫星整体结构的优化。卫星上应用的CAN总线网络如图2所示。

CAN总线传输模式为主从模式,实现形式为一主多从,星载计算机作为主节点,卫星各分系统及分系统内部各设备作为从节点,主节点对从节点数据通信进行统一调度,禁止从节点之间的相互通信,各个节点有不同的节点地址,用以区分各节点的优先级解决总线冲突,节点地址越小优先级越高,同时通过对节点标识符的报文滤波即可实现点对点、一点对多点及全局广播多种通信方式。

图2 CAN总线网络

针对CAN总线在测控数传一体化应答机中的应用,CAN总线主要完成测控数传一体化应答机与星载计算机的通信,负责传输指令数据、遥测数据。指令数据由主节点发送给从节点,后经从节点发送给各执行机构执行指令,如发射机的开关、工作模式的切换等。遥测数据的传输是由主节点发送遥测请求指令给从节点,从节点接收到遥测请求指令后,返回该从节点的遥测数据。

测控数传一体化应答机中CAN总线硬件接口电路设计与文献3中的硬件接口电路类似,考虑到卫星的工作环境,采用A、B总线互为冗余备份的方式以提高系统的可靠性,同时将CAN通信控制器SJA1000以软核方式集成到FPGA中,无需在FPGA与SJA1000之间进行电平转换,在硬件电路上仅保留CAN收发器PCA82C250[5],极大程度上减小了硬件电路的体积、功耗,进一步提高了系统的可靠性。

3 CAN总线接口模块实现

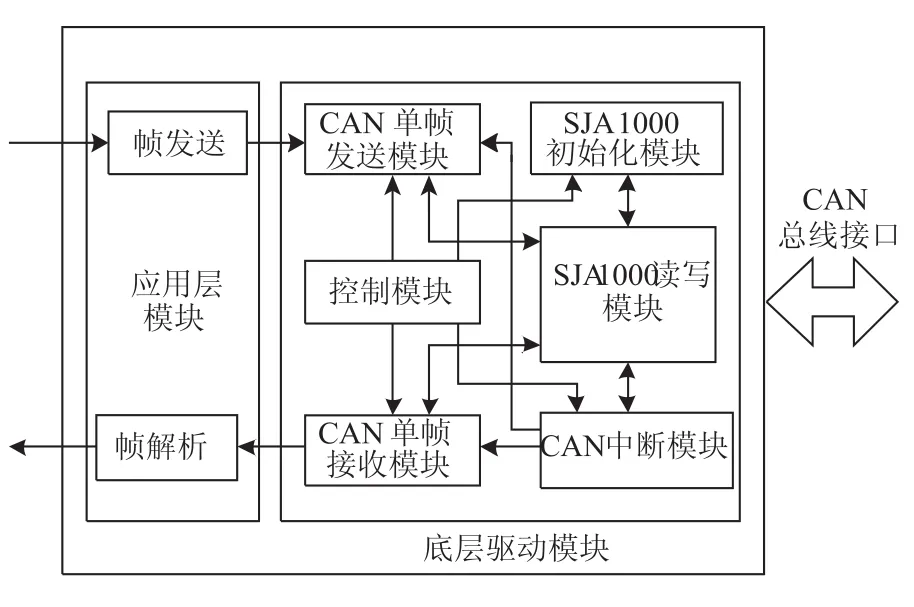

CAN总线接口模块按功能进行模块化设计与实现,实现框图如图3所示。笔者主要完成CAN通信控制器SJA1000底层驱动模块的设计与实现,底层驱动模块主要进行对SJA1000内部寄存器的读写操作,SJA1000初始化模块完成芯片在复位模式下相应寄存器的参数配置,初始化完成后,电路通过控制模块切换到中断处理模块。若未检测到中断,电路工作在查询发送状态,与应用层组帧发送模块交互获取报文,通过读写模块将报文写入SJA1000发送缓冲器并发送。若检测到接收中断,电路工作在中断接收状态,读写模块从SJA1000接收缓冲器中读取报文,并通过接收处理模块将数据送到应用层,由应用层的帧解析模块完成数据帧类型的判断[6]。

3.1初始化处理

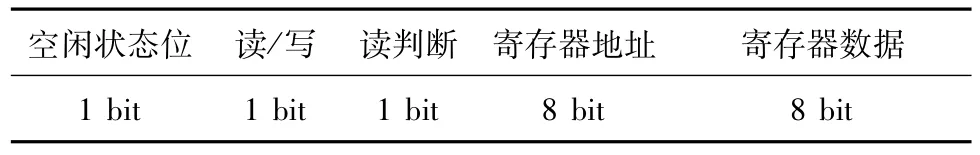

CAN总线工作的正常与否与总线状态密切相关,初始化模块是保证CAN总线具有正常工作状态的关键,故考虑采用读取ROM表的方式实现CAN通信控制器SJA1000的参数配置,以提高芯片参数配置的可靠性以及后期维护的便利性[7]。根据需要定义位宽为19 bit,深度可变的ROM表,数据格式如表1所示,在复位模式下进行SJA1000的初始化,需要配置模式寄存器MOD、时钟分频寄存器CDR、验收代码寄存器ACR、验收屏蔽寄存器AMR、总线定时寄存器BTR0、BTR1、输出控制寄存器OCR以及中断使能寄存器IER等[8]。

图3 CAN总线接口模块实现框图

表1 ROM表数据格式

系统上电后,采用软件复位方式产生一个复位脉冲复位CAN总线接口。空闲等待SJA1000进入复位模式,配置CDR使SJA1000工作于PeliCAN模式,同时将接收输入比较器旁路以减少内部传输延迟,增加正常通信的总线长度。接收器采用双验收滤波器模式,配置ACR、AMR使该从节点只接收主节点的数据。

采用ISO11898 CAN高速应用标准,通过配置BTR0、BTR1将CAN通信波特率设置为500 Kbps。最后配置OCR使SJA1000工作于正常输出模式,输出引脚配置为推挽输出。进入工作模式后,配置IER开启所需中断[9]。

3.2发送报文处理

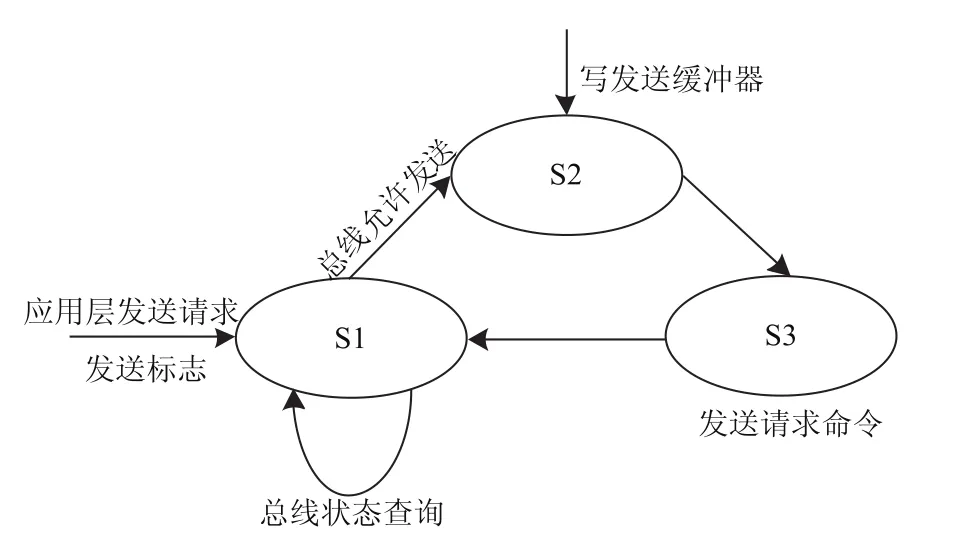

采用查询控制方式实现报文的发送,主要采用状态机完成单帧发送流程,状态转换图如图4所示。检测到应用层发送请求后,周期查询状态寄存器,并判断发送缓冲区是否锁定、上次发送是否完成以及是否正在接收报文,当总线处于允许发送状态时,单帧发送模块与CAN应用层组帧发送模块交互获取长度为11字节的标准数据帧,再与读写模块交互将报文写入SJA1000的发送缓冲器,最后置位命令寄存器的发送请求TR标志位完成报文的发送[10]。

图4 发送模块状态机

3.3接收报文处理

由于星上数据量较大,且为了满足星上数据通信实时性的要求,故采用中断控制方式实现报文的接收,单帧接收过程在一个中断子程序中完成,同样采用状态机完成单帧接收流程,状态转换图如图5所示。如果SJA1000已接收一个报文并且该报文已通过验收滤波器并存放在接收FIFO里,就会产生一个接收中断,主控制器FPGA检测到接收中断后能立即作用将收到的报文发送到FPGA内部的存储器,然后通过置位命令寄存器的释放接收缓冲器RRB标志位完成报文的接收。

图5 接收模块状态机

3.4中断处理

在本文的CAN总线接口模块设计中,中断处理模块是底层驱动模块的核心,提供发送、接收标志以及中断、异常状态处理功能。区别于文献3中在接收处理之前进行异常状态处理,本文将中断处理以及异常状态处理作为一个单独的模块,简化了各个模块的功能以及复杂度,使得各模块功能更加明确。

CAN通信控制器SJA1000进入工作模式后,开启需要处理的中断源:总线错误中断BEI、仲裁丢失中断ALI、数据溢出中断DOI以及接收中断RI。初始化完成后,中断处理模块不断检测SJA1000中断输出INT管脚电平,检测到低电平就执行中断处理进程,检测到高电平就执行查询总线状态进程,中断处理流程如图6所示。

图6 中断处理模块流程图

(1)中断处理:SJA1000允许同时产生多个中断,因此需要考虑多个中断同时产生的情况,首先定义中断寄存器的8个中断源优先级从高位到低位逐渐降低,屏蔽其中4个与异常状态相关的中断源,按照优先级顺序依次对BEI、ALI、DOI与RI进行处理,BEI、ALI是PeliCAN模式下新增的中断源,通过读取错误代码捕捉寄存器ECC、仲裁丢失寄存器ALC获取总线错误类型和位置信息以及仲裁丢失的位置信息完成对BEI、ALI的处理。DOI的处理需要通过置位命令寄存器的CDO标志位清除数据溢出中断。最后处理RI,产生一个接收标志启动接收模块。

(2)异常状态处理:需处理的异常状态包括总线关闭状态以及总线错误计数器超过错误报警限制EWLR后的总线出错状态,针对异常状态的处理,底层驱动模块产生一个错误标志送给应用层,请求应用层复位整个CAN底层驱动模块。

3.5控制模块

控制模块通过各个模块的指示信号实现模块间的切换,从而避免了各个模块之间信号复杂的相互交互。控制模块实现对其他模块的控制,仅在其他模块电路需要工作时,才切换到相应的模块,从而达到降低功耗的目的。

3.6仿真与验证

采用VHDL语言进行电路设计,使用ISE软件进行电路的功能仿真、逻辑综合、布局布线和物理验证等设计。需要对CAN底层驱动模块的单帧发送、单帧接收、中断处理以及各模块之间的切换等过程进行仿真测试以及硬件验证。

硬件测试时将星上用于冗余备份的两个CAN总线接口电路作为CAN总线网络上的两个节点,一个作为主节点,另一个作为从节点,进行单帧发送、接收测试。硬件测试平台如图7所示。

图7 硬件测试平台

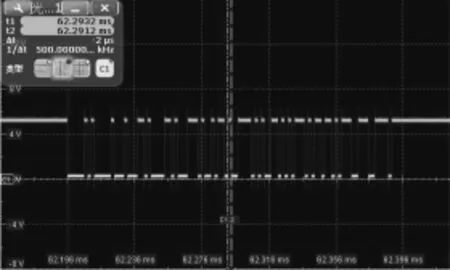

图8 CAN数据帧

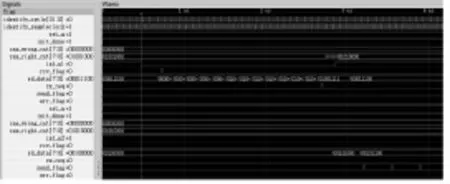

图8为指令数据经过SJA1000成帧处理后在物理线路上传输的实际波形,符合CAN协议中定义的CAN数据帧结构[11],测试结果表明在该硬件平台上,CAN总线通信速率可以达到500 Kbps,同时将应用层发送的数据帧与自环测试接收的数据帧进行比对,测试该通信速率下CAN总线数据传输的误码率,图9为主从节点双向收发测试时通过基于RTL级的在线调试工具Identify[12]获取的误码率测试结果,遍历发送各指令数据、遥测数据测试误码率,数据帧错误计数器始终为0,满足星上数据传输的可靠性要求。

4 结 语

本文按功能进行模块化设计,能够简化各模块的功能,相比较之前的CAN总线通信节点的设计实现,在处理机制上作了改进,优化了程序设计的结构,实现的功能更加全面,且在项目要求的CAN通信波特率为500 Kbps时误码率较低,满足星上数据传输的可靠性、实时性要求。将CAN总线应用于测控数传一体化应答机及整星上,可以实现星上数据的高速、实时、可靠传输以及卫星整体结构的优化。

图9误码率测试

[1] 李正军.现场总线及其应用技术[M].机械工业出版社,2005.

[2] 徐璐,陈金树.微纳卫星测控通信统一系统的研究与实现[J].微计算机信息,2007,23(2):96-98.

[3] 张培坤,高伟,宋宗喜,陈楚君.基于FPGA的CAN总线通信节点设计[J].仪表技术与传感器,2012,(12):68-70.

[4] 于志坚,丁溯泉,罗伦.航天测控与数传接收综合信道构想[J].遥测遥控,2002,23(4):8-11.

[5] PCA82C250 CAN controller interface Data sheet.Philips Semiconductor Corporation,1997.

Im p lementation of CAN Bus Interface in FPGA Based on TT&C Platform

WANG Jie1,2,LIZhi-qiang1,2,ZHUWen-ming1,2,TANG Ji-bo1,2

(1.Institute of Communication Engineering,PLA University of Science and Technology,Nanjing 210007,China;2.Satellite Communication and Navigation Collaborative Innovation Center,Nanjing 210007,China)

Integration of TT&C system is a new mode which adopts CCSDS Advanced Orbiting Systems,can effectively improve the utility of satellite payload.Aimed at the application of CAN bus in TT&C transponder,CAN interface circuit is based on core controller FPGA and CAN controller SJA1000.The design and implementation of CAN bus interfacemodule is described by using VHDL,simulation and test results show that CAN communication rate can achieve 500 Kbps,preferablymeet the system requirements.

TT&C;FPGA;CCSDS;CAN bus

TN47

:A

:1673-5692(2015)06-593-05

10.3969/j.issn.1673-5692.2015.06.006

2015-07-30

2015-09-26