基于RapidIO的相控阵短波发信系统交换单元设计*

邓 冉,高 俊,屈晓旭

(海军工程大学 电子工程学院,湖北 武汉 430033)

基于RapidIO的相控阵短波发信系统交换单元设计*

邓 冉,高 俊,屈晓旭

(海军工程大学 电子工程学院,湖北 武汉 430033)

传统总线技术成为了制约短波通信系统性能进一步提升的瓶颈。RapidIO总线是一种新型嵌入式总线,具有传输效率高、系统成本低、系统稳定性好等特点。基于RapidIO技术设计了相控阵短波发信系统的交换单元,硬件上进行了系统供电电路、时钟电路和交换芯片端口电路设计;软件上主要介绍了RapidIO初始化和交换芯片的远程配置两个方面。在实际应用中实现了系统中各模块间信号的高速交换。

RapidIO;短波通信;交换单元;TSI578

0 引 言

短波通信被广泛的应用于军事、商业、气象等领域用来传输文字、语音、图像等数据信息。随着数字信号处理技术和微电子技术的飞速发展,短波通信的重要作用日益凸显出来。数字信号处理器(DSP)的发展和广泛应用使短波通信的数字化程度得到极大提升[1]。随着新的短波通信技术的应用,通信速率不断提高,对数字化通信系统的性能要求也越来越高。数字处理器件的处理速度平均翻一番需要18个月,而总线速率提升一倍需要三年,因此总线的速度也成为了制约短波通信系统性能增长的瓶颈[2]。相控阵短波发信系统模块多并且复杂程度高,因此要求总线尽可能的简单管脚尽可能的少。同时由于涉及到天线组阵时多路信号的交换,这务必要求总线传输速率足够高。RapidIO总线是一种新型嵌入式总线,采用差分串行传输,相对传统总线具有引脚少的优势,使得系统硬件设计时更加简单,资源利用率更高,成本更低,稳定性更好。该总线采用交换结构,支持点到点或点到多点的串行传输,运用8B/10B编码将时钟嵌入数据中。基于以上这些特点本文设计的相控阵短波发信系统交换单元选择RapidIO总线为板间信息传输总线,以实现系统中信号串行速率达1.25 Gb/s的高速信号交换。

1 RapidIO技术简介

RapidIO技术是由Motorola和Mereury Computer公司共同开发的一项高速互联技术。RapidIO是国际标准组织(ISO)和国际电工委员会(IEC)一致通过的互连规范。RapidIO协议分为物理层、传输层和逻辑层。物理层是这个协议的最底层,它定义了并行和串行两种协议。并行LVDS协议能够使系统的内部紧密耦合在一起,能够支持250 MHz、500 MHz、750 MHz及1 GHz工作频率;串行协议则在对于引脚数目限制和长距离传输的系统中得到运用,支持1.25G、2.5G、3.125G、5G、6.25G 等5种比特率,传输性能可从1 Gb/s到20 Gb/s[3]。逻辑层是协议的最高层,它定义了消息传递协议、数据流协议、I/O逻辑操作协议、流量控制协议以及全局共享存储协议。中间的传输层能够实现用统一包格式来传输数据,既支持点到点的传输也支持广播的传输方式[4]。

2 系统整体框架设计

相控阵短波发信系统按照各自功能可以分为5个单元,分别为调制解调单元、相位检测单元、波束控制单元、交换单元和上变频单元。调制解调单元主要进行基带信号的处理;相位检测单元主要进行射频信号相位的检测,并把检测结果交予波束控制单元;波束控制单元进行多路射频信号相位的控制;上变频单元进行频率搬移使信号能发射出去。各个单元通过光纤连接交换单元,在交换单元中进行信号的交换与传输。每个单元各自完成自己的功能,相互之间没有影响,这样分工明确,结构清晰方便系统的维护以及问题的排查[5]。系统框架见图1。

图1 系统框架

3 交换单元硬件设计

由于DSP编程方式灵活,具有很强大的数字处理功能同时能进行灵活的控制。因此交换单元采用的DSP芯片是TI公司的TMS320C6416芯片。DSP芯片在本系统中的主要作用是对交换芯片进行初始化、复位和配置,同时对各个单元发过来的数据进行解析然后进行相应操作。交换单元中的FPGA芯片采用的是StratixⅡ GX系列芯片,它的功能是提供与RapidIO相连的接口。交换单元硬件框见图2。

图2 交换单元硬件框

交换单元选择Tsi578芯片完成RapidIO协议的交换。Tundra公司开发的第三代RapidIO交换芯片Tsi578目前在市面上应用广泛。它支持全双工串行RapidIO交换,支持符合开放式标准及第1.3版串行RapidIO互连规范[6]。根据系统方案需求,将Tsi578配置为16个1x端口模式,串行速率为1.25 Gb/s。

3.1 供电电路设计

外部给系统统一提供的电源为5 V。5 V 电压在交换单元中通过电压转换芯片转变为DSP和FPGA需要的工作电源。DSP和FPGA需要的工作电源是1.2 V和3.3 V。1.2 V是用于DSP和FPGA的逻辑处理,3.3 V用于提供DSP和FPGA内部锁相环(PLL)的驱动电压以及FPGA相关管脚上的逻辑1电平。

DSP和FPGA的3.3 V电压供电电路相同。由外部统一提供的5 V电源经过LC电路,最后通过TOS0605SM电源转换芯片得到3.3 V电压。再由并联电路把电压送到各个芯片。在转换得到的电压与最终输出的电压之间有一个过流保护电阻,用来防止电路电流过大,起到保护芯片的作用。

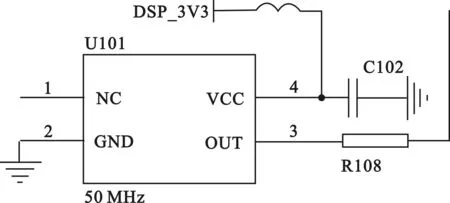

3.2 时钟电路设计

DSP的时钟供给电路如图4所示。DSP的时钟由本地晶振产生50 MHz的时钟,经过一个过流保护电阻和DSP需要的三个时钟,BECLKIN、DSPCLK、AECLKIN对应的引脚相连。

FPGA的时钟供给电路如图5所示。

外部输入一个400 MHz时钟,通过时钟芯片SY89202U转化成两路100 MHz,经过两个电容隔去直流后,作为FPGA的两个时钟输入CLKp和CLKn。

图4 DSP时钟电路

图5 FPGA时钟电路

3.3 Tsi578芯片端口电路设计

Tsi578芯片端口电路图如图6所示。在短波通信系统中,我们采用串行协议,需要将芯片配置工作在1x模式下。Tsi578芯片共有16组1x模式端口,图6中显示有8组,另外8组与之相同。

图6 578芯片端口电路

4 交换单元软件设计

交换单元中软件设计包括DSP和FPGA两个方面。FPGA中软件设计核心是利用Quartus已有的IP核实现RapidIO协议,利用SOPC(可编程片上系统)[7]编程将DMA和RAM等资源有机地结合在一起,实现RapidIO接口,此外还提供接口转换功能为DSP管理RapidIO和交换芯片提供通路。DSP只需要完成命令和数据的接收与解析,对本地和远程的RapidIO系统的维护,门铃的发送,交换芯片的配置等功能。

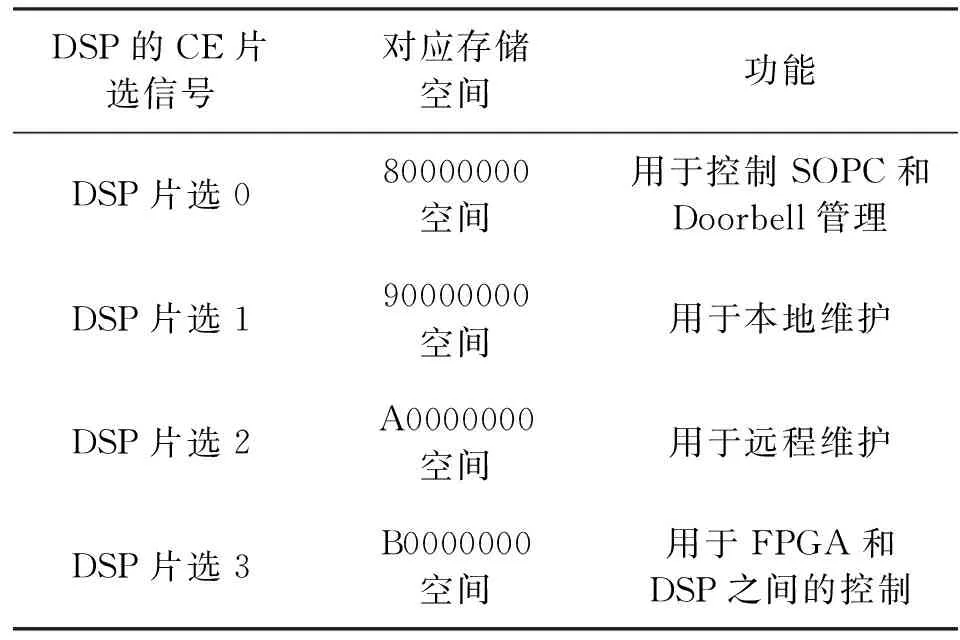

交换单元DSP空间分配如表1所示。

表1 DSP空间分配

RIO模块接口如图7所示。

图7 RIO接口

交换及控制单元中远程终端通过RapidIO模块接口与Tsi578进行交互。RapidIO模块接口由RapidIO IP核[8]、RAM、DMA控制器、并行总线接口转换器子单元经特定的逻辑相互连接构成。在交换及控制单元中,RapidIO模块只需完成主控命令的接收与维护交换芯片的信息的发送,不需要进行基带数据的发送和接收。

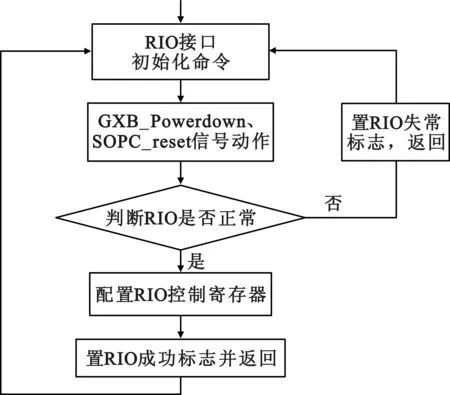

RapidIO初始化软件流程如图8所示。系统收到RapidIO初始化命令,然后通过一系列信号的变化判断RIO是否正常。即首先置GXB_powerdown=‘1’,等待2 ms,置GXB_powerdown=‘0’,再置SOPC reset=‘0’,等待2 ms,置SOPC reset=‘1’。之后判断RapidIO状态寄存器中RapidIO状态标志,如果RapidIO状态非正常,置RapidIO失常标志并返回;如果RapidIO状态正常,则配置RapidIO控制寄存器,并置RapidIO成功标志并返回。

图8 RIO初始化

远程配置是交换单元中特殊功能,其流程如图9所示。主控下达配置Tsi578的命令,DSP首先判断本地RapidIO接口是否正常,如果不正常,则置RapidIO失败标志返回;如果正常则将Tsi578复位,并判Tsi578寄存器是否正常,如果不正常则置失败标志返回;如果正常则打开Tsi578的通道,配置其LUT表,并置配置成功表示返回。

图9 578芯片远程配置

5 RapidIO数据传输速率测试

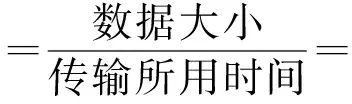

系统配置完毕以后,由DSP不断向RapidIO口写入1,0,DSP向FPGA发起DMA操作传输数据是通过EMIFA口,数据大小为128Byte。系统在RapidIO口为1的时候为空闲状态,在RapidIO口为0的时候传输数据。

由图10可知低电平的持续时间是1.1 μs,高电平是200 ns,即在低电平的持续时间内完成了128 byte的数据传输。又由于物理层采用8B/10B编码,因此可以算出实际的传输速率:

图10 RapidIO口时序

通过与理论值比较可以看出,本文设计的交换单元基本能够达到设计的速率要求。

6 结 语

随着科学技术的发展,短波通信系统数字化程度越来越高,使用的技术越来越复杂,这对数据的传输速度和性能有了更高的要求。RapidIO总线技术在短波通信系统中的应用越来越广泛。本文设计的相控阵短波发信系统的交换单元在实际应用中能够实现多路信号的高速交换,下面的研究就尝试着把RapidIO总线技术应用到收发一体化的相控阵短波通信系统中。着重解决交换速度和性能的进一步提高,同时尝试使用578交换芯片更高速的交换模式。

[1] 廖娜.DSP应用技术综述[J].IT技术论坛,2008(32):78. LIAO Na.DSP Application Technology Summary[J].IT Technology Forum, 2008 (32):78.

[2] 李少龙,高俊,娄景艺.基于SRIO总线的数字信号处理系统的实现[J].通信技术,2012,45(05):101-103. LI Shao-long, GAO Jun, LOU Jing-yi. Implementation of Bigital Signal Processing System based on SRIO Bus[J].Communication Technology, 2012,45 (05):101-103.

[3] Copyright RapidIO Trade Association.RapidIOTM Interconnect Specification Part 6: LP-Serial Physical Layer Specification [EB/OL].12343 Hymeadow, Suite 2-R (non-US mail deliveries to Suite 3-E) Austin, TX 78750 ,2011.

[4] 邓豹,赵小东.基于串行RapidIO的嵌入式互联研究[J].航空计算技术,2008(05):123-126. DENG Bao, ZHAO Xiao-dong. Research on Embedded on Interconnection of air based on serial RapidIO[J].Aviation Computing Technology,2008(05):123-126.

[5] 杨春顺.基于RapidIO总线通信系统交换单元的设计与实现[J].计算机与数字工程,2014(06):1003-1006.YANG Chun-shun. and the realization of Design of RapidIO Bus Communication System based on Switching Unit[J].Computer and Digital Engineering, 2014 (06): 1003-1006.

[6] Tundra corporation.IDT Tsi578 Serial RapidIO Switch User Reference Manual[EB/OL].6024 Silver Creek Valley Road San Jose, California 95138,2009.

[7] 周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006. ZHOU Li-gong. the Basis of.SOPC Embedded Systems Tutorial [M]. Beijing: Beihang University Press, 2006.

[8] Altera Corporation.RapidIO MegaCore Function User Guide [EB/OL].101 Innovation DriveSan Jose, CA 95134,2009.

Design on Exchange Unit of Phased-Array Shortwave Transmitting System based on RapidIO Bus

DENG Ran,GAO Jun, QU Xiao-xu

(College of Electronic Engineering, Naval University of Engineering, Wuhan Hubei430033, China)

The traditional bus technology now becomes a bottleneck in further enhancing the control performance of shortwave communication system. RapidIO bus,as a new type of embedded bus, features high transmission efficiency, low system cost, good system stability etc.. The paper describes the phased-array shortwave communication system platform constructed in DSP and FPGA, including the design of TSI578 chip based on RapidIO switching unit. Hardware design mainly involves the system power circuit ,clock circuit, and port circuit of the switching chip. As for the software, two aspects including RapidIO initialization and remote configuration of the switching chip are introduced. The unit can realize high-speed signal switching of among various modules in the practical application of exchange.

RapidIO; shortwave communication; switching unit; TSI578

date:2014-10-09;Revised date:2015-02-18

TN91

A

1002-0802(2015)04-0495-06

邓 冉(1991—),男,硕士研究生,主要研究方向为数字通信;

高 俊(1957—),男,教授,主要研究方向为数字通信、无线通信;

屈晓旭(1976—),男,副教授,主要研究方向为数字通信、无线通信。

10.3969/j.issn.1002-0802.2015.04.022

2014-10-09;

2015-02-18