基于FPGA+DSP的双核控制器硬件设计

王国栋,马晓军,袁 东,杨怀彬

(装甲兵工程学院,北京 100072)

基于FPGA+DSP的双核控制器硬件设计

王国栋,马晓军,袁 东,杨怀彬

(装甲兵工程学院,北京 100072)

在设计高实时性的系统时,针对基于DSP、单片机等串行运算方式的单核控制器无法实现高实时性的问题,利用FPGA的并行运行优点构建了基于DSP+FPGA的双核控制器,以达到提高系统实时性的目的。通过分析系统总体结构,主要设计完成了系统总线构架、DA电路、CAN总线和PROM电路,然后通过软件编程来验证硬件设计。经调试分析,该系统各部分运行正常,可为研究设计高实时性的控制器提供参考和借鉴。

FPGA,控制器,并行,高速总线

0 引言

在设计高实时性的系统时,基于DSP、单片机等串行运算方式的单核控制系统难以满足高实时性的要求。若采用并行构架的FPGA实现DSP功能或FPGA与DSP协同控制,系统可以实现大量数据并行运算,提高系统实时性[1-2]。文献[3-4]中基于FPGA的高速信号处理平台均验证了并行构架的FPGA提高系统实时性的可行性,对设计基于DSP+FPGA的双核控制器提供了理论支持;本文所设计的DSP+FPGA的双核控制系统采用DSP来实现系统顶层复杂控制算法部分,采用FPGA来实现系统底层计算量大、实时性要求高的数据处理部分,这样发挥了DSP和FPGA各自的优势,从而满足数字系统信号实时处理的要求。

1 系统总体结构

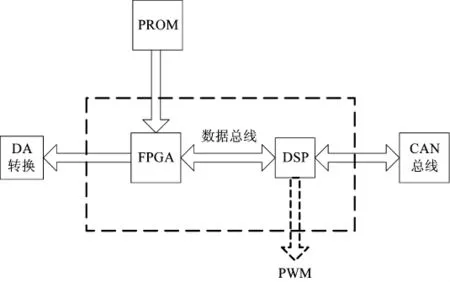

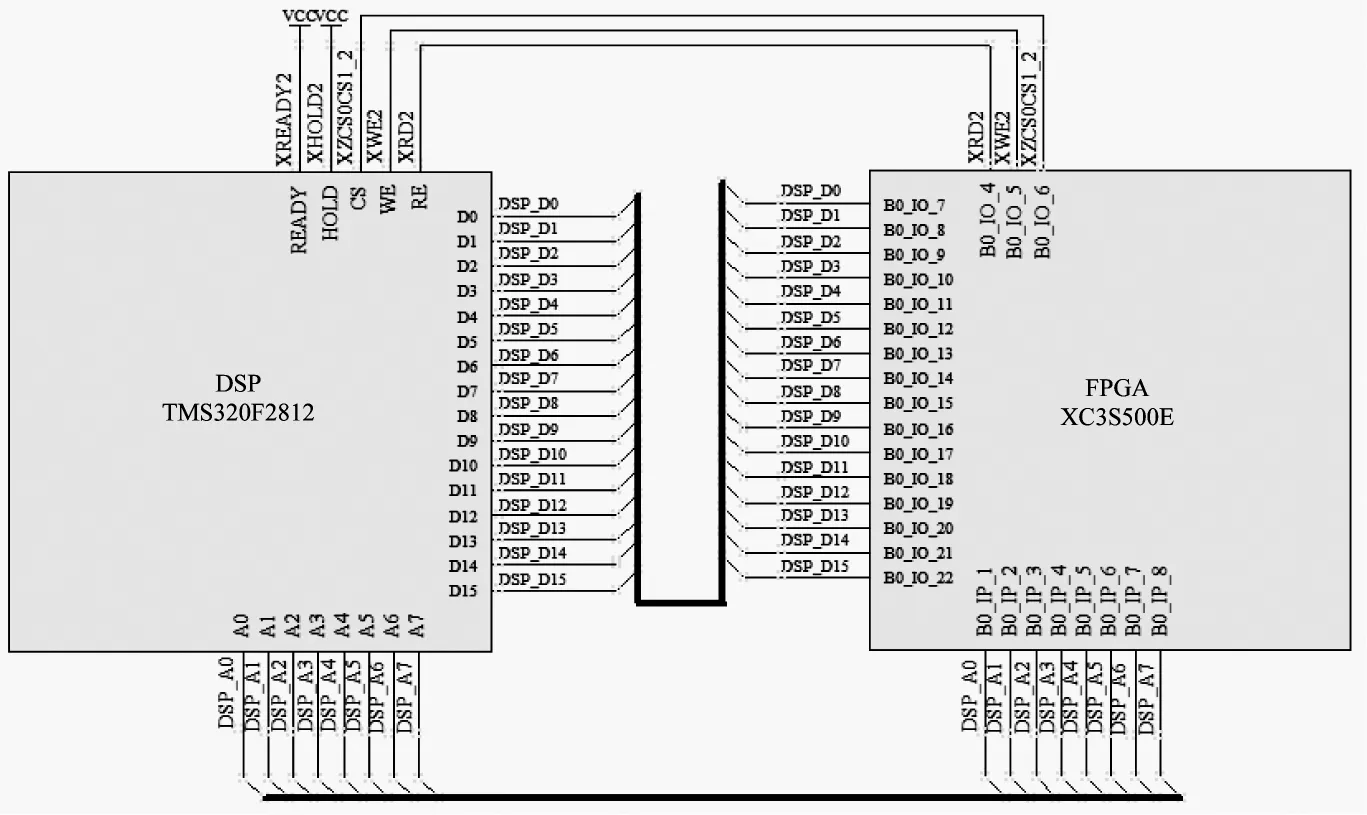

系统中的 DSP采用了适合控制运算的TMS320F2812,FPGA则采用了适合作为DSP辅助处理器的Spartan3E系列的XC3S500E[5],图1为系统结构图。系统由DSP、FPGA、PROM、DA转换电路以及CAN总线组成。①DSP用于实现系统顶层复杂的控制算法,并输出PWM等控制信号;②FPGA用于实现系统底层大量的高速信号的实时处理,FPGA与DSP通过高速总线相连,实现数据的高速交互;③PROM用于存储FPGA的程序,防止程序掉电丢失;④DA转换电路用于将FPGA内部的数字信号转换输出,以便于系统测试,方便系统控制,系统包括6路DA电路,DA电路由FPGA直接控制,使FPGA替DSP分担了底层并行信号的实时处理;⑤CAN总线用于实现DSP与外界的通信。

图1 系统结构图

2 系统设计

2.1 DA输出电路设计

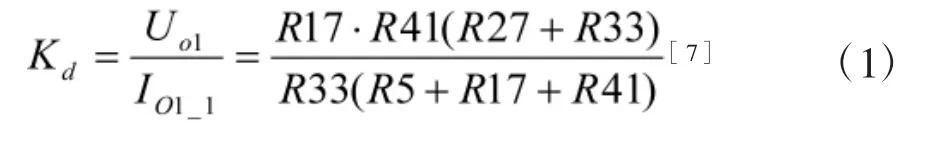

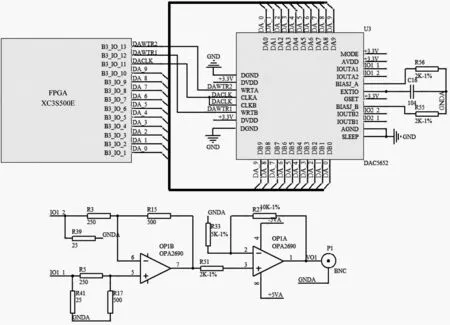

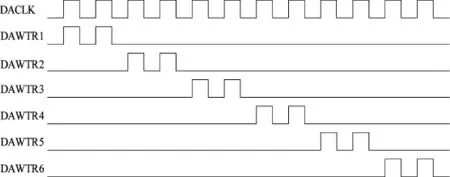

DA输出电路由DA转换电路和差分放大电路组成。DA转换芯片选用DAC5652[6]。DAC5652是一种双通道、电流型的10位DA转换芯片,图2以1片DAC5652为例分析系统的DA设计;其结构如图2所示,当MODE管脚为高时(3.3 V),DAC5652工作在双通道模式;DA输出电路共用一条数据总线和一个转换时钟(DACLK),每路DA电路有各自独立的片选信号(DAWTR1/DAWTR2);转换时钟(DACLK)和片选信号(DAWTR1/DAWTR2)由FPGA控制依次有序输出,从而保证6路DA电路有正确的工作时序,如下页图3所示。差分放大电路选用运放OPA2690,电路差模放大倍数如式(1)所示。

图2 DA输出电路

2.2 DSP与FPGA间的总线构架

为了实现DSP与FPGA的信息交互,系统采用如下页图4所示的总线构架。DSP和FPGA之间共有1组高速数据地址总线(DSP_D/DSP_A)和读写、片选等控制信号(XRD/XWE/XZCS)[8]。其中:①地址总线用于实现DSP在FPGA内寻址,其中地址总线的高4位(DSP_A7-DSP_A4)用于确定片外存储器的地址,将DSP的片外存储地址指向FPGA的内部缓存,低4位(DSP_A3-DSP_A0)用于确定DSP进行读写操作的具体地址,即DSP的地址信号指向了FPGA内部缓存的哪一个地址,因此,低4位地址线(DSP_A3-DSP_A0)决定了DSP共指定了16个片外存储地址;②数据总线用于实现DSP和FPGA之间数据的高速交互;③信号XZCS用于指定DSP的片外存储器;④信号XWE用于控制DSP对FPGA进行写操作;⑤信号XRD用于控制DSP对FPGA进行读操作。

图3 DA工作时序

在该总线构架中,FPGA单独进行数据运算,并控制着DA电路依次有序输出,DSP通过高速地址总线来指定读写FPGA内缓存的数据,然后通过高速数据总线来进行数据交互。

图4 DSP与FPGA间的总线构架

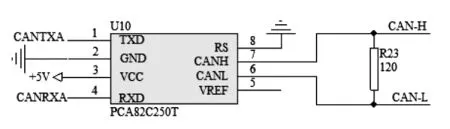

2.3 CAN总线的设计

用CAN总线实现数据通信具有突出的可靠性、实时性和灵活性,CAN总线采用多主串行通信协议,具有较高的安全性,可以有效地支持分布式实时控制[9]。系统CAN总线设计如图5所示,CAN总线控制器选用PCA82C250T实现数据的收发。TXD为数据输入控制端,用于实现数据的发,TXD和RXD通过电压转换后与DSP相连;RXD为数据输出控制端,用于实现数据的收;CANH/L用于高/低压总线数据的传输,用于实现与外界通讯。

2.4PROM设计

FPGA是基于SRAM的可编程器件,掉电后FPGA上配置的信息将全部丢失,因此,需要ROM为FPGA存储信息。PROM的设计如图6所示,TMS用于JTAG输入模式选择;TCK用于JTAG时钟的输入;TDI用于JTAG串行数据输入;TDO用于JTAG串行数据输出。在下载FPGA程序时,使用JTAG模式配置bit文件,然后用bit文件转换为prom文件下载到PROM里,当系统上电时,将程序配置到FPGA里。

图5 CAN总线设计

图6 PROM设计

3 设计验证

3.1 验证DSP与FPGA之间的通信

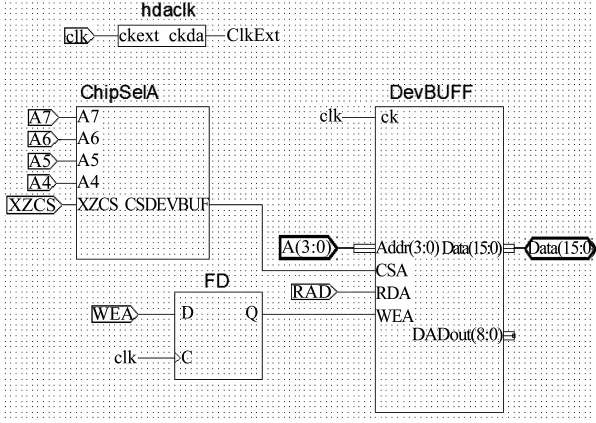

为了验证DSP与FPGA之间的通信设计,在ISE中创建一个简单的读写工程。读写工程用于在FPGA内部构建地址译码模块和数据缓存模块,当FPGA收到DSP发出的地址和控制信号后,地址译码模块将收到的地址信号进行翻译,使DSP能够读写数据缓存模块中地址信号所指定的数据。工程的顶层设计如图7所示。

图7 DSP与FPGA通信

图7 包括分频程序模块(hdaclk)、片选程序模块(ChipSelA)、缓存程序模块(DevBUFF)和D触发器(FD)。片选程序(ChipSelA)是采用逻辑运算式(2)来指定DSP的外部存储(FPGA)的地址;

缓存程序(DevBUFF)内部构建了16个地址缓存,每个地址缓存中都存储有一个16位的二进制数,程序通过读(RDA)、写(WEA)信号以及地址信号(A(3:0))来判断读写缓存器内的某个数,读写的数据通过数据总线Data(15:0)与DSP进行交互,最终实现DSP与FPGA间的通信。经试验验证,DSP可以顺利读写FPGA内指定地址的信息。

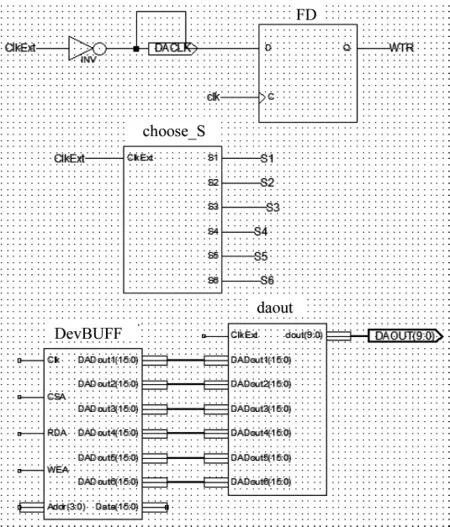

3.2 验证DA输出

由于系统的6路DA电路是共用与FPGA相连的数据线总线,因此,在进行设计验证时,我们必须保证FPGA为各个DA电路依次有序的提供数据信号、片选信号以及转换时钟信号,使片选信号和转换时钟信号满足图3对工作时序的要求。软件工程的结构框图如图8所示。

图8包括DA选择程序模块(daout)、片选选择程序模块(choose_S)和控制信号生成模块。dout模块和choose_S模块分别控制着数据信号和片选信号的选择输出,即控制6路DA的输入数据和片选信号依次按顺序输出,同时确保当某个DA的数据信号来时,片选信号同时到达;控制信号生成模块是用于生成DAC5652所需的时钟(DACLK)和片选信号(WTR),并确保两个信号为图3所示的正确工作时序。

图8 DA程序框图

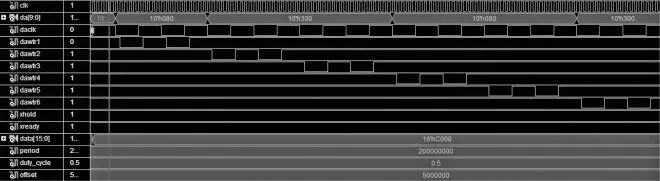

对上述工程进行仿真验证[5],仿真结果如图9所示。

图9 DA输出仿真

通过图9看到FPGA为DA芯片提供的时钟信号(daclk)和片选信号(dawtr)与图3的工作时序相同,表明DA电路工作正常。综上所述,各个DA端口能够依次有序输出系统指定的数据信号。

4 结论

通过软件调试,验证了设计DSP+FPGA的双核控制器的可行性,这种构架的控制器发挥了DSP和FPGA各自的优势,增强了系统实时处理数据的能力,十分适合实时性要求高的系统,是构建高实时性系统的一种有效设计。

[1]杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-727.

[2]Kuon I,Rose J.Measuring the Gap Between FPGAs and ASICs[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2007,26(2):203-215.

[3]付志红,马静,谢品芳,陈清礼.基于高速数字信号平台的实时仿真技术[J].系统仿真学报,2007,19(16):3680-3684.

[4]李乐,熊志辉,王斌,等.DSP+FPGA折反射全景视频处理系统中双核高速数据通信[J].电子与信息学报,2010,32(3):649-654.

[5]谈世哲,李健,管殿柱.基于Xilinx ISE的FPGA/CPLD设计与应用[M].北京:电子工业出版社,2009.

[6]DAC5652技术手册[S].www.ti.com.

[7]童诗白,华成英.模拟电子技术基础(第四版)[M].北京:高等教育出版社,2006.

[8]刘和平,刘平,王华斌,等.数字信号控制器原理及应用——基于TMS320F2808[M].北京:北京航空航天大学出版社,2011.

[9]杜春洋,王宇超.零基础学TMS320F281x DSP C语言程序设计[M].北京:机械工业出版社,2010.

Design of Dual Core Controller Based on FPGA+DSP

WANG Guo-dong,MA Xiao-jun,YUAN Dong,YANG Huai-bin

(Academy of Armored Forces Engineering,Beijing 100072,China)

In the design of the high real-time system,for single core controller,such as DSP,singlechip,which is based on the way of serial arithmetic is difficulity to achieve high real-time.In this article,the advantages of FPGA which is parallel running to constructed the dual core controller which based on DSP and FPGA is utilized,in order to improve the real-time performance of the system. Through analysis of the overall structure of the system,the design of the bus architecture of the system,DA circuit,CAN bus circuit and PROM circuit are completed,then using the software to verification the design of hardware.After debugging and analysis,each part of the system is in normal operation,which can provide reference for design the high real-time controller.

FPGA,controller,parallel,high speed bus

TP391.9

A

1002-0640(2015)04-0165-04

2014-01-05

2014-03-19

王国栋(1990- ),男,山东泰安人,硕士研究生。研究方向:电力电子与电力传动。