数字化多通道射频鉴相器设计与实现

吴 拓,曾繁荣,温佳隆,郑文波

(华航无线电测量研究所,北京100013)

数字化多通道射频鉴相器设计与实现

吴 拓,曾繁荣,温佳隆,郑文波

(华航无线电测量研究所,北京100013)

多通道微波射频鉴相器是被动导引头及无源定位装置普遍使用的一种鉴相装置,在整个系统里起着决定性的重要作用。基于高速采样芯片及数字信道化接收技术,设计实现了一种工作稳定可靠、相对成本较为低廉的数字化多通道射频鉴相器。

数字化;微波鉴相;FPGA

0 引言

传统的多通道微波鉴相器由高中频前端以及中频鉴相电路、数字信号采样处理电路等部分组成,其优点是技术难度低、较为成熟,数字信号处理部分设计较为容易,对数字系统要求较低。其不足也很明显:需要昂贵的高中频前端,目前微波、模拟电路及组件的价格一般占到整个侦查导引设备成本的一半或者更多;系统构成环节多、结构复杂、并且通道间幅相校正极为困难;可移植性、通用性、灵活性很差。

针对上述传统设备的弊端,本文基于高速采样芯片及数字信道化接收技术设计实现了一种工作稳定可靠、相对成本较为低廉的数字化多通道射频鉴相器,并已在实际中得到了应用。

1 基本原理

1.1 鉴相器应用背景

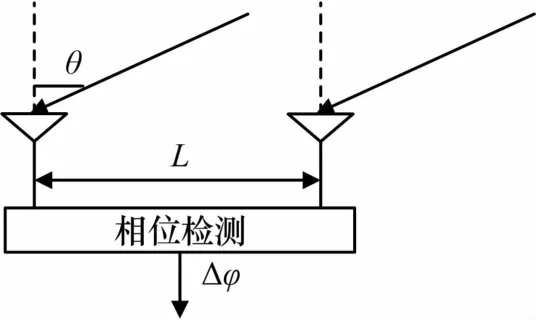

鉴相器主要应用于相位干涉仪测向系统。干涉仪具有设备简单、测角精度高的优点,在无源定位等方面具有重要的应用价值。如图1所示,以θ角度入射的电磁波对应的相位差为Δφ=2π/λL sinθ。如果能够以便捷、可靠的手段求取相位差,即可计算出电磁波入射角度θ。

图1 相位干涉仪原理示意图

1.2 信道化接收机原理简述

宽频带信道化接收机基本结构为低通滤波器组结构,即将完整频谱内各个频带的信号分多路变换到基带,然后共用一个预先设计好的低通滤波器进行滤波,可以恢复出各个信道的基带信号。

低通滤波器组结构当信道数较多时,低通滤波器的通带截止特性要求非常陡峭,阶数会很高,根本不适合硬件实现。

由软件无线电中常用的多相滤波结构可以很容易地对低通滤波器组结构的数字接收机进行改造,使之适用于实际电路。这就是实用性信道化接收机的基本原理。

2 硬件电路设计

2.1 电路基本构成

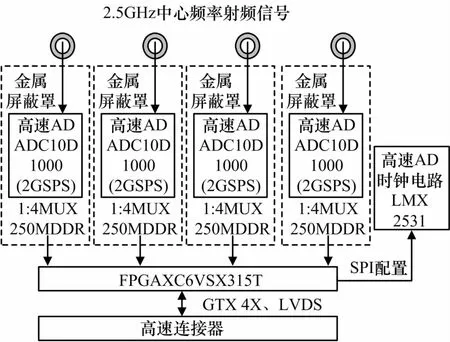

鉴相器电路主要构成部分是高速采样AD芯片、高性能FPGA和数字信号处理器。

由于馈入的射频信号频率较高,例如中心频率为2.5 GHz的宽频带信号,在进入数字鉴相器之后需要立即进行数字化处理,结合数字信道化接收机理论,电路采用2 GSPS带通采样,AD芯片选用带有AutoSync锁相同步功能的ADC10D1000。该AD芯片的特点是:解析位数为10位;转换速率为单路2GSPS采样;有效位数为9.1位(典型值);无杂散动态范围为70 dBc;功耗为双采样通道同时工作2.77 W;具有AutoSync自动同步功能;带宽为2.8 GHz。

该型号AD芯片的Full Power Bandwidth为2.8 GHz,可以满足对2.5 GHz中心频率、600 MHz带宽的射频信号的接收处理需求。

电机以及传动系统的设计要求保证下料装置运转平稳和运动传递准确,常用的传动方式有链传动和同步带传动等方法。链传动方式传动效率高,轴间距离适应范围大,没有弹性滑动和打滑,能保持准确的传动比;但是传动精度较低,瞬时链速和瞬时传动比不是常数,传动平稳性较差,工作中有一定的冲击和噪声,若装配不好,容易掉链。同步带传动精度高、效率高,相比链传动成本有所增加。为保证传动系统的平稳性和精度,改善设备性能,本设计采用同步带传动方法。

射频信号转换成数字信号后,数据码流速率非常高,每片AD芯片具有4路DDR输出,每路的数据率达到了500 MSPS。唯有基于多相滤波器组的数字信道化接收机可以并行将4路共2GSPS数据率的数字信号转换成基带信号,并将数据率降低至FPGA可处理的范围。FPGA型号选用Xilinx公司的Virtex6系列,高速差分管脚较多,并且逻辑资源非常丰富,适合实现多路结构复杂的信道化接收机。

图2 数字化射频鉴相器硬件基本构成图

图3 数字化射频鉴相器硬件基本构成图

带通采样后,信号频谱“折叠”至第一奈奎斯特区间,此时通过多相滤波器组对采样之后的信号进行低通滤波,以实现抗频谱混叠的目的。

电路采用GTX高速链路将计算结果传至下一级电路进行信号分选处理。硬件基本构成如图2所示。

2.2 电路工作原理及难点

鉴相器电路将馈入的射频信号通过模数转换为高速数字信号,AD芯片所需的采样时钟为1 GHz,由LMX2531系列PLL+VCO集成芯片产生。

高速采样数据经过串并转换和重组后,送入多相滤波器组形式的信道化接收机进行处理,信道化接收机输出各路信号的频率、相对应的相位、幅度等信息。

将各通道计算结果同频率信号的相位对应相减结果及幅度、频率等信息一并计算,通过高速GTX链路传输给下一级处理板,进行信号分选等处理。以上计算及传输均在FPGA片内完成,信道化接收机的优势在于可将宽频带内的多个同时到达信号的幅度、相位差全部计算出来,处理批次和效率都要优化很多。图3为FPGA内部程序结构框图。

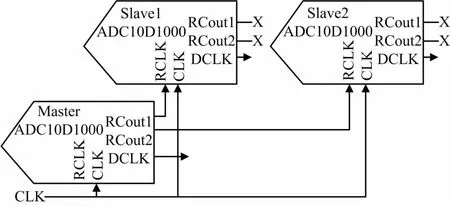

电路设计调试的难点在于高速AD的同步、程序配置、数据的接收、信道化接收机调试等。多通道高速AD的同步对于多路射频鉴相非常重要,直接关系到鉴相系统的测量误差和性能。AD10D1000在芯片级就实现了多片(多通道)的精确同步采样,基于PLL的同步采样时钟控制使得硬件工程师的数据同步工作难度大大降低,并且没有高低温环境下同步调整时序错乱的顾虑,具备较好的环境适应性和稳定性特点。

图4为高速AD自动同步采样功能示意图。其中有一片是主芯片,带有2个参考时钟RCout输出,可以以二进制树的形式接入很多从芯片,从芯片依据RCLK输入进行采样时钟的动态调整,从而保证精准的片间同步。

需要说明的是,Xilinx公司Virtex6系列FPGA在接收类似这种高速AD输出的DDR(AD随路时钟双沿均有数据)数据时,必须使用BUFIO时钟针对IOcolumn数据进行锁存,才能达到较好的效果,这对电路设计及FPGA编程人员也构成了较大的挑战,必须十分熟悉芯片内部的结构,从而在管脚分配和代码编写上有所讲究。

2.3 瞬时工作带宽及动态范围

该射频鉴相器的瞬时工作带宽为600MHz,这个带宽与微波前端、AD芯片的采样率、全功率带宽均有关联,是一个系统设定参数。鉴相器的瞬时工作带宽B不大于微波前端的频带宽度Bw,同时B<fs/2,fm<FPBW,这里fs为AD芯片采样率,fm为输入信号的最大频率,FPBW为AD芯片的全功率带宽。

该射频鉴相器的动态范围主要由AD芯片的全频带有效位数决定,主要难点在于小信号的接收处理,因为AD芯片的有效位数是一定的,10位解析度的高速AD芯片,其在全工作频段上的平均有效位实测为6位左右,即单板动态范围在36dB的水平。有的频率下有效位数较高,达到7位多,但并不能作为整个鉴相器产品的系统参数。

GHz级别高速采样AD普遍有效位数不高,导致单板动态范围受限、小信号检测能力受到影响,为弥补此缺陷,往往通过系统设计的方式来解决,在微波前端内加入带有带通滤波的低噪声放大器,将微弱信号的功率及信噪比调整到信道化射频鉴相器可以接受的范围,以此来达到整机的技术指标要求。

2.4 多通道射频鉴相器工程实用性和优点简述

该射频鉴相器依靠GHz级别高速采样芯片、大规模可编程器件、软件无线电的方式进行设计,参数设定灵活、便捷,开发周期短。其采样率、中心频率、工作带宽等均可通过更改FPGA软件来确定。在被动侦收、测向装置等产品上具有较广阔的使用前景。并且由于普遍采用了工业级数字器件,处理过程在FPGA及DSP中完成,其在环境适应性、相位稳定性上较传统产品具有较大的优势。

目前常见的高速数字鉴相器一般采用微波前端+高中频前端+中速AD数字鉴相的方式设计,微波前端+高中频前端这一级的成本往往占到整机成本的40%~60%,且采用超外差式接收,送给数字信号处理器的信号频率往往需要降至几十MHz,其响应速度、可同时处理的频带宽受限。

多通道射频鉴相器直接在高中频环节对射频信号进行采样,将高中频前端这一环节省略,不仅大大降低成本,其瞬时带宽、处理目标的数量也比超外差式高速数字鉴相器大得多。

图4 高速AD自动同步采样功能示意图

3 结束语

本文所述的数字化多通道射频鉴相器已应用于型号产品,减小了产品体积和功耗、降低了产品成本、缩短了研发周期,并取得了较好的效果。未来随着AD器件技术水平的提升以及SOC技术的进步和普及,将有可能将多通道射频鉴相器制作成SOC产品,具备较高的采样频率、较好的动态参数、极佳的通道一致性以及小体积、低功耗等优势。■

[1] Daniel RZ,David LS,Timothy WF.A hardware-efficient,multirate,digital channelized receiver architecture[J].IEEE Trans.on Aerospace and Electronic Systems,1998,34(1).

[2] 吴拓.侦察接收一体式宽带数字接收机设计[J].航天电子对抗,2009(6):43-46.

[3] 杨小牛,楼才义,徐建良.软件无线电原理及应用[M].北京:电子工业出版社,2001.

The design and realization of digital multi-channel phase detector

Wu Tuo,Zeng Fanrong,Wen Jialong,Zheng Wenbo

(Huahang Institute of Radio Measurement,Beijing 100013,China)

The multi-channel microwave phase detector is widely used in passive ladar guider and passive seeker,which plays an important role in the whole system.A digital multi-channel microwave phase-detector is designed and realized based on high-speed AD and digital channelized receiver theory,which is more reliable and cheaper.

digital;micro wave phase detector;field-programmable gate array

TN97

A

2015-03-16;2015-05-15修回。

吴拓(1982-),男,高工,硕士,主要研究方向为高速电路及数字接收机。