基于1 pps时间基准信号的授时装置设计

肖 龙,赵秋明,许丰灵

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

基于1 pps时间基准信号的授时装置设计

肖 龙,赵秋明,许丰灵

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

针对1 pps时间基准信号在时间同步中的应用,研究了一种基于1 pps时间基准信号的授时装置。通过对器件选型、参数设定,调制器等关键部分的详细分析,设计了一种基于1 pps时间基准信号的授时装置,主要包括基带编码、预处理电路、调制电路、功率放大电路。该装置具有授时精度高、成本低、功耗小、便携式等优点,满足时间同步的应用需求。

1 pps;授时;时间同步

随着导航、通信、电力等技术的进步,越来越多的工程和科学领域需要时间统一[1]。而时间源是时间统一系统的时间参考基准,一个时间源对应着一个外部时间基准信号。1 pps信号是一种典型的时间基准信号,其上升沿对应着精确的UTC时刻。目前,时间同步方式主要有网络协议和授时型接收机两种方式,而网络传输存在不确定性延迟和阻塞,并不能满足时间精度要求高的场合。利用授时接收机进行本地时间同步,虽然时间精度高误差小,但成本高[2]。文献[3]中提出了基于1 pps时间基准信号来实现节点间时间同步的方法,即通过转发1 pps时间基准信号和本地信息来实现节点间的时间同步,但仅限于理论研究。本文依据文献[3]中的理论,从工程应用的角度设计了一种基于 1 pps 时间基准信号的授时装置,能够满足时间同步的工程应用需求。

1 1 pps时间同步原理介绍

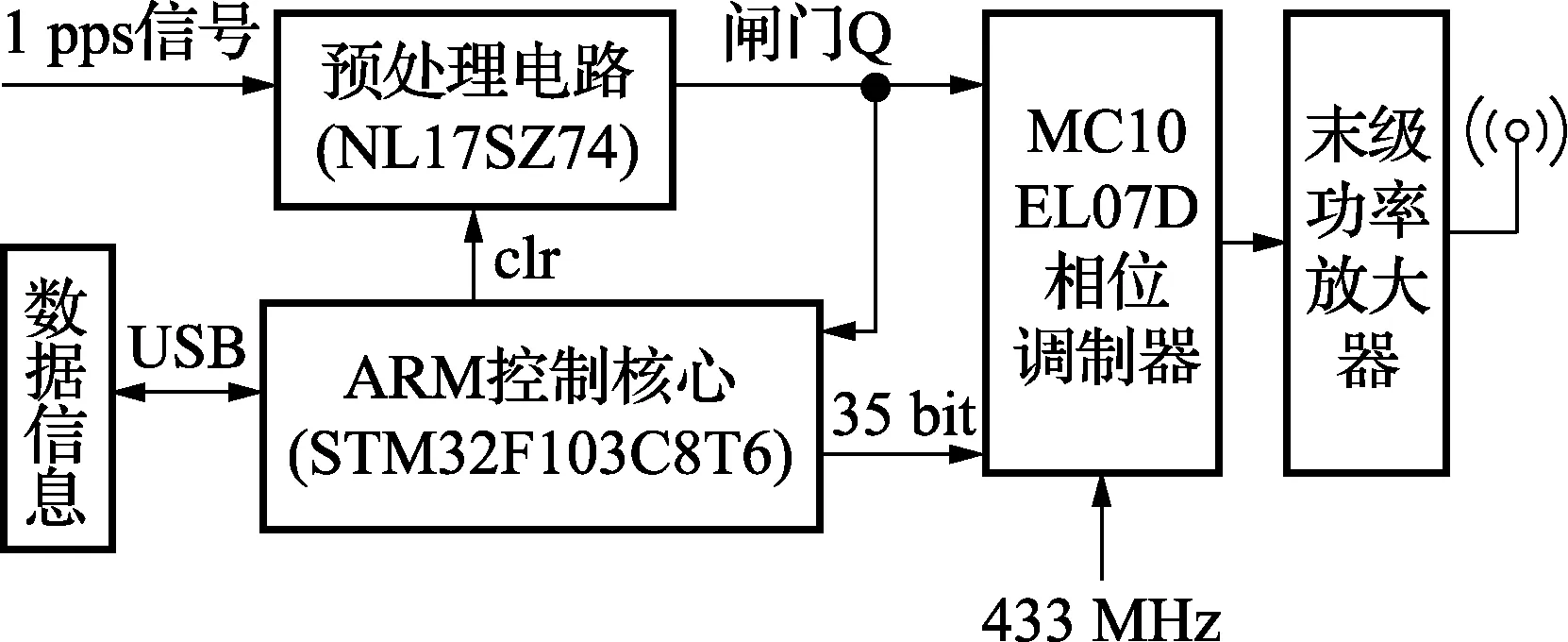

如图1所示,发送方广播本地授时型接收机的1 pps时间基准信号和数据信息进行授时,接收方从接收的信息中恢复1 pps时间基准信号和数据信息,实现与发送方的时间同步。据此,本文设计了一种基于1 pps时间基准信号的授时装置,其原理框图如图2所示。

图1 时间同步原理框图

图2 1 pps授时装置框图

装置的工作流程:在待机时刻,STM32单片机从PC机端加载35 bit信息,预处理电路等待外部1 pps时间基准信号的上升沿时刻。在其上升沿到来之前,相位调制器输出未调相的载波信号,经过末级功率放大后发送。在其上升沿到来时刻,闸门信号Q触发STM32F103C8T6单片机产生35 bit信息,开启相位调制器直接调相,经过末级功率放大后发送,首个相位跳变点对应第一个1 pps时间基准信号上升沿时刻。

2 授时装置设计

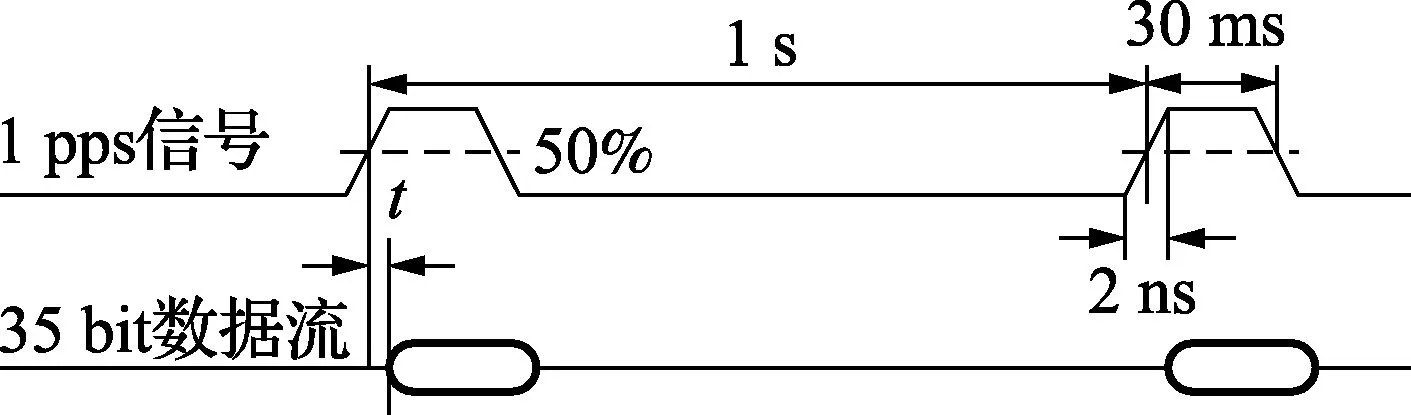

1 pps时间基准信号传输时序如图3所示,授时装置在 1 pps 时间基准信号的上升沿时刻,转发本地35 bit信息,1 pps 时间基准信号的上升沿标识了本地信息的当前时刻,从而实现授时。其中1 pps信号的脉宽时间为30 ms,上升沿持续时间为2 ns,发射功率为18 dBm。1 pps时间基准信号的上升沿与发送首位数据信息之间的时间延迟t决定了授时精度,t越小,授时精度越高,t越大,授时精度越低[3]。

图3 1 pps时间基准信号传输时序图

2.1 预处理电路

微处理器的响应速度影响着装置的时间延迟指标,为了使微处理器能够精确地响应1 pps时间基准信号的上升沿时刻,需要根据以下具体要求选择合适的单片微处理器芯片[4]:

1)中断响应速度。周期T与频率f之间满足关系T=1/f,而1 pps时间基准信号的上升沿持续时间为2 ns,则上升沿持续时间对应的频率为f=500 MHz,若需要响应这一频率的上升沿时刻,则要求处理器的响应频率f≥500 MHz。

2)指令执行速度。在闸门信号Q的上升沿时刻,微处理器I/O口产生35 bit信息,若从响应其上升沿到装置发送首位已调信息之间的时间延迟为纳秒级,则要求微处理器的 I/O 口的响应速度和指令执行速度至少在纳秒级。

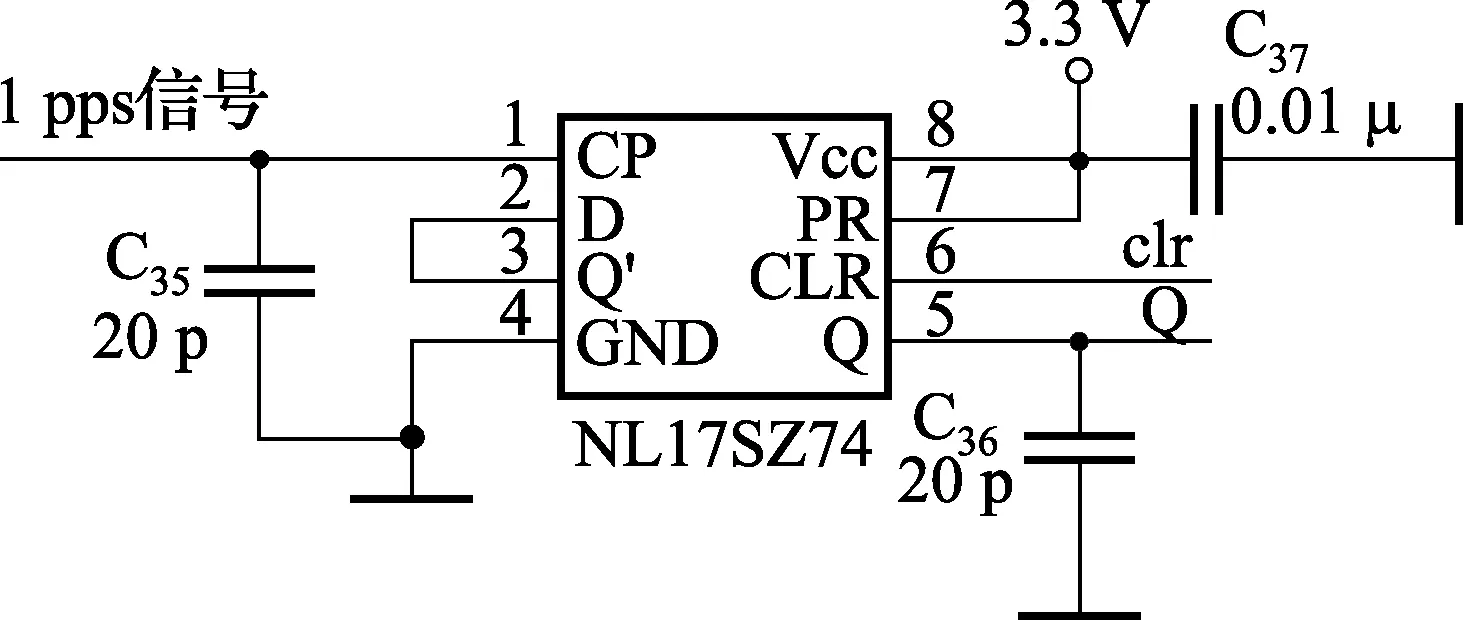

综合考虑以上具体要求,选用意法半导体的STM32F103C8T6单片机,工作电压为+3.3 V,时钟频率最大为72 MHz,中断响应时间小于6个机器周期,指令执行速度为1.25 DMips/MHz,I/O口的响应时钟频率最大为50 MHz,显然满足条件2),但无法满足条件1)。为满足条件1)的要求,采用D触发器对1 pps时间基准信号进行预处理,得到信号Q,STM32单片机捕捉到信号Q后开始响应产生35 bit信息,同时开启调相器就临近载波相位调相[5]。发送完末位比特数据后,STM32向D触发器发送清零信号,此时Q=0,调相器停止相位调制,输出未调相的载波信号。

预处理电路原理图如图4所示,选用NL74SZ17作为超高速D触发器,工作电压为+3.3 V,传输时间延迟为2.6 ns,典型上升沿持续时间为1.5 ns,满足条件1)。

图4 预处理电路原理图

2.2 相位调制电路

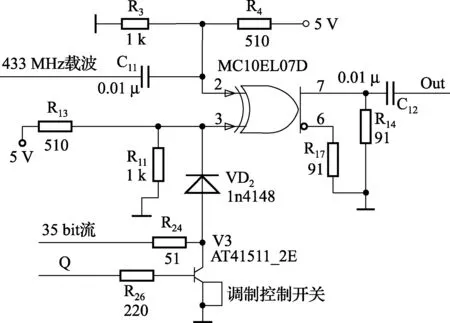

为了解决1 pps时间基准信号的调制响应速度问题,设计了一种简易的超高速数字异或门相位调制器,直接对模拟载波信号和基带信号进行相位调制。异或门实现相位调制的原理参见文献[6],本文不再赘述。

相位调制电路原理图见图5,选用MC10EL07D作为异或门,工作电压为+5 V,两输入端逻辑“1”表示的电压范围为3.87~4.19 V,逻辑“0”表示的电压范围为3.05~3.52 V。为了能够实现模拟信号与数字信号的直接调制,需要设定异或门的静态工作点,输入端均需要+3.3 V的直流偏置电压,使得调相器工作在逻辑“0”状态,输出端通过电容耦合隔直流,得到交流信号。Q信号高电平期间,输出已调相信号,低电平期间,输出载波信号。

图5 相位调制电路原理图

2.3 功率放大电路

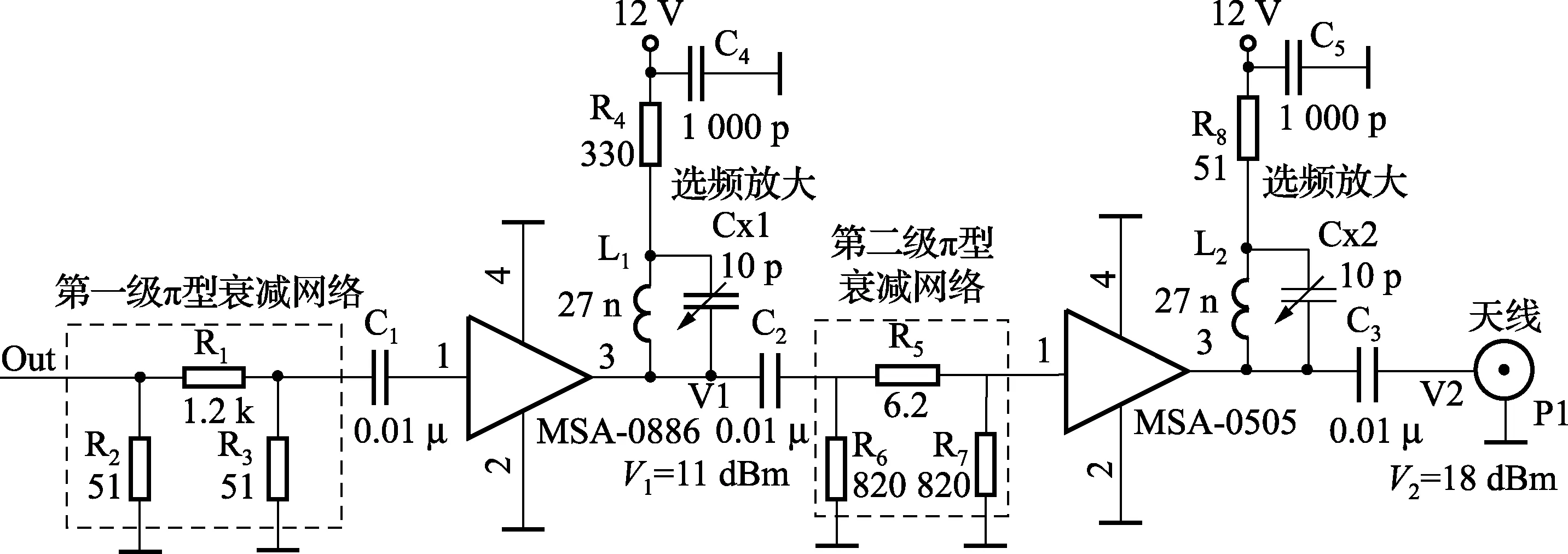

由于工作于ISM(工业、科研及医疗)频段的近距离无线通信免通行证[7],因此本文选定的无线通信频率点为433 MHz。

功率放大电路原理图如图6所示,相位调制器输出的信号为数字信号,故需要在放大器中加入谐振选频网络,选择出433 MHz的已调相模拟信号。为确保信号的纯净性,在两级放大器中均加入谐振选频网络,谐振网络的L与C之间的关系满足

(1)

图6 功率放大电路原理图

依据式(1),取f=433 MHz,C=5 pF时,L=27 nH。实际应用时,电感L=27 nH,电容C选用1~10 pF的微调电容。

由于相位调制器输出信号的峰峰值约1 V左右,为了避免信号在放大时出现饱和失真,同时获得较为理想的驻波比,因此需要在放大器输入端插入阻抗特性为50 Ω的π型电阻衰减网络。实际应用中,第一级衰减网络的参数为R1= 1.2 kΩ、R2=R3=51 Ω,第二级衰减网络的参数为R5=6.2 Ω、R6=R7=820 Ω。

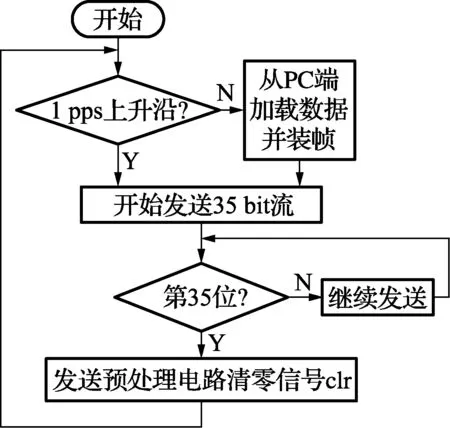

3 软件设计

整个软件的主程序流程图如图7所示,装置以STM32F103C8T6为控制核心,待机时,STM32从PC机端加载本地35 bit数据并完成装帧,等待1 pps时间基准信号上升沿时刻,在其上升沿响应输出35 bit数据,发完末位比特数据后,对预处理电路清零,等待下一个1 pps时间基准信号上升沿时刻,以此为周期工作。

图7 主程序流程图

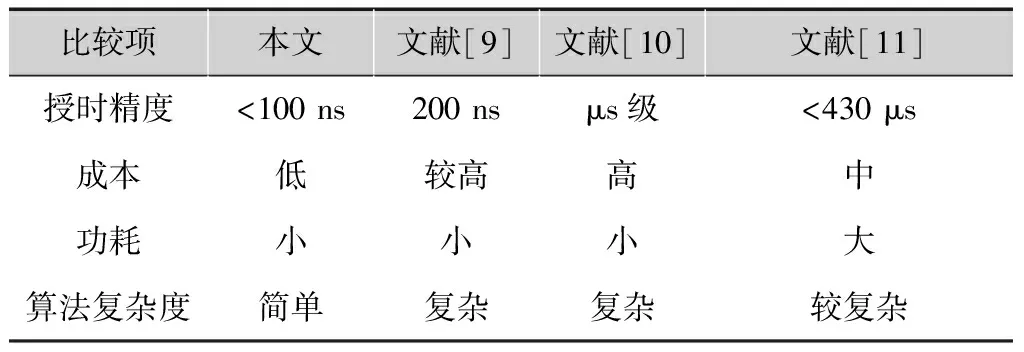

4 分析与对比

授时装置的传输时间延迟t主要来源于D触发器延迟时间、STM32中断响应时间及I/O口响应时间,其中D触发器传输延迟为2.6 ns,STM32中断响应时间最大为83.3 ns,I/O口响应时间最快为11.1 ns,因此器件固有的传输延迟时间约为97 ns。考虑到FR4板材传输线的传输速度为6 in/ns[8],而实际制作的PCB板上闸门信号Q与STM32之间的线长约为0.6 in(1 in=2.54 cm),由此可以计算出传输线引入的传输延迟为0.1 ns,因此装置固有的传输延迟时间为97.1 ns,则装置的授时精度记为t<100 ns。授时装置主要采用硬件电路来实现授时,弱化了软件算法开发难题,从而简化了授时过程;均选用市场上常用的低功耗器件,因而降低了装置的功耗和成本。本文与文献[9]、文献[10]、文献[11]中的性能比较详见表1。

表1 性能比较

比较项本文文献[9]文献[10]文献[11]授时精度<100ns200nsμs级<430μs成本低较高高中功耗小小小大算法复杂度简单复杂复杂较复杂

5 小结

本文采用超高速D触发器和STM32的高速中断响应来捕获1 pps时间基准信号的上升沿、数字相位调制器直接就临近载波相位调相的方法,将1 pps时间基准信号的上升沿与数据之间的传输延迟尽可能地限定在器件自身的极限值,提高了授时精度,从而确保了时间同步中1 pps时间基准信号上升沿的可靠性和精确性。通过研制转发1 pps时间基准信号和本地信息来实现授时的硬件平台,弱化了软件算法开发难题,从而简化了授时过程。在工程研制中,涉及的低功耗有源IC器件均为贴片型,无源器件均为0603贴片型封装,大大减小了授时装置的物理尺寸,从而降低了授时装置的功耗和成本。该装置具有授时精度高、成本低、功耗小、便携式等优点,具有一定的工程应用价值。

[1] 黄飞,明德祥,乔纯捷,等.时间统一系统中多基准源的设计[J].兵工学报,2008,29(11):1330-1331.

[2] LEE J,JEONG Y-S,NAM K-D. Time synchronization method of network testing system by standard wave[C]//Proc. the 16th International Conference on Advanced Communication Technology. [S.l.]:IEEE Press,2014:1136-1139.

[3] YAO Xinyu. Time synchronization under 1pps signal with synthetic disturbance[C]//Proc. the International Conference on Logistics Engineering and Intelligent Transportation Systems. [S.l.]:IEEE Press,2010:1-4.

[4] 李小瑞,党宏社,佟明,等.基于STM32F103C8T6的广播发射机微控制器硬件设计[J].电视技术,2008,32(11):28-30.

[5] 樊昌信,曹丽娜.通信原理[M].6版. 北京:国防工业出版社,2006.

[6] 时宏伟.二进制相移键控的异或门实现[J].电讯技术,1989,29(3):23-25.

[7] 郑魏,李智敏,骆德汉.智能家居无线网络设计与实现[J].电视技术,2013,3(21):56-59.

[8] 田广锟,范如东.高速电路PCB设计与EMC技术分析[M].北京:电子工业出版社,2011.

[9] 张涛,林雨.采用AVR控制器的GPS授时与定位装置的设计与制作[J].计算机测量与控制,2014,22(12):4127-4129.

[10] 黄敬尧,张超,何明川,等.电力系统GPS同步授时装置设计与应用[J].计算机测量与控制,2012,20(12):3355-3357.

[11] 李德骏,汪港,杨灿军,等.基于NTP和IEEE1588海底观测网时间同步系统[J].浙江大学学报,2014,48(1):1-7.

肖 龙(1988— ),硕士生,主研无线通信、电路与系统;

赵秋明(1954— ),硕士生导师,副教授,高级工程师,主要研究方向为无线通信、电路与系统;

许丰灵(1990— ),硕士生,主研嵌入式应用开发。

责任编辑:闫雯雯

Timing Device Design Based on 1 pps Signal

XIAO Long, ZHAO Qiuming, XU Fengling

(SchoolofInformationandCommunication,GuilinUniversityofElectronicTechnology,GuangxiGuilin541004,China)

In view of the time synchronization application of 1pps signal, a timing device based on 1pps signal is researched. According to detailed analysis of the devices selection, parameter setting, modulator and other key parts, a timing device based on 1pps signal is designed, mainly including baseband coding, preprocessing circuit, modulation circuit,power amplification circuit. The device is well characterized by high timing accuracy, low cost, low power and portability, meets the needs of time synchronization application.

1 pps; timing; time synchronization

TN832

A

10.16280/j.videoe.2015.19.009

2015-04-22

【本文献信息】肖龙,赵秋明,许丰灵.基于1 pps时间基准信号的授时装置设计[J].电视技术,2015,39(19).