智能微网保护装置新平台系统设计

刘 靖

(国电南瑞科技股份有限公司深圳分公司,广东 深圳 518054)

随着电网规模的不断扩大,电力系统也逐步提高了对电能质量和可靠性方面的要求。世界范围内发生了多次影响范围极大的停电事件,暴露出了超大规模电力系统内分布式电源与大电网之间的矛盾。微网的出现可以解决分布式电源并网给大电网带来的问题,平时作为分布式电源与大电网并网运行,但是当故障发生时,微网可以孤岛运行,从有问题的主网上脱离,独立为负荷供电[1]。

智能微网是通过集成的通信体系、高级的分析技术、先进的控制技术来实现的。微网保护应采用广域保护的模式,由中央单元和就地单元两部分组成。在微网主控制室安装的中央单元可以提供全站保护,而在每个开关处安装就地处理单元完成交流量和开关量的采集。

针对智能微网保护方式,大量的数据被采集到中央单元,进行汇总计算,同一时刻的数据必须保证在相同的采样周期得到处理,而不被延迟。复杂的控制原理和保护技术,要求快速响应的通信机制,都需要有强有力的硬件平台的保障。针对线路或者变压器的单一对象的传统的保护装置已不能满足广域保护的模式,新一代平台对计算、通信能力有了更高的要求,同时也提出了对应用不同的小系统方面适用性与易用性的需求。本文提出的系统设计可广泛应用于智能微网保护装置,并具有实际操作性。

1 设计原则

智能微网保护装置的新平台的设计原则如下。

1.1 广域保护方案

在广域保护方案中,主保护为智能微网保护中央单元,完成微网区域内的线路和母线保护。主保护的逻辑计算来源于就地单元上送的数据,并根据计算的结果对就地单元发送控制命令。智能终端主要完成就地开关信息、交流量的采集以及中央单元下发的控制命令的执行。智能微网的保护模块众多,定值数量大,采集的开关量输入、模拟量输入与开关量输出的数量都远大于一套普通的保护装置,因此对保护中央单元的计算处理能力、通信传输能力和数据存储能力都提出了高规格的要求[2]。

相对于由多台装置共同完成全套保护功能的方案来说,本文提出了单台8U 装置完成全套保护功能的系统设计方案。这样做可以使数据更为集中,效率更高,成本降低的同时也省去组屏和接线的繁复工作,有利于调试和维护工作。

1.2 主处理器选型

主处理器采用Freescale 公司45nm QorIQ 系列的P2020,有优异的单线程性能功耗比,适用于网络、电信、军事以及工业市场中的各种应用。该通信处理器具有两个高性能Power Architecture® e500内核,每个内核的运行频率为1.33 GHz,自带32 KB L1 缓存、512 KB L2 缓存,支持32/64 位DDR2 和DDR3,同时支持纠错码。

P2020 的外设丰富,带有4 个高达3.125GHz 的SerDes、两个PCI Express 接口、两个Serial RapidIO接口、两个SGMII 接口、两个高速USB 控制器。作为主保护最核心的部分,此款处理器提供了一个强大的硬件平台,特别适用于通信高度集成与大规模数据处理,为智能微网保护提供充足的资源保障,并且为今后的扩展预留有较大的提升空间。

1.3 数据总线设计

智能微网保护处理的GOOSE 与SV 数据总量是巨大的,但不同小系统处理的数据量是不同的,需要根据需求来配置不同数量的插件。各个插件采集的数据都通过相同的接口由数据总线上送主处理器处,这就要求该数据总线具有高速、共享、可配置的特性。无论应用于数字化变电站或是传统变电站,数据总线上的智能插件都要求配置灵活,并具有可扩展性。

数据总线由FPGA 加上MLVDS 的方式构成:FPGA 采用Xilinx 公司Spartan-6 系列的XC6SLX25T芯片,它集成了24051 个逻辑单元,936Kbits 的RAM块,以及38 个DSP48A1 单元,内置1 路PCI-E 硬核;MLVDS 芯片采用TI 公司的SN65MLVD080 芯片,可提供8 路半双工的250Mbit 的物理通道[3]。每个插件都配有FPGA 和MLVDS 芯片,FPGA 进行数据编码与解码的工作,SN65MLVD080 在总线板上组成的总线方式的物理通道,将主处理器与GOOSE、SV 插件的数据相互传输。这样的硬件平台设计使得保护的适应性增强,具有很高的冗余度。

1.4 软硬件可靠性设计

可靠性在软硬件两个方面都有考虑,确保装置的正确运行。软件方面主要是对关键电路与核心器件进行监测,包括:开入、开出返读,电源状态监视,A/D 基准判断,内存(RAM)与定制区(EEPROM)的正反码CRC 校验等。发现任何问题,都会立即闭锁出口继电器,发出告警信号,并生成事件记录上送。硬件方面从器件的选择和回路的双重化配置来保障可靠性:所有设计都采用工业级器件,并充分考虑降额应用,降低其发热和功耗,控制元器件的失效率,延长其有效生命周期。采用双电源、双采样等冗余设计,防止关键电路上的失效影响了整体运行,双CPU 互为闭锁出口回路减少了单一元器件失效而造成的误动。

2 硬件设计

2.1 总体架构

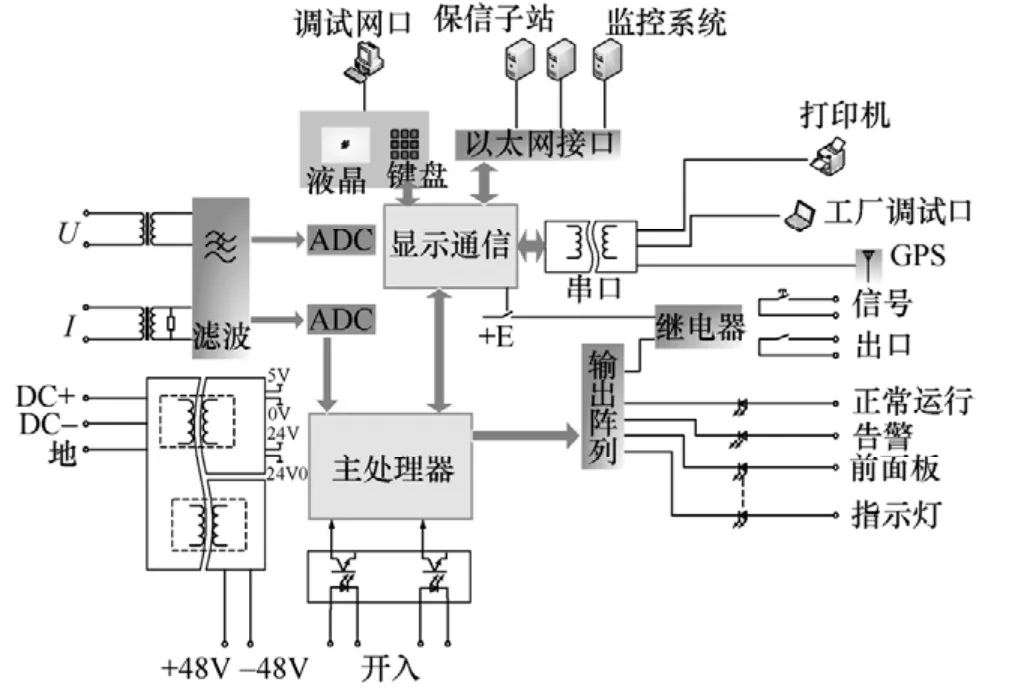

所有插件均为标准4U 高度规格,采用背插式结构通过总线板安装在机箱中。根据数字化站或者常规站的不同配置可以选择不同的机箱高度来配置更多的插件,如标准19 英寸4U 机箱或者8U 机箱。无论是4U 机箱还是8U 机箱,电源插件、主CPU插件、显示通信插件都是标准配置,智能ADC 插件、智能I/O 插件、交流插件、SV/GOOSE 插件都是根据功能需求选配。装置正面配置一块5.7 寸320×240点阵TFT 液晶,辅以按键和点灯信号用来完成良好的人机交换界面。装置的整体硬件结构如图1所示。

图1 整体硬件结构图

2.2 主CPU 插件设计

主CPU 插件主要需要完成模拟量的采样、计算,保护逻辑的判断,开入的读取、出口控制,各种记录保存等功能。在满足这些功能的前提条件是稳定可靠的系统设计,为了应对难以预测的各种突发状况,系统要具有冗余性。主处理器P2020 的双核并行处理可以满足这些需求,CPU 的两个内核独立运行,又相互监视,起到双重闭锁的功能,保证系统的可靠性。在功能划分上,core0 负责逻辑运算与记录保存,core1 负责与外部通信、传输数据与开关量接口工作,包括FPGA、千兆以太网、串行接口等。P2020 是一款高性能带有双精度浮点计算能力的处理器,特别适合保护逻辑计算;丰富的外设接口可以与多种设备高速连接,可以满足大容量数据吞吐。除了处理器自带的cache 和sram,板上还为CPU 外扩了1GB DDR2 和128MB NOR FLASH,这些大容量内存保证了有足够的数据空间和代码空间提供给智能微网保护;另外还预留有 NAND FLASH 与SPI FLASH 的扩展位置,便于保存录波数据与整定定值。在本系统中P2020 用到的高速接口有3 路千兆以太网口和1 路PCI-E 接口,其中PCI-E 接口用于与FPGA 自带的PCI-E 接口相连,最高速度2.5Gb/s,可以满足数字化站下的数据流量需求。

为了提高板间数据交换速率,同时兼顾适应性和兼容性,使用到了MLVDS 通信技术。MLVDS 总线是专门应用于背板或多点电缆的LVDS 技术的一个新系列,继承了LVDS 低压差分的信号特性,通过更改输出幅度和输出数据的压摆率,减小了电磁干扰带来的问题。2 片MLVDS 芯片多达16 路通道,其中每一路MLVDS 都可以达到125Mb/s,组成的数据总线最大支持2Gb/s 的数据流量。每路通道都可以独立控制收发方向,根据逻辑划分可定义为控制总线、数据总线、校时总线等不同功能。FPGA使用自身的时钟驱动并提供给MLVDS 芯片,在内部将数据总线与异步FIFO 相连接,数据宽度与传输速度都可以根据需求更改定义。

Xilinx® Spartan-6 LXT FPGA 中 内 置 PCI Express 端点模块,兼容PCI Express® 1.1 标准,是针对低功耗、低成本高速互连实现PCI Express 的兼容系统设计。所有收发数据在FPGA 内部整合后打包,经PCI-E 通道由DMA 直接传输给主处理器P2020,无需应用程序的控制与干涉,极大提升了运行效率与速度。

2.3 显示通信插件设计

显示通信插件主要完成人机界面、打印以及与站控层通信等功能。内部的处理器MPC8321 是一颗经济高效的网络通信处理器,包含一个e300c2 内核,它包括一个16KB 的L1 指令、数据缓存和片上内存管理单元(MMU)。增强的特性允许并行执行更有效的操作,从而显著提高了性能。显示通信插件提供了按键与液晶的接口,同样也有MLVDS 总线接口从主CPU 插件获得数据;对外提供了3 路百兆以太网口用于和监控后台、保护工程师站通信,一路RS484 的校时口,一路RS232 的打印口和一路RS232调试口。

2.4 智能插件设计

智能插件包括数字化的SV/GOOSE 插件与传统I/O、ADC 插件,各种插件的软硬件接口都保持统一,有极强的扩展性与适应性,而且支持带电拔插,方便检修工作的进行。数字化的SV/GOOSE 插件使用FPGA 作为主控芯片,对上与MLVDS 总线连接,对下生成多个百兆以太网来驱动光口或者网口与外部通信。FPGA 的同步处理能力可以保证所有报文都能立即被响应,配合IEEE1588 打下时标完成精确记录报文收发时刻,百兆以太网的数量也可以灵活配置,缓存根据需求变更大小。

智能ADC 插件采用在电力行业成熟应用的16位采集芯片AD7606,所有通道都做到同步采样,片内集成二阶滤波器、采样保持放大电路、输入钳位保护等功能。在FPGA 的控制下,采样速率可被设置为一个可变值,最高达到200Kbps 的采样率。智能I/O 插件可以采集DC220/DC110 的开入量,完成信号出口和跳闸出口的功能。开入开出量保存在FPGA 固定的数据区域内,其中开入量的每个变位都有精确到微妙的记录,随时可以上送到主控制器;开出量的数据报文需要经过奇偶校验,在硬件上受到单独的出口电源控制,双重闭锁保证了安全性。

3 软件逻辑

3.1 面向对象软件平台

为保证程序系统化以及可延续性,且为应用开发提供安全、灵活、一致的编程接口,建立了基于多任务实时操作系统Vxworks,采用面向对象设计方式的适用各种开发环境、具有长生命周期的软件平台。该平台可以大大缩短应用开发周期,支持电力行业各种标准通信规约,如IEC 103、IEC 104、IEC 61850 等。软件平台的基本元素称为元件,在面向对象思想中,是将数据以及定义在数据上的操作封装在一起的过程,同样也可以扩展为一个个智能化插件,将同类的应用程序以元件的形式进行封装,可以提高代码的可维护性和可重用性。

软件平台的组成有:各个插件上的系统程序、底层的驱动程序、智能插件上的功能程序和后台配置工具软件等。系统程序包括定值调用与存储功能模块、事件记录与录波功能模块、系统监测与自检功能模块、定时器控制功能模块等;驱动程序包括操作系统接口功能模块、插件识别与注册功能模块、各种硬件控制功能模块等;智能插件功能程序包括开入开出逻辑控制、参数管理功能模块、报文收发与拼接功能模块等;后台配置工具包括文件、程序的上传下载功能模块、定值参数的调取与修改功能模块、记录和波形的查看和分析功能模块等。

3.2 MLVDS 总线逻辑设计

装置上电时主处理器读取配置文件,得到智能插件数量与类型,其中插件数量根据工程不同可灵活增减,用配置工具进行注册。受到总线板插槽数量限制,插件数量最大为16 块,一致的软硬件接口可根据工程需求配置不同的插件。MLVDS 总线结构如图2所示。

图2 MLVDS 总线结构图

MLVDS 总线分为控制总线与数据总线。控制总线用于调配轮询插件,由主处理器插件上的FPGA产生定时中断,根据不同插件的数据量分配不同的 时间,再召唤该插件数据。插件在轮到自己发送时才可以发送,如果有内容则发送信息,如果无内容则发送空帧;在其他插件发送时处于监听状态,如果发现是发给自己的开启接收逻辑,否则不予理会。总线控制逻辑可以保证所有插件受到主机调配,相互间不会产生竞争或冲突的情况。

4 结论

基于集中式保护方式研发的智能微网保护装置目前已通过了型式试验和动模试验的检测,检测结构表明了该装置的保护功能以及各项软硬件指标均满足或高于电力行业标准,具有抗干扰能力强、测量精度高、反应速度快速、应用场合广泛等特点。

本文提出的智能微网保护装置的新平台技术方案,可广泛应用于不同的小系统,具有实际操作性。该平台软硬件资源丰富,保护功能强大,配置可随需求裁剪,可靠性极高,可以满足微网保护装置的各种功能需求,具有良好的应用前景。

[1] 刘龙舞,张捍东,董克龙.微网控制技术研究综述[J].电工电气,2012(2): 1-6.

[2] 张宗包,袁荣湘,赵树华,等.微电网继电保护方法探讨[J].电力系统保护与控制,2010,38(18): 204-209.

[3] 孟令军,张国兵,王宏涛,等.基于FPGA 的LVDS高速差分接口应用[J].化工自动化及仪表,2010,37(5): 94-96.