中国调频频段数字音频广播标准的LDPC编码器设计

陈冬英, 郭里婷, 苏凯雄, 吴林煌

(福州大学物理与信息工程学院, 福建 福州 350116)

中国调频频段数字音频广播标准的LDPC编码器设计

陈冬英, 郭里婷, 苏凯雄, 吴林煌

(福州大学物理与信息工程学院, 福建 福州 350116)

根据2013年颁布的中国数字音频广播(CDR)中LDPC码的校验矩阵结构特点, 提出一种基于生成矩阵的编码方法. 该方法将生成矩阵转化为块准循环结构, 并行化处理编码算法的行与列操作; 采用存储器调用的控制策略, 实现CDR标准中四种码率编码, 提高了硬件资源的利用率. 在Xilinx 公司的FPGA平台上进行该编码器的设计, 联合ModelSim和Matlab软件进行验证. 结果表明, 该设计方法具有资源占用较少、 功耗低、 编码准确率高等特点, 其吞吐量约为400 Mbit, 达到了CDR标准的LDPC编码要求.

中国调频频段数字音频广播; 低密度奇偶校验码; 编码器; FPGA平台

0 引言

针对早期基于DAB的标准中存在1.536 MHz信道带宽限于FM/AM的兼容性问题[1-2], 我国于2013年8月颁布了中国调频频段数字音频广播标准(FM-CDR, frequency modulation-China digital radio), 以下简称CDR[3-4]. 鉴于LDPC码具备极佳的纠错性能, CDR标准也采用了LDPC码作为信道编码方案. 该标准支持4种码率的LDPC码, 其码长均为9 216. 由于校验矩阵的非零元素分布随机, 导致编码器设计存在存储资源需求大、 功耗大、 效率低等问题, 这给基于CDR标准的LDPC编码器的设计带来极大挑战.

文[5-6]报道了LDPC编码的方法, 给出一般LDPC码的构造, 但其码长较短. 文[7]对块准循环LDPC码译码器进行FPGA实现, 达到高吞吐量. 文[8]采用存储器调用的控制策略, 对LDPC码进行解码器实现, 达到多种码率复用. 本研究对CDR标准中LDPC码的校验矩阵结构进行分析, 利用编码器与解码器的关系, 将利用生成矩阵的编码方法转化为块准循环结构, 采用并行化处理的行与列操作, 提高了数据吞吐率. 同时, 采用一种合适的存储器调用的控制策略来实现CDR标准中4种码率的复用, 有效提高资源利用率. 在Xilinx 公司的FPGA平台上设计, 通过ModelSim仿真软件进行验证. 结果表明, 该设计方法编码器资源占用较少, 吞吐量可达400 Mbit, 达到了CDR标准的LDPC编码要求. 本设计方法对于CDR编码器的进一步研究具有重要的参考价值.

1 CDR标准的LDPC编码算法

1.1 CDR中LDPC码的特征

CDR标准定义的LDPC码, 具有4种码率, 分别为3/4、 1/2、 1/3、 1/4, 各码率码字长度均为9 216 bit, 信息比特长度分别为6 912, 4 608, 3 072, 2 304 bit.

由分析知, 4种码率的LDPC校验矩阵有类似规律. 通过块高斯消元法[9]得到生成矩阵, 通过行列置换进行块循环矩阵划分, 所得矩阵是系统矩阵, 具体的结构如下所示:

Gqe=[IG]

其中:

结构中Gi, j为子矩阵, 每个子矩阵均为256×256的循环矩阵, 并且每行循环右移一位即可得到其下一行, 每列循环下移一位即可得到其下一列, 第一行由最后一行进行循环右移得到, 第一列由最后一列循环下移得到. 因此, 要获得一个Gi, j只需其中一行的数据元素gi, j即可, 此行数据为Gi, j生成多项式, 则k×c个生成多项式即可构成Gqc.

根据CDR标准的LDPC配置, 若码率为3/4,k=6 912÷256=27,c=(9 216-6 912)÷256=9, 以此类推, 各码率相对应的k与c的值如表1所示.

表1 CDR编码配置的参数k与c

1.2 LDPC编码算法

CDR标准中采用LDPC码生成矩阵可进行块准循环矩阵划分. 文[10]采用并行译码可实现(8 176, 7 154) LDPC译码, 获得高吞吐量. 本研究利用类似的并行处理, 实现了CDR标准中4种码率的LDPC编码.

设待编码的输入信息序列为:m=m0,m1, …,mi, …,mk-1, 其中mi=mi, 0,mi, 1, …,mi, b-1, 0≤i≤k-1. 信息序列被分为k组, 每组为b比特信息. 参考文[11], 设计中S为编码后的码字, 由下式所得:

其中:pj为校验位:

同时

由此, 当串行输入信息序列(m0,m1, …,mk-1), 根据已构造出的生成矩阵, 由式(3)得pj. 其中, 输入mi相应的值miGi, j, 可通过反馈移位寄存器来实现. 当所有的信息序列输入完毕, 所有的检验位向量pj由式(3)求得, 便可以得到编码后的序列s. 设计中,c个校验向量pj采用并行设计, 当信息序列全部输入编码器后即可完成所有校验向量的计算. 因此, 存储的生成多项式只需k×c个, 而不用将所有生成多项式进行存储, 所需存储gi, j只占原来总量的1/256, 有效地节省了存储资源.

2 CDR标准的LDPC编码器设计

2.1 LDPC编码总体设计

CDR标准中对业务数据采用的是LDPC编码, 根据块高斯消元法获得生成矩阵, 所得生成矩阵可进行块循环矩阵划分为256×256个子矩阵, 且各子矩阵具有循环特性, 提高其编码效率.

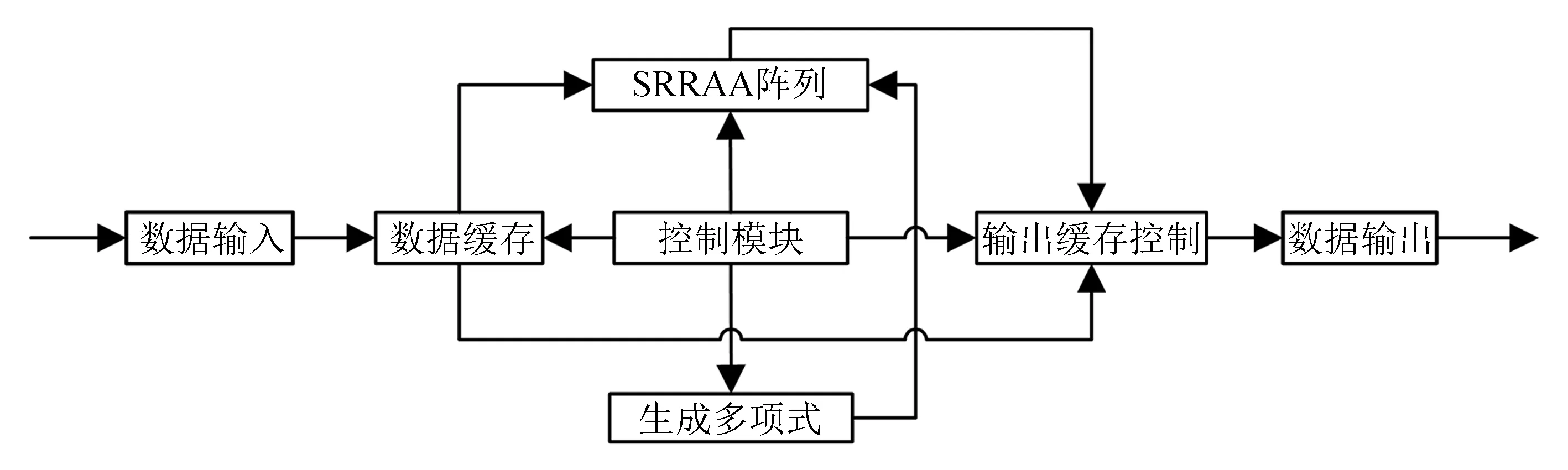

在实现时, 由于RAM要进行同时读写, 采用双口RAM. 每块RAM实现不同码率的地址初始化以及RAM的读、 写等操作由一个控制器控制. 根据CDR标准的LDPC编码原理, 设计中LDPC编码模块总体架构如图1所示.

图1 基于CDR的LDPC总体设计框图

2.2 输入存储单元

因LDPC码率的不同, 其校验矩阵具有差异性. 根据文[8], 将分解好的生成矩阵存储在ROM中, 编码器存储采用存储器调用的控制策略, 通过寻址加载不同编码码率下的生成矩阵. 4种编码码率存储的矩阵数为2 304、 3 072、 4 608、 6 912, 根据CDR中的生成矩阵特性将其分成256bit大小的段, 分别存储在9~27个256bit存储宽度的ROM中. 设计采用并行结构, 根据不同LDPC码率加载相对应的生成矩阵, 并在SRAA模块中生成校验信息. 由于矩阵按照这种方法分解后的子矩阵是循环矩阵, 因此只需要存储矩阵的首行信息即可.SRAA模块就可以通过对首行信息比特进行循环移位, 进而得到整个生成矩阵. 存储方法如图2所示.

图3 SRAA电路框图

2.3 SRAA模块阵列

SRAA(移位寄存累加器)模块是编码器的核心, 其占用资源是最多的.CDR标准有4种LDPC编码码率: 3/4、 1/2、 1/3、 1/4. 当码率为1/4时, 生成的校验码最多为6 912, 此时存储的生成矩阵也是最大的. 所设计的SRAA为并行的256bit输出, 其最大校验码6 912bit, 输出需要27个SRAA并行工作, 因此, 总共使用了27个串行输入、 并行输出256bit的SRAA并行进行校验即可. 具体的SRAA电路如图3所示.

具体的设计流程:

1) 初始化, 将A寄存器和B寄存器清零;

5) 开始输入信息矢量m1, B寄存器加载第二个子矩阵G1, 0的生成多项式g1, 0, 重复步骤2~4, 经过256个时钟周期,m1输入完毕, A寄存器的数值更新为:A=m0G0, 0+m1G0, 1;

6) 重复步骤5, 所有信息矢量输入完毕, A寄存器的数值更新为A=m0G0, 0+m1G0, 1+…+mk-1Gk-1, 0=p0.

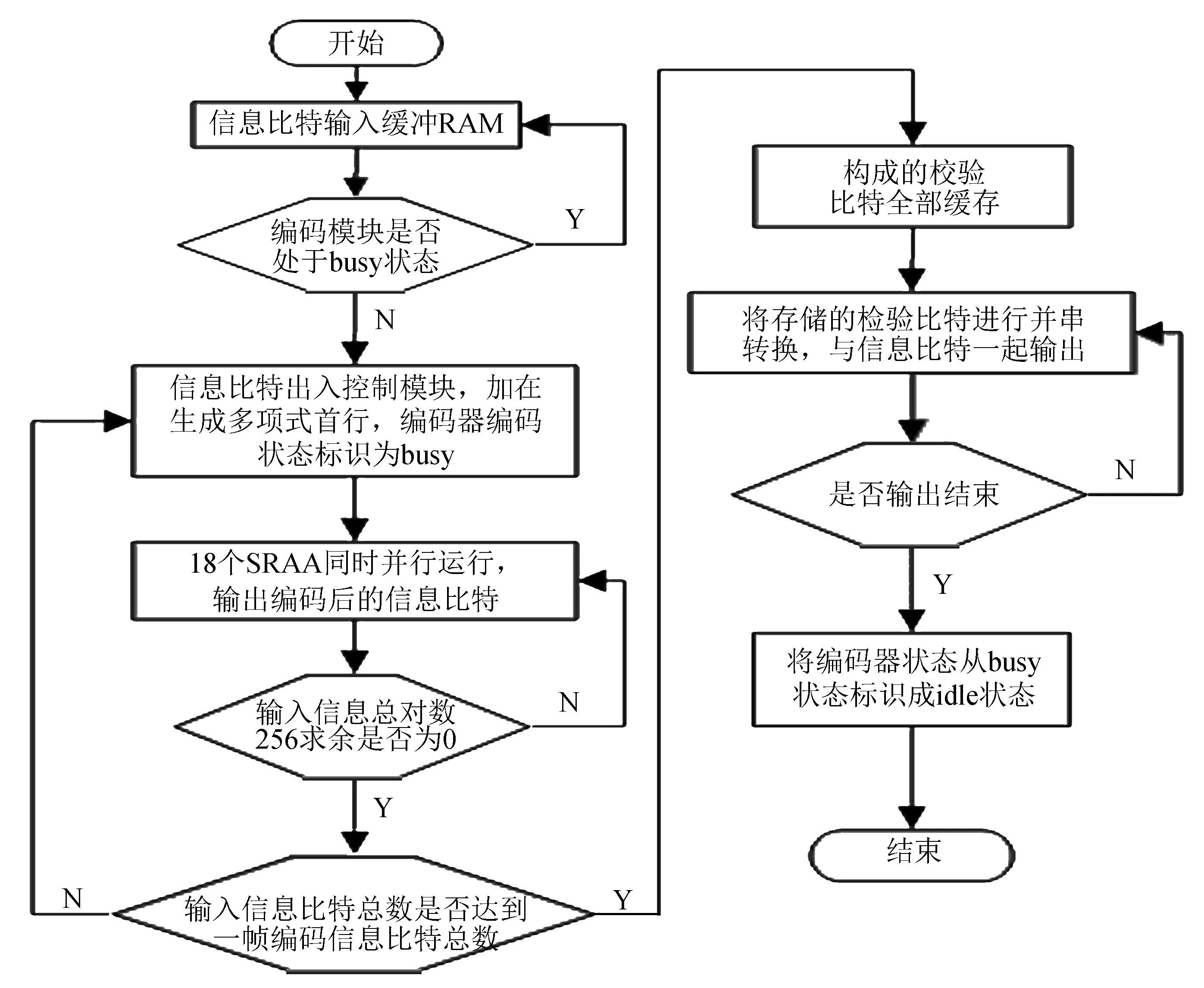

图4给出了1/2码率H(4 608, 9 216)的LDPC编码器的编码流程图. 首先将信息比特输入到RAM缓冲, 判断编码模块是否处于busy状态. 当编码模块空闲时, 信息比特输入控制模块, 同时控制模块加载生成多项式, 且编码器进入busy状态. 18个SRAA电路并行工作, 当完成一帧信息比特输入时, 对生成的校验比特全部存储, 进行并串转换后, 以信息比特在前, 校验比特在后的格式进行输出, 输出完毕后编码器状态从busy状态进入idle状态, 完成一帧数据的编码.

图4 1/2码率LDPC编码流程图

3 FPGA实现与仿真

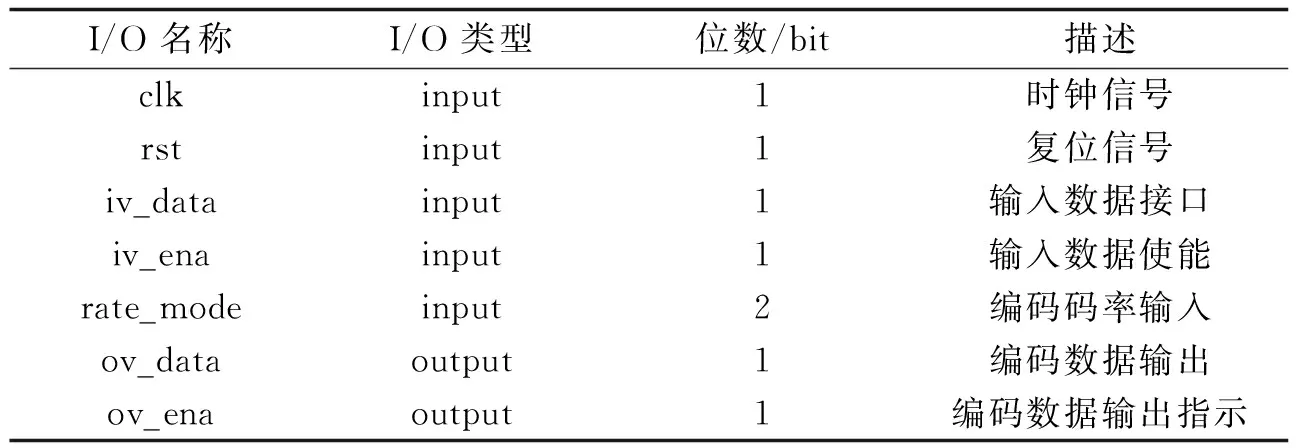

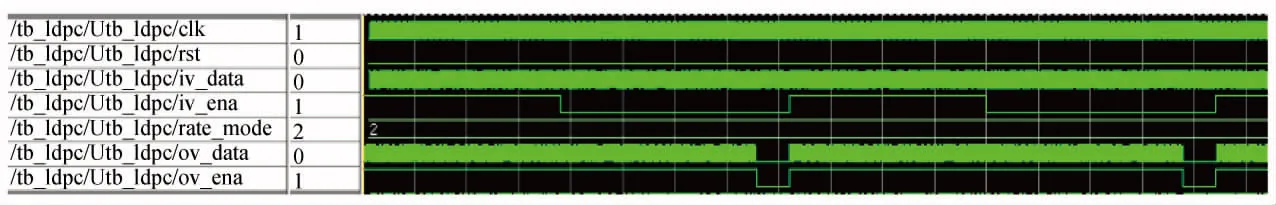

采用RTL级的Verilog HDL语言编写整个设计. 利用Xilinx公司的xc6slx150t-3fgg484 FPGA芯片在资源符合本设计要求下, 满足价格低、 集成度高、 保持灵活和功耗低的优点, 选用此芯片对CDR标准中4种码率的LDPC编码器进行编译综合. 以1/2码率的LDPC编码器为例, 表2为编码器顶层模块LdpcEncode的I/O端口说明, 包括端口名称、 端口类型、 该端口的位宽及端口性质的描述. 图5为H(4 608, 9 612)LDPC码在ModelSim平台下的时序仿真波形.

表2 Ldpc Encode模块的端口说明

图5 LDPC编码器的时序仿真波形图

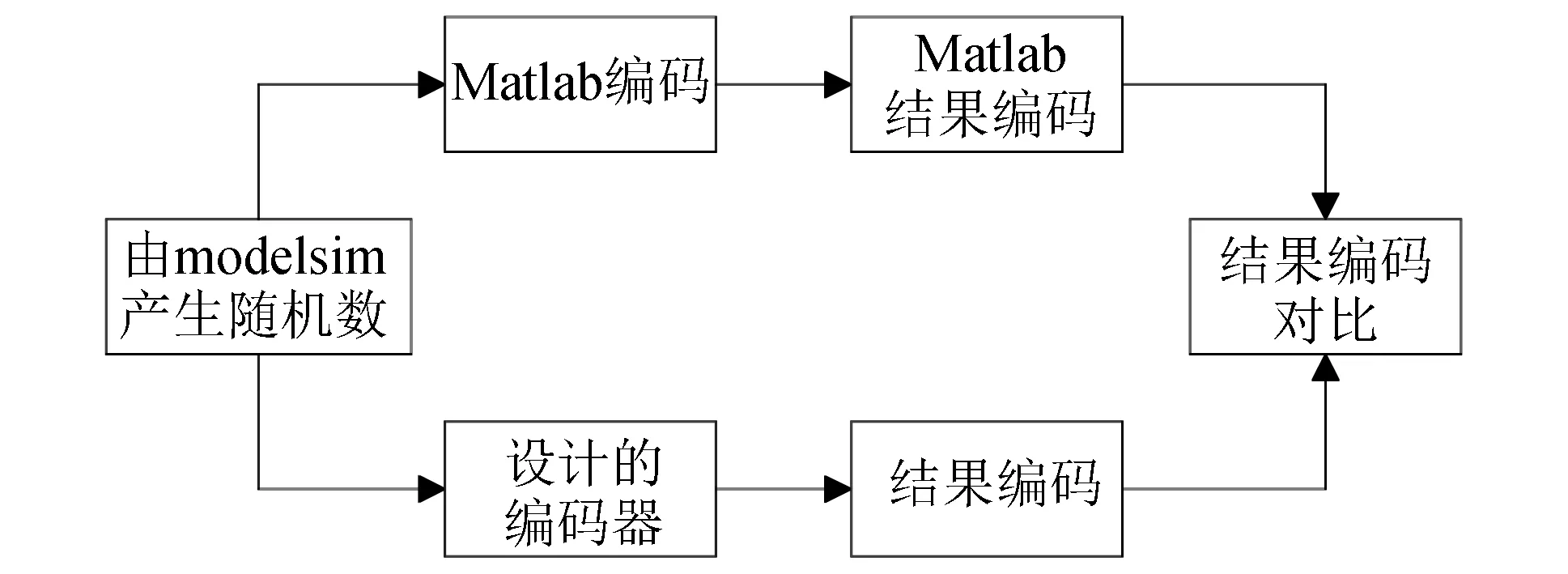

图6 本文设计的LDPC编码器准确性验证

图5中, 编码器顺次从ROM中读取生成向量, 送入SRAA电路进行校验位运算. 当18个生成向量进入电路完成运算后, 结束一帧信息的编码, 开始输出校验信息. SRAA电路完成一个生成向量的运算需要256个时钟, 则校验位的计算完成时间为256×18=4 608个时钟. 若以最高工作频率200 MHz为系统时钟、 码长为9 216 bit进行计算, 编码吞吐量约为400 Mbit, 满足CDR标准的要求, 且吞吐量较高.

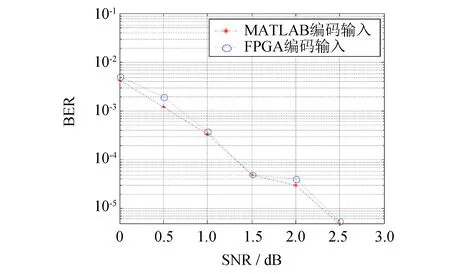

图7 MATLAB编码与本文设计编码器经过BP迭代译码的误码率

根据CDR对LDPC编码器的描述, 联合ModelSim和Matlab软件, 搭建了一个LDPC编码器验证平台. 具体如图6所示.

本设计首先基于Matlab平台对其进行了实现, 并根据C×HT(C为编码器生成的码字)对编码结果进行验证, 说明Matlab设计的编码器能对信息序列进行准确编码. 其次, 在ModelSim平台上产生随机数作为待编码的信息序列, 分别送入Matlab设计的编码器模块和本文设计的编码器模块, 并对比两个输出结果. 仿真结果, 两输出编码差值为0. 因此, 所设计的LDPC编码器能对信息序列进行准确编码. 图7是分别以Matlab编码结果与所设计的编码器编码结果作为Matlab平台的BP迭代译码[12]的输入, 并经过高斯信道, 所得的信噪比与误码率的关系曲线. 由图7可知, Matlab编码输入进行译码后所得的误码率曲线与FPGA编码器编码结果输入译码后的误码率曲线, 两者具有一致性, 且在信噪比为2.5 dB时, 误码率均达10-5以下, 证明所设计的编码器编码具有高准确率.

在具体方案设计结果中, 因本标准为最新颁布的, 还未找到同一标准的编码设计文献进行比较, 因此以文[9]中介绍的编码器的资源使用情况进行对比, 见表3. 文[9]编码器吞吐率约为228 Mbit·s-1. 所设计的编码器所占逻辑资源slice为 17%, 片上RAM资源为13%, 并且未使用DSP.本设计的标准与文[9]中的标准基本相似, 但本标准H矩阵较大, 实现难度更大. 本设计编码器在保证与文[9]设计的编码器占用资源相近时, 其可获得更大的吞吐率. 因此, 该设计在硬件实现上完全可行, 且资源利用率较高.

表3 本设计与文[9]资源使用情况对比

4 结语

分析了最新颁布的CDR标准中LDPC编码过程, 提出一种基于生成矩阵的编码算法. 利用生成矩阵块准循环结构, 通过行列置换实现, 并行化处理编码算法的行与列操作, 采用存储器调用的控制策略, 实现CDR标准中四种码率编码[13-14]. 最后, 对所提出的方法在Xilinx公司的FPGA平台上用Verilog HDL语言编写设计, 以H(4 608, 9 216)的LDPC编码器为例, 它的信息数据吞吐率达400 Mbit·s-1. 联合Matlab和ModelSim平台对编码过程进行验证, 其结果具有一致性, 并对比Matlab编码器与FPGA编码器译码输出的误码率曲线, 得信噪比在2.5 dB时, 误码率可达10-5以下, 说明所设计的LDPC编码器具有较高吞吐量, 且编码准确率高. 因本标准最新颁布, 还未找到同一标准的编码设计文献进行比较说明, 本设计为后续的CDR研究具有重要的参考价值.

[1] Ji Long, Li Nadi, Peng Gao,etal. A digital audio broadcasting system using short length QC-LDPC[C]//IEEE 14th International Conference on Communication Technology (ICCT). Chengdu:[s.n.], 2012: 1 057-1 061.

[2] 盛国芳, 王涛. 调频频段数字音频广播系统的实验性能测试[J]. 广播电视信息, 2014, 40(16): 44-48.

[3] ETSI ES 201 980 V3.1.1 Digital radio mondiale system specification[S]. 2001.

[4] GY/T 268.1-2013 调频频段数字音频广播第1部分: 数字音频广播信道帧结构、 信道编码和调制[S]. 2013.

[5] 高鹏, 盛国芳. 调频频段数字音频广播系统研究[J]. 广播电视信息, 2014, 40(11): 27-30.

[6] Zhao Shancheng, Ma Xiao, Zhang Xiaoyi,etal. A class of nonbinary LDPC codes with fast encoding and decoding algorithms[J]. IEEE Transactions on Communications, 2013, 61(1): 1-6.

[7] 张仲明, 许拔, 杨军, 等. 800 Mbps准循环LDPC码译码器的FPGA实现[J]. 信号处理, 2010, 26(2): 255-261.

[8] 康亮, 杨波, 沈萌. 符合CMMB标准的LDPC解码器设计[J]. 电视技术, 2009, 33(5): 40-42.

[9] 谢勇, 姚远程, 秦明伟. QC-LDPC码编码器的FPGA实现[J]. 西南科技大学学报, 2013, 28(1): 84-87.

[10] Richardson T J, Urbanke R L. Efficient encoding of low-density parity-check codes[J]. IEEE Transactions On Information Theory, 2001, 47(2): 638-656.

[11] 姜小波, 聂正华. 用于CMMB的低运算复杂度LDPC解码运算[J]. 电子学报, 2010, 7(7): 1 612-1 616.

[12] 韩国军, 刘星成. LDPC码的信道自适应迭代译码算法[J]. 电路与系统学报, 2010, 15(1): 102-107.

[13] Ouyang Xiang, Ruan Changcheng, Zheng Lingxiang. Implementation of LDPC encoding to DTMB standard based on FPGA[C]//2011 10th IEEE/ACIS International Conference on Computer and Information Science. [s.l.]: [s.n.], 2011: 235-238.

[14] Chen Xianheng, Kang Jingyu, Lin Shu. Memory system optimization for FPGA based implementation of quasi-cyclic LDPC codes decoders[J]. IEEE Transactions on Circuits and Systems, 2011(1): 98-111.

(责任编辑: 沈芸)

Design of LDPC encoder based on frequency modulation-China digital radio

CHEN Dongying, GUO Liting, SU Kaixiong, WU Linhuang

(College of Physics and Information Engineering, Fuzhou University, Fuzhou, Fujian 350116, China)

According to the structure of LDPC code in frequency modulation-China digital radio(CDR), which was promulgated in 2013, a new architecture of generator matrix LDPC coder is proposed. The LDPC code parity matrix structure is exploited to parallelize the row and column encoding operations. An appropriate method is used to control memories, which can reuse memories for different code rates, and improve the utilization of hardware resources. We have implemented the LDPC encoder on Xilinx FPGA. Combining the ModelSim with Matlab simulation results show that the design method has fewer resources consumption, low power, high accuracy rate encoding, and achieves encoding throughput of 400 Mbit.It meets with the requirements of CDR.

frequency modulation-China digital radio; low-density parity-check; encoder; field-programmable gate array platform

2014-10-10

郭里婷(1976-), 副教授, 主要从事信息与通信系统研究, guoliting@fzu.edu.cn

福建省高校产学合作重大项目(2012H61010016); 福建省自然科学基金资助项目(2013J01234)

10.7631/issn.1000-2243.2015.06.0772

1000-2243(2015)06-0772-06

TN911.22

A