宽带PCSF雷达信号频率合成器的设计与实现

翟腾普,任丽香,刘泉华,王昊飞

(北京理工大学 信息与电子学院, 北京 100081)

·收/发技术·

宽带PCSF雷达信号频率合成器的设计与实现

翟腾普,任丽香,刘泉华,王昊飞

(北京理工大学 信息与电子学院, 北京 100081)

基于脉内相位编码脉间频率步进(PCSF)雷达信号的特点,提出了利用复杂可编程逻辑器件、直接数字频率合成器(DDS)和锁相环倍频器产生任意PCSF雷达信号的方法,并实际构造了一个宽带、低噪声的S波段PCSF信号源。利用该方法可以实现对输出信号相位的精确控制,通过选择DDS输出信号的频率范围可以减少带内的杂散分量。测试结果表明:该频率源在320 MHz带宽内的无杂散动态范围为62 dBc,相位噪声为-110 dBc/Hz@1 kHz。

脉内相位编码脉间频率步进;直接数字频率合成;锁相环

0 引 言

频率步进雷达采用频率步进信号实现大的合成带宽和高距离分辨率,具有系统复杂度低且容易实现的优点。但是,由于单个脉冲瞬时带宽小、合成信号时间长,当实验对象为高速运动目标时,其对雷达信号处理具有较高要求。

相位编码信号具有较大的时宽带宽积,克服了脉冲雷达在提高发现能力和测量精度及分辨率方面的矛盾[1]。采用相位编码信号作为频率步进信号的子脉冲,构成的脉内相位编码脉间频率步进(PCSF)雷达信号[2],实现了脉内相位和脉间频率的两次调制。因此,可以在较短时间内实现大的合成带宽,拓展了频率步进雷达的应用。

本文在分析PCSF信号特点的基础上,介绍了基于复杂可编程逻辑器件(CPLD)、直接数字频率合成(DDS)和锁相环(PLL)的PCSF频率合成器的设计方法,并且基于该方法构建了一个宽带、低噪声S波段信号源,并给出了其性能测试结果。

1 PCSF信号形式和解析表达式

脉冲频率步进信号(Stepped Frequency,SF)是一种大时宽带宽积信号[3],其距离分辨率ΔR取决于系统有效工作带宽N·Δf,其中,N为频率步进脉冲串的个数,Δf为频率步进量。由于N太大会降低目标数据率,因此,在给定距离分辨率的条件下,频率步进量应该较大以减小N。同时,SF信号参数要求满足紧约束条件Δf·τ≤1[4],为获得较大的发射信号平均功率,需增大脉冲宽度τ,减小Δf。因此,在SF信号中目标数据率与发射信号平均功率是一对矛盾。

而在PCSF信号中,紧约束条件为Δfτc≤1[5],使得频率步进量Δf受相位编码子脉冲宽度τc约束。因此,在满足较大Δf的同时,通过增加相位编码长度,可以保证较大τ,以满足较大的平均发射功率,从而解决距离分辨率、目标数据率和平均发射功率之间的矛盾。

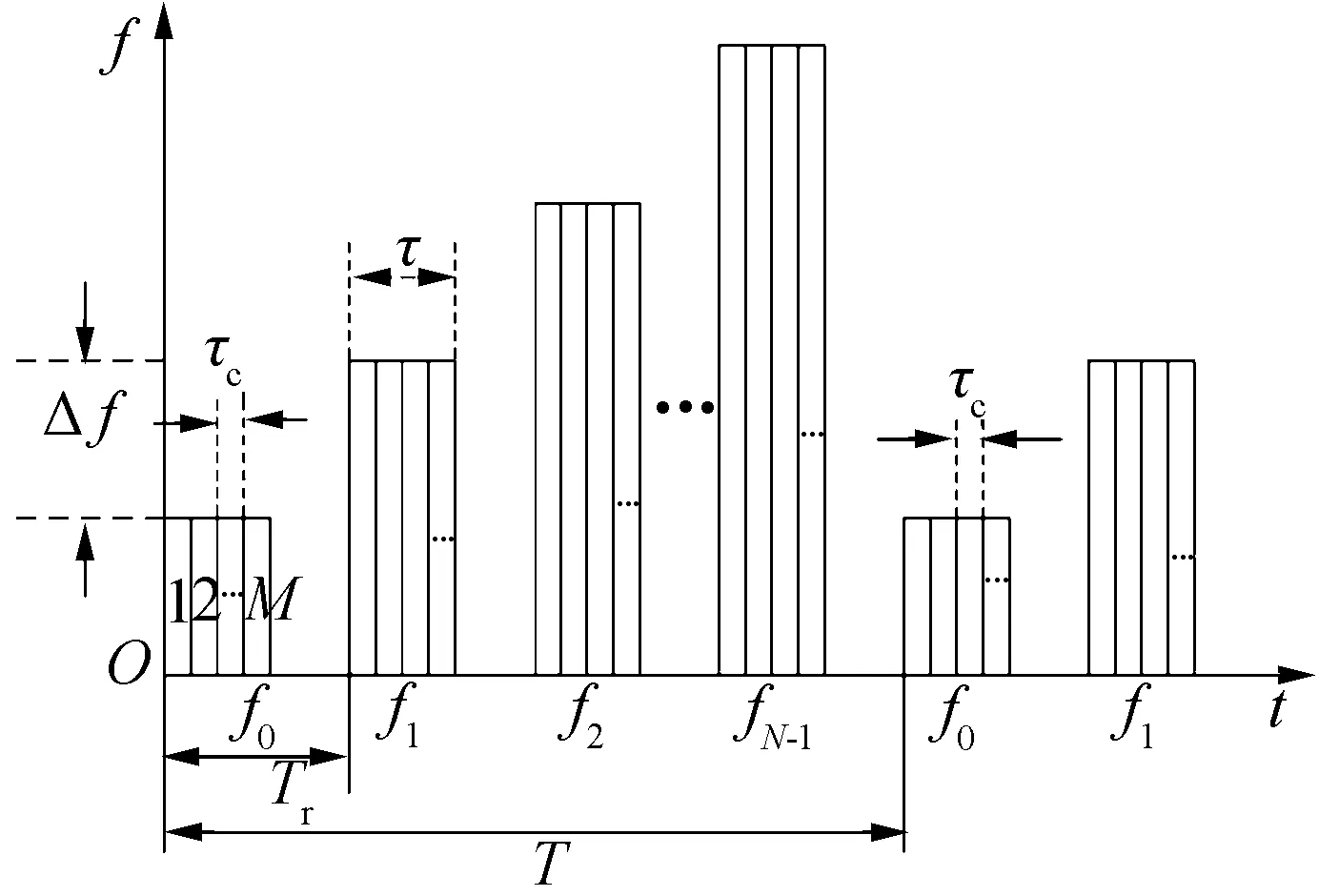

PCSF信号波形如图1所示,其中Tr为脉组重复周期,T为信号重复周期,N为频率步进数,τc为相位编码周期,M为相位编码长度。

图1 PCSF信号波形示意图

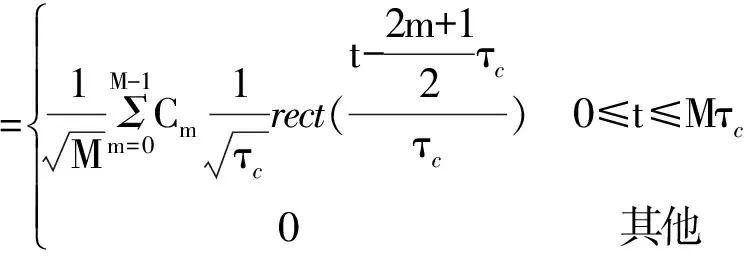

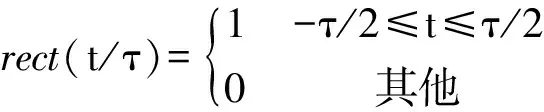

相位编码子脉冲信号的复包络为

(1)

其中

PCSF信号的解析表达式为

u(t-iTr)e-j2π(f0+iΔf)t

(2)

常用的二相编码序列有巴克码、M码等,脉内相位编码序列的类型和码长可以根据系统需要进行选择。以15位M码作为相位编码序列,Cm=1,-1,-1,-1,1,1,1,1,-1,1,-1,1,1,-1,-1,其中,{Cm=ejbm=+1,-1}为二进制序列,则bm=0,π,π,π,0,0,0,0,π,0,π,0,0,π,π,bm反映了信号的相位变化。

2 PCSF频率源方案设计

PCSF信号由中频脉冲相位编码信号和S波段频率步进信号通过混频实现。为得到高性能的PCSF雷达信号,脉冲相位编码信号应保证在脉冲间具有稳定的波形及固定相位,而频率步进信号应具有低杂散和低相位噪声的特性。

2.1 相位编码信号设计

由于在脉冲宽度τ内,载频信号的相位每隔τc就要进行一次相位编码。因此,精确的载频决定了相位编码信号的相位是否只有0或π两种状态,从而也影响到数据处理中对接收信号的匹配滤波处理结果,进而影响到整个系统的性能。

1) 调制模式

本文利用DDS可编程模式改变输出信号频率的内核方程,从而产生精确的载频信号。

在可编程调制模式中,频率方程可以表示为

f0=fs×(FTW+A/B)/232

(3)

式中:FTW、A和B分别对应DDS相应的功能寄存器,f0/fs<1/2,0≤FTW<231,2≤B≤232-1,且A DDS信号的相位通过16位的相位偏移字POW来控制。相对相位偏移Δθ可由下式计算 (4) DDS信号的相对幅度范围可由12位幅度比例因子ASF进行数字化控制。幅度范围的计算公式为 (5) 使用并行数据端口模式控制输出信号的幅度和相位,相应的参数控制字直接由32位并行数据端口提供,而功能引脚F0~F3确定了32位数据表示的参数类型。 2) 数模转换(DAC)采样时钟 外部晶振输出的100MHz高性能时钟信号作为DDS内部PLL的参考时钟,经内部PLL倍频后产生DAC的系统时钟。外部100MHz时钟信号的无杂散动态范围大于70dBc,相位噪声为-146dBc/Hz@1kHz。通过设置DDS内部PLL的倍频数,将参考信号24倍频后得到2.4GHz的DAC采样时钟。 2.2S波段频率步进信号设计 常规的频率合成技术有4种:直接频率合成、PLL频率合成、DDS以及DDS+PLL。 直接频率合成技术即直接将参考信号通过混频器、倍频器和分频器,从而实现宽带频率合成。这种频率合成器原理简单、频率分辨率高、转换速度快,但其结构复杂、体积庞大,适用范围有限[6]。PLL技术虽然具有输出信号频率高、带宽大等优点,但其输出信号的频率线性度差、相位误差大且信号锁定时间长,从而限制了其在宽带捷变频率源中的应用。DDS技术尽管具有频率分辨率高、频率转换速度快、输出相位连续等优点,但其输出信号带宽有限,杂散分量较多,并且无法直接输出高频宽带信号。而DDS+PLL的方法能够充分利用DDS频率转换速度快、频率分辨率高、线性度好的特点,同时可以发挥PLL杂散抑制好、带宽输出大的优势[7]。 本系统采用DDS驱动PLL的方法产生S波段频率步进信号,但是DDS输出信号的杂散分量较多。因此,通过选择DDS输出信号频率范围的方法,减小输出杂散分量。DDS输出信号的杂散分量主要分布在f=Afs±Bfo[8-9],其中,fs为DAC系统时钟,fo为DDS输出信号,A、B为整数。为保证频率步进信号的低杂散特性,首先,对DDS输出频段进行波段划分,尽量避开处于带内的低次杂散分量;然后,利用PLL对输出信号进行倍频;最终,得到高质量S波段频率步进信号。 软件仿真DAC采样信号频率为2.4GHz,输出信号带宽为16MHz,并且考虑DAC采样频率的2次谐波、输出频率的8次谐波,则输出信号中无杂散混叠的可用频段分布如图2所示。 图2 可用频段分布图 根据仿真结果选取可用频段内的171.136MHz~185.682MHz作为DDS的输出信号范围,设置PLL倍频数为22,以此产生中心频率为3.925GHz、带宽为320MHz的S波段频率步进信号,频率源结构如图3所示。 图3 DDS驱动PLL结构 锁相环的环路带宽越大,其输出信号锁定时间越短,但杂散分量越多;而锁相环的环路带宽越小,其锁定时间越长,但杂散分量越少。考虑系统对跳频时间的需求,锁相环的环路带宽设定为10MHz。为增强环路滤波器对带外相位噪声和杂散的抑制作用,环路滤波器选取有源三阶二类增强型,R1、C4组成的低通滤波器可滤除相位检波器输出的高频噪声,R3、C2组成的低通滤波器可滤除运算放大器输出的高频噪声,在保证锁相环锁定时间的基础上,尽可能减少杂散分量的影响。 2.3 基于DDS和PLL的PCSF频率源设计 由于DDS是可编程芯片,其输出信号的频率和相位可通过软件进行控制。因此,利用DDS可以产生任意编码类型、任意编码长度的中频信号,与PLL倍频后的频率步进信号混频便可得到任意编码类型的PCSF雷达信号。 以15位M码为相位编码序列的S波段PCSF雷达信号频率合成器为例,介绍频率合成器的实现方法,见图4。 图4 PCSF频率源结构图 1通道DDS芯片工作在可编程模式下,产生载频为125MHz的相位编码信号。其中,相位编码序列采用上述15位M码,相位编码子脉冲宽度为0.1μs,信号脉宽为1.5μs,重复周期为15μs。 2通道采用DDS驱动PLL的方法,产生脉组重复周期为15μs、频率步进量为10MHz、频率步进数为32、中心频率为3.925GHz、带宽为320MHz的S波段频率步进信号。 经过两次混频后,最终得到中心频率为3.3GHz、带宽为320MHz的S波段PCSF雷达信号。 利用DDS可编程模式可以对相位编码信号的相位进行精确控制。通过选择DDS输出信号的频率范围,再利用DDS驱动PLL的方法可以得到高性能、低杂散的频率步进信号,进而保证PCSF频率源具有相位稳定、输出频率高、输出带宽大的特点。 通过分析PCSF频率源系统中125MHz中频相位编码信号的相位稳定性以及PLL输出的S波段频率步进信号的杂散分量和无杂散动态范围,验证该频率源系统的性能,如图5、图6所示。 图5 相位编码信号 图6 相位编码信号局部放大图 1通道产生载频为125MHz的相位编码信号,编码序列采用15位M码。由图5可知,信号相位编码为0,π,π,π,0,0,0,0,π,0,π,0,0,π,π。相位编码子脉冲宽度为0.1μs,载频为125MHz。因此,0.1μs内有12.5个载频时钟周期,并且载频信号波形稳定,相位为固定的0或π。 通过测量S波段频率步进信号3.765GHz~4.085GHz内的32个频点可知,在320MHz带宽内,信号无杂散动态范围大约为62dBc,相位噪声为-110dBc/Hz@1kHz左右,如图7所示。 图7 中心频率测量结果 图8为DDS输出的频率步进信号,其中心频率为3 925MHz/22,频率步进量为10MHz/22,频率步进数为32。图9为DDS输出信号经过22倍锁相环倍频器后形成的中心频率为3 925MHz、带宽为320MHz的频率步进信号。 图8 频率步进信号频谱(倍频前) 图9 频率步进信号频谱(倍频后) 本文在介绍PCSF雷达信号特点的基础上,介绍了利用DDS、CPLD和PLL频率乘法器设计PCSF信号的方法。利用该方法可以实现对输出信号相位的精确控制,并且可减小输出信号的杂散分量。通过对实际构造的S波段PCSF信号源进行测试,验证了设计方法的可行性,为实现高性能PCSF雷达信号提供了设计参考。 [1] 陆锦辉, 是湘全, 丁庆海,等. 随机二相码脉冲压缩雷达信号分析[J]. 电子学报, 1996, 24(6): 125-127.LuJinhui,ShiXiangquan,DingQinghai,etal.Analysisofrandombinaryphase-codedpulseradarsignal[J].ActaElectronicaSinica, 1996, 24(6):125-127. [2]SitlerKL.Highrangeresolutionprofilingusingphase-coded,stepped-frequencywave-forms[J].ElectronicsLetters, 2002, 38(1):46-48. [3]EinsteinTH.Generationofhighresolutionradarrangeprofileautocorrelationfunctionsusingstepped-frequencypulsetrains[D].Massechusetts:MITLincolnlaboratory, 1984. [4]LongT,LiD,WuQZ.Designmethodsforstepfrequencywaveformandthetargetpick-upalgorithms[J].SystemsEngineeringandElectronics, 2001, 23(6):26-31. [5] 靳 凯, 王卫东, 王东进. 一种脉内相位编码脉间步进频雷达信号的研究[J]. 中国科学技术大学学报, 2006, 36(2): 137-142.JinKai,WangWeidong,WangDongjin.Thestudyonanewradarwaveform(PCSF)withhighrangeresolution[J].JournalofUniversityofScienceandTechnologyofChina, 2006, 36(2):137-142. [6] 胡柳荫. 宽带捷变频频率合成器研究[D]. 南京: 南京理工大学, 2010.HuLiuyin.Researchoffastwidebandfrequencysynthesizers[D].Nanjing:NanjingUniversityofScienceandTechnology, 2010. [7] 赵志勇, 常文革, 黎向阳. 一种宽带信号产生的DDSPLLHybrid新型结构及实现[J]. 国防科技大学学报, 2013, 35(4): 103-108.ZhaoZhiyong,ChangWenge,LiXiangyang.AnovelDDS-PLLhybridstructureforwidebandsignalgeneration[J].JournalofNationalUniversityofDefenseTechnology, 2013, 35(4): 103-108. [8]WangHY,WangHF,RenLX,etal.LowspuriousnoisefrequencysynthesisbasedonaDDS-drivenwidebandPLLarchitecture[J].JournalofBeijingInstituteofTechnology, 2013, 22(4):514-517. [9] 刘 林, 田进军, 刘朝辉. 基于DDS和直接频率合成技术的超宽带捷变频源设计与实现[J]. 兵工学报, 2010, 31(12): 1648-1652.LiuLin,TianJinjun,LiuZhaohui.Ultra-widebandfrequencyagilesourcedesignandimplementationbasedonDDSanddirectfrequencysynthesis[J].ActaArmamentarii, 2010, 31(12): 1648-1652. 翟腾普 男,1989年生,硕士研究生。研究方向为信号与信息处理。 任丽香 女,1971年生,博士。研究方向为宽带雷达信号处理。 刘泉华 男,1982年生,博士。研究方向为雷达系统与雷达信号处理。 王昊飞 男,1990年生,博士研究生。研究方向为宽带雷达信号处理。 Design and Implementation of Frequency Synthesizer for Wideband PCSF Radar Signal ZHAI Tengpu,REN Lixiang,LIU Quanhua,WANG Haofei (School of Information and Electronics, Beijing Institute of Technology, Beijing 100081, China) A method of producing arbitrary phase coded stepped-frequency (PCSF) radar signal was proposed based on the characteristics of this signal which incorporates complex programmable logic devices, direct digital synthesizer (DDS) and phase-locked loop-based frequency multiplexer. A S-band PCSF frequency synthesizer with low spurious noise and wideband was built using this method. With this method, phase of the output signal can be precisely controlled, and output of DDS was selected to ensure low spurs in the entire bandwidth. Experimental results demonstrate that at 320 MHz the overall spurious free dynamic range was better than 62 dBc and the phase noise was lower than -110 dBc/Hz@1 kHz. phase coded stepped-frequency; direct digital synthesizer; phase-locked loop 10.16592/ j.cnki.1004-7859.2015.09.016 翟腾普 Email:neuq50815ztp@126.com 2015-04-08 2015-07-16 TN74 A 1004-7859(2015)09-0067-04

3 频率源性能分析及测试

4 结束语