基于FPGA的雷达干扰效果评估接收机设计

李 洋,郑 辉

(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

基于FPGA的雷达干扰效果评估接收机设计

李 洋,郑 辉

(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

测试雷达干扰设备性能得到雷达干扰效果评估结果,就要完成加干扰后雷达信号的特征参数提取.介绍了一种基于高速A/D、FPGA、串口组成的雷达干扰效果评估接收机.其接收经过微波前端处理得到的中频信号,通过A/D采样,再利用FPGA系统得到功率、脉宽、带宽时延等参数.信息的测试结果通过串口上报给上位机以完成干扰效果的估计.

FPGA;CORDIC;干扰效果评估接收机

干扰效果评估是指对雷达信号进行干扰以后,定性或定量的对其产生的干扰效果的评价[1].干扰效果评估是对实战、试验及电子对抗设备的研制都很重要的一项用来衡量雷达干扰设备干扰性能的综合性指标[2].想要对干扰效果进行评估就必须要提取加扰后的雷达信号的特征参数,基于这些参数信息对其信号进行数学分析,从而得到评估结果.加扰后的雷达信号的接收需要具有高分辨率、高灵敏度、较宽输入带宽、较大的动态范围等能力,要求必须对信号参数进行快速且高精度的测量[3].本文主要研究了基于数字正交下变频和CORDIC算法的信号瞬时特征参数提取.本文中干扰评估数字接收机要求接收来自前端的处理过的中频信号,用A/D芯片完成模数转换,将采样后的数据送入到FPGA系统中进行信号处理,通过对信号正交下变频、数字滤波、CORDIC运算等处理,得到目标信号的频率、相位、脉宽、功率、时序等参数,再由串口将数据发送给上位机进行数学分析.

1 系统框图

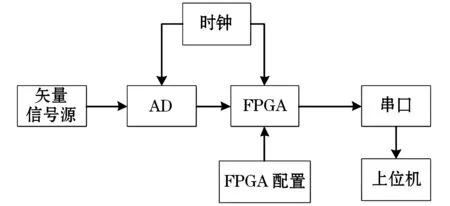

测试系统需完成的内容为:中频窄带信号通过SMA接口接入测试评估板内,先通过变压器电路将其有单端信号转换成差分信号,再将此差分信号送入12位分辨率的采样芯片中完成由模拟信号到数字信号的采集转变,之后将这12位信号通过LVDS引脚送入FPGA中,在FPGA中首先完成该信号的数字正交下变频,生成两路正交的信号,然后将此正交信号送入CORDIC模块中,可以得到此信号的相位和幅度信息,对其幅度信息取适当门限进行判断即可得到信号的脉宽,而对其相位信息进行解模糊和一阶差分运算即可得到信号的瞬时频率信息,对此瞬时频率信息进行判断识别就可得出相应的起始频率和截止频率及信号的带宽.在本测试板上,还有一用来计算时延的雷达同步脉冲的接入口,首先要对接入的脉冲进行电压转换,然后将此脉冲信号与输入信号比较,即可得到试验信息.将这些参数计算并整合成功后,存入FPGA的FIFO模块,再通过并行转串行的芯片和422串口,将这些参数传送至上位机.干扰评估数字接收机系统框图如图1所示.

图1 干扰评估数字接收机系统框图

本系统中,对数据的采样选用带通采样定理.Nyquist采样定理针对频谱分布在(0~fH)上的基带信号,fs≥2fH按照的采样速率对信号进行无混叠采样,采样后得到的数据中含有原始信号的全部信息.但是如果要对于频谱分布在频带(fL~fH)上的带通信号进行采样,虽然也能够按照Nyquist采样定理以fs≥2fH的采样速率对其进行采样,但是一般情况下带通信号的最高频率要远大于信号带宽,需要的采样率会非常高,使得对高速ADC采样器件的要求过高难以实现,且对后续的信号处理也有很高的要求[4].而通常情况下带通信号的带宽有限,远小于信号最高频率,所以自然会希望能用比Nyquist采样率低一些的的速率来进行采样并重建原始信号,带通采样定理就很好的解决了这类问题.

2 数字正交下变频及滤波器设计分析

2.1 数字正交下变频理论分析

模拟信号通过A/D采样采集后数字化成为数字信号,要对这个数字信号进行正交变换.数字混频正交变换方法是用数字信号与两个正交的本振序列相乘,再分别通过数字低通滤波器进行滤波即可实现.这种方法是运用数学运算,取得正交性的要求是保证运算过程的精度.其缺点是在采样速率较高时,低通滤波器需要有很高的阶数,比较不容易实现.基于多相滤波器的正交变换方法,可以解决滤波器阶数要求的问题,更易于实现.

在本实验中,由于采用带通采样方法:

(1)

对输入信号x(t)=a(t)·cos[2πf0t+φ(t)]按照带通采样频率对其进行采样得到,

(2)

取信号基带的同相分量xI(n)=a(n)cosφ(n),正交分量xQ(n)=a(n)sinφ(n)得,

(3)

(4)

(5)

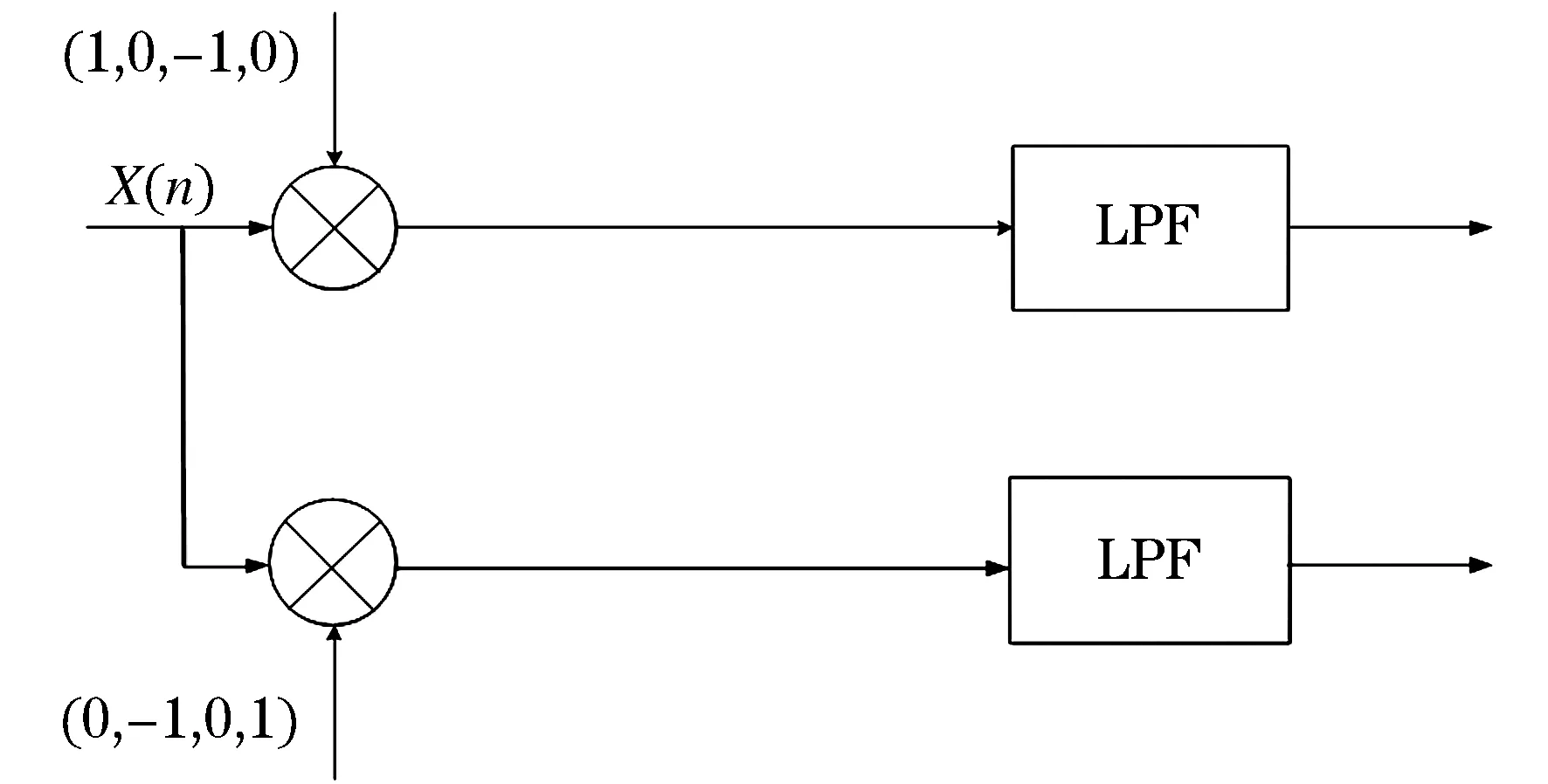

我们可以从上面的4个滤波器中选择一对来做为两个抽取结果对应的延时校正滤波器,要求满足条件|HIi(ejw)|=|HQi(ejw)|=1.即选择一个原型滤波器,对其进行4倍内插,得到其分支滤波器且其阶数仅为原型滤波器的1/4.在本设计的数字正交变换阶段,对本地载波信号的设计环节进行了简化,同相分量载波设置为[1 0-1 0],正交分量载波设置为为[0 1 0 -1],因而省去了复杂的NCO设计和乘法运算,更易于实现.此方法即相当于对信号进行二倍抽取而得到同相分量和正交分量,因此抽取后的信号在时域上会存在时延,因此在抽取以后需要用一个64阶的FIR滤波器分成为两组正交的分支滤波器,选取其中的一组就对其进行延时校正并且可以抑制带外噪声,这样就实现了数字正交下变频,得到I、Q两路正交信号.见图2.

图2 数字下变频模块设计

2.2 正交下变频的Matlab仿真设计

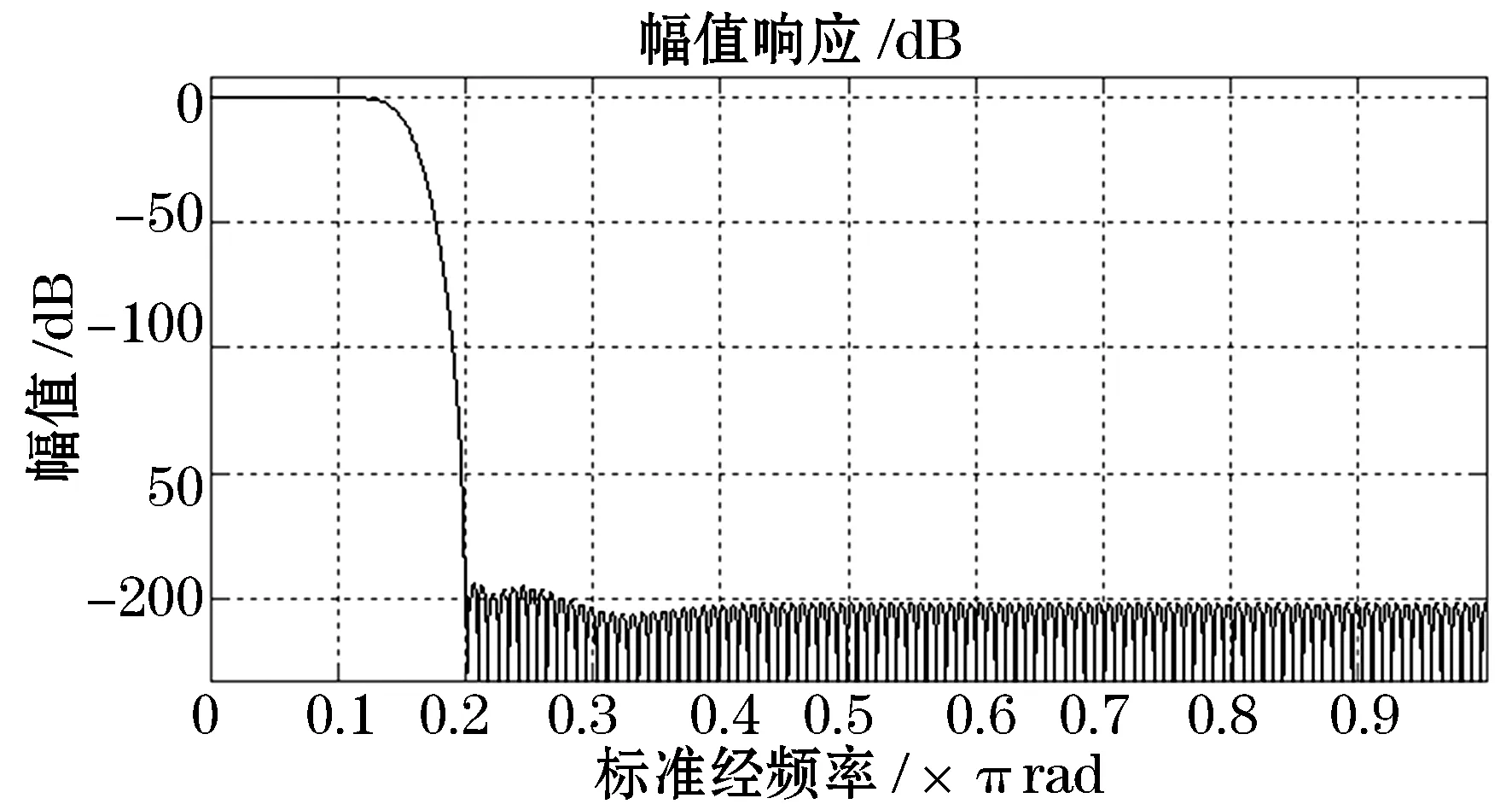

先需要用Matlab仿真软件根据设计的指标要求进行滤波器设计.本实验中选用FIR滤波器,采样频率设置为100MHz,通带设置为15 MHz,阻带设计为25 MHz,中心频率125 MHz,带宽15 MHz.用Matlab的firpm( )函数可以生成一个128阶的滤波器的滤波系数,将其进行相应的分组,在正交的两组分支滤波器中选择一组,分别作为对应的I、Q两路正交信号的滤波器,将参数取出并加载到FPGA的IP核的FIR模块中,便可利用FPGA实现该滤波器.其中Matlab产生的原始滤波器和抽取后的正交FIR滤波器如图3所示.

图3 原始FIR低通滤波器

图3所示为由Matlab的firpm( )函数产生的滤波器响应系数,通过fvtool对其观察的频率响应图,从图3中可以看出此滤波器的频率响应很好,应该具有较好的滤波性能,可以满足实验需要.

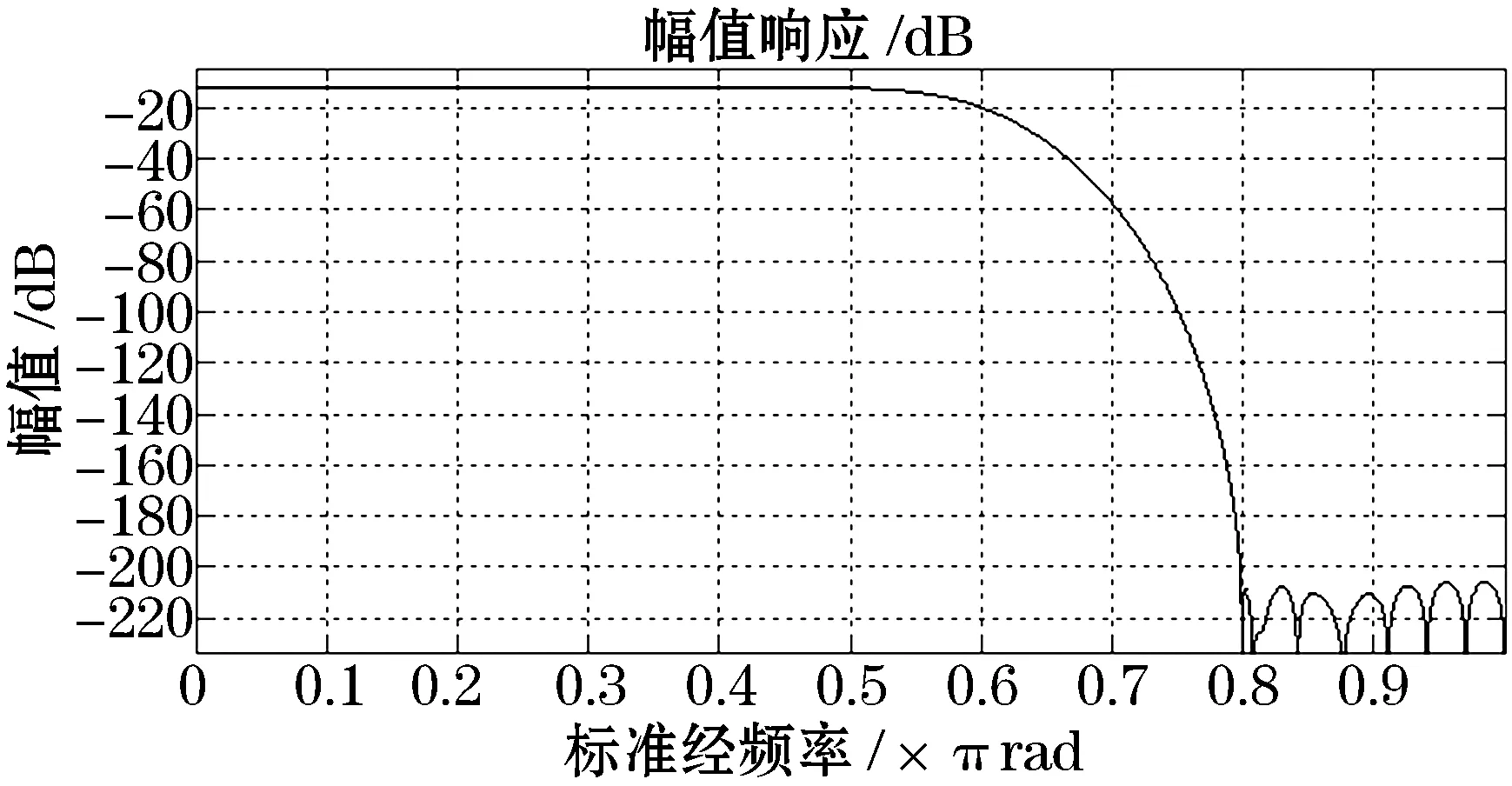

图4所示为由Matlab的firpm( )函数产生的原始滤波器响应系数经过分组后得到的两个正交滤波器的滤波系数,通过fvtool对其观察的频率响应图.从图4中可以看出,由于分组为抽取,这两个滤波器的通带和阻带有所展宽,而因为实际上分组得到的滤波器为将原始的滤波器响应系数分成4个,故其扩展大约有4倍左右.但是,可以从图4中看到这两个正交滤波器的频率响应也很好,应该具有较好的滤波性能,并没有因为分组而影响其率比性能,所以这组滤波器的响应系数可以满足实验需要,可以用作正交下变频后的滤波器使用.

图4 抽取后的FIR滤波器

3 基于CORDIC算法测相

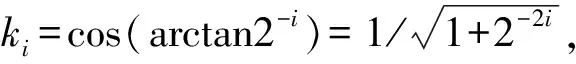

坐标旋转计算机算法(CORDIC)仅仅使用了移位和加法来代替复杂的乘法、正余弦、坐标变换、求模值等运算,非常适合在FPGA中使用来实现一些参数的测量[5].在本实验中,利用CORDIC算法计算信号的幅度、相位等信息,再进一步可计算出其他参数.该算法有向量和旋转两种实现方式,本设计采用旋转模式并且通过微旋转次数的合理选择可以满足在精度上的要求.CORDIC算法旋转模式下di=sign(zi),此算法是通过n次αi的微旋转来近似完成的旋转角度φ,即可以近似表示为:

(6)

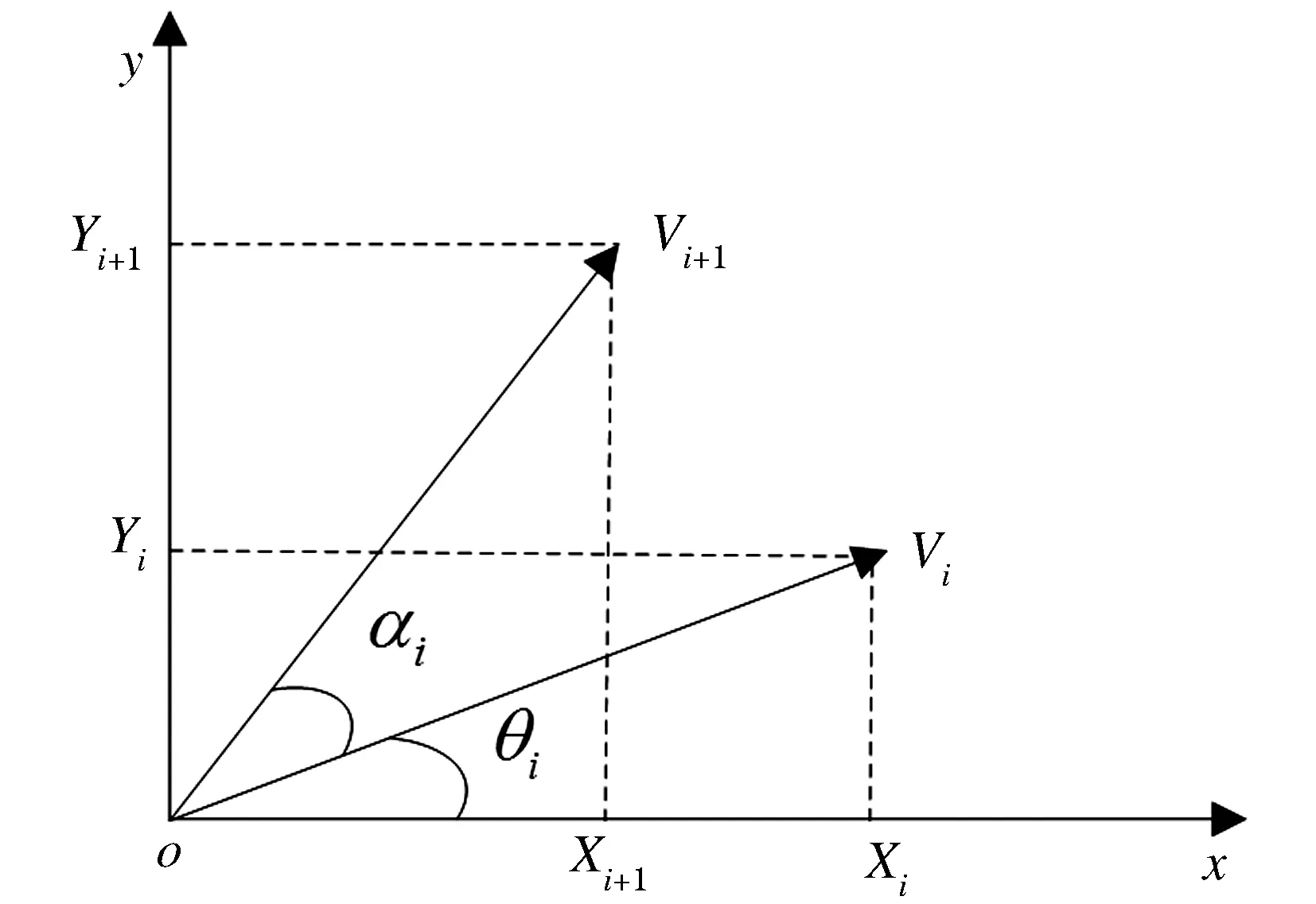

其中:第i次旋转方向由di确定,逆时针旋转时di=1,顺时针旋转时di=-1,αi为对应的旋转角度且其值恒为非负数.第i次微旋转过程示意图如图5所示,

CORDIC算法的递推是通过选择旋转αi来完成的,如果想要通过移位运算来完成相应的乘法运算,则需要选择一些特殊的αi.通常取:

αi=arctan2-i(i=0, 1, 2, 3…)

(7)

设向量Vi=[Xi,Yi]通过过旋转αi后变为向量Vi+1=[Xi+1,Yi+1],可得到微旋转方程为:

(8)

图5 第i次微旋转示意图

(9)

如果想恢复初始向量V1=[X1,Y1]所对应的相位,则可以选择

(10)

该定义式表示的是:若Yi<0时,加上的分量为正;若Yi≥0,加上的分量为负,直至最终使得|Yn|→0(当n→∞),相位值φ就可通过n次递推叠加而得到[6].同时也可以得到每次微旋转后的实际矢量角与目标角之间的误差为:

Zi+1=Zi-diarctan2-i

(11)

CORDIC算法采用的是流水线型微旋转结构,所以利用FPGA进行编程设计就可以实现该算法.由于该算法的每一流水单元中都是只含有加法器、移位器和一个系数存储器,用FPGA进行编程实现时,需要占用的资源数和存储器相对较少易于实现.当输入足够位数的I、Q两路正交信号时,其计算得到的相位信号的精度仅与微旋转迭代次数n的取值有关,即只取决于流水单元的个数[7].要满足一定的计算精度要求时,只需设置合理的迭代次数n,并不需要耗费大量FPGA的资源,在FPGA中利用较少的资源就可使用VerilogHDL语言进行编程实现.

而对数字信号而言,其瞬时频率函数f(n)与瞬时相位函数φ(n)之间的关系为:

(12)

其中:T为采样时间间隔,角频率ω(n)=φ(n)-φ(n-1),上式表明在数字域频率与相位可以表示为一阶差分关系[8-9].对CORDIC算法得到的瞬时相位做一阶差分便可得到瞬时频率.

4 实验结果及分析

4.1 AD采样数据的读取

由AD9230的DCO+、DCO-引脚送入FPGA内的100MHz的随路时钟读取由AD9230采集的数据,以由Agilent的83752A型信号发生器所产生的正弦信号和线性调频信号为例,FPGA读取到的AD采样的12-bit数据结果经由SignalTapII Logic Analyzer进行显示如图6所示.

图6 从AD9230读取的12位数字信号

图6所示的信号是频率为128 MHz由信号发生器输出的正弦信号,FPGA通过100 MHz的时钟速率对由AD9230通过LVDS引脚接入的采样数据结果进行观察的结果

4.2 数字正交下变频结果

由AD9230采集的12位数据经过混频即二倍抽取后,可得到两路存在延时的混频信号,再通过其相应的低通滤波器对其进行时延校正,可得到I、Q两路正交的数字信号.图7是用SignalTapII Logic Analyzer采集到的两路正交信号.

图7 两路正交数字信号

图7中所示的信号是频率为128MHz由信号发生器输出的正弦信号,经过数字正交下变频后由FPGA用100MHz的时钟速率进行观察的结果,II和QQ分别是数据的同向分量和正交分量,这两路信号的相位之间差90°为正交的.

4.3 CORDIC算法测量参数的实现

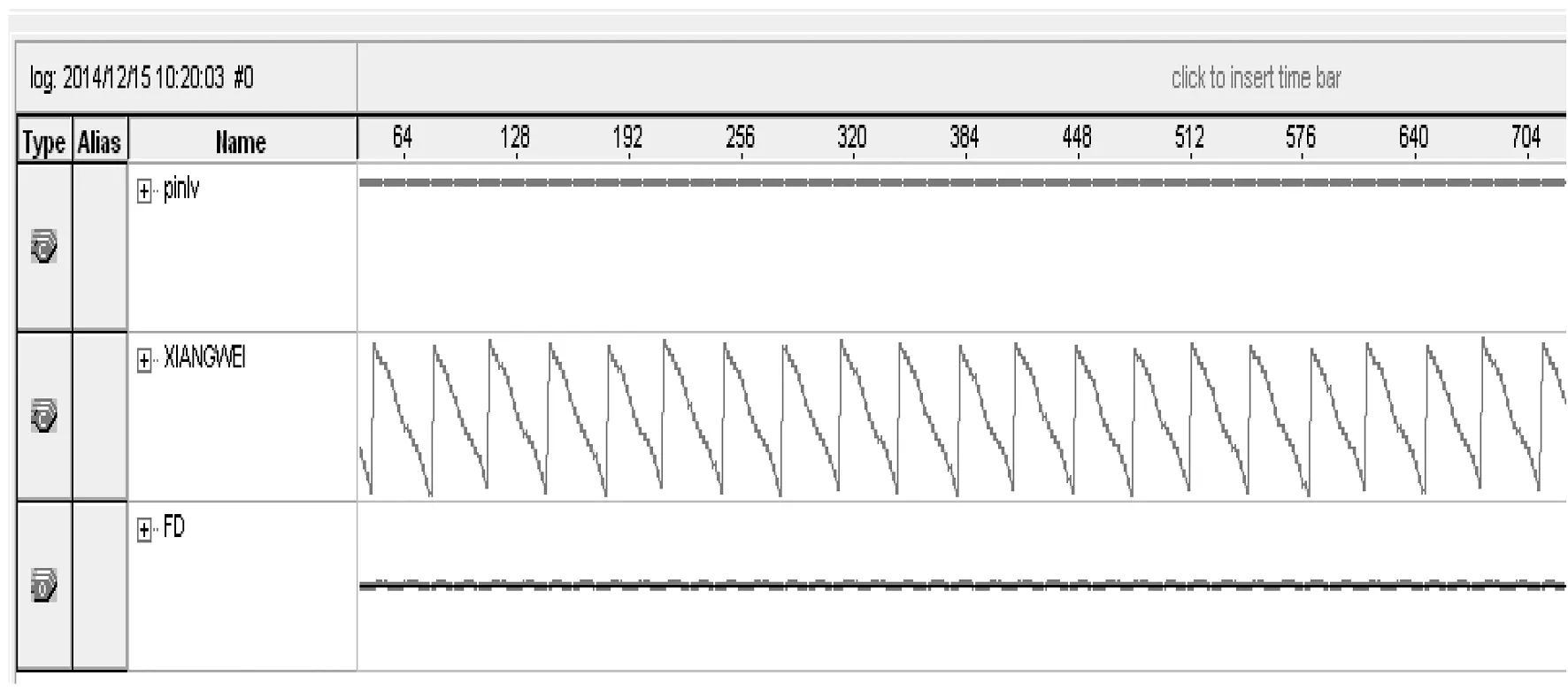

在FPGA中对得到的两路正交I、Q数字信号进行CORDIC运算,即可得到信号的相位信息和幅度信息,再对得到的瞬时相位进行一阶差分运算便可以得到其瞬时频率,并且通过得到信号的幅度信息设置判断门限,可以测量出信号的脉宽,而对瞬时频率信号进行判定就可以得到信号的起始频率、截止频率,进一步计算可以得到信号的带宽.用SignalTapII Logic Analyzer采集到得CORDIC算法测出的瞬时频率信息、相位信息和幅度信息如图8所示.

图8 基于CORDIC算法的结果图

图8中的信号XIANGWEI是将I、Q两路信号通过CORDIC运算得到的相位信息,FD信号为经过CORDIC运算得到的幅度信息,而pinlv信号则为对相位进行一阶差分运算得到的频率信息.图7中为信号源产生的常规正弦信号经过CORDIC运算得到的运算结果,从图8中可以看出对于单频信号在其信号每个周期内相位曲线虽然有所抖动但为一条斜率不为零的直线,而图中一阶差分运算得到的频率曲线基本上为一条水平直线即为单频信号,而信号的发射功率一定时,其幅度也为一定的即为一条直线,图8中的幅度信息虽略有变化但基本为一条直线.

由于加扰后的雷达信号为一脉宽有限的脉冲信号,因而通过对信号幅度信息的识别,即设置一门限就可以算得其脉宽,脉宽结果如图9.

图9 脉宽计算结果图

图9是通过对幅度判断得到的脉宽计算结果图,其中pul_width信号为信号脉宽的计数值,pul信号为通过幅度判断得到的脉冲波形整形信号.图中对脉宽为5 μs的信号进行脉宽技算结果,由于信号的混频抽取此时信号处理时钟为50 MHz,图中所示计数值为251,通过计算得到脉宽结果为5.02 μs,对脉宽的计算比较精确.

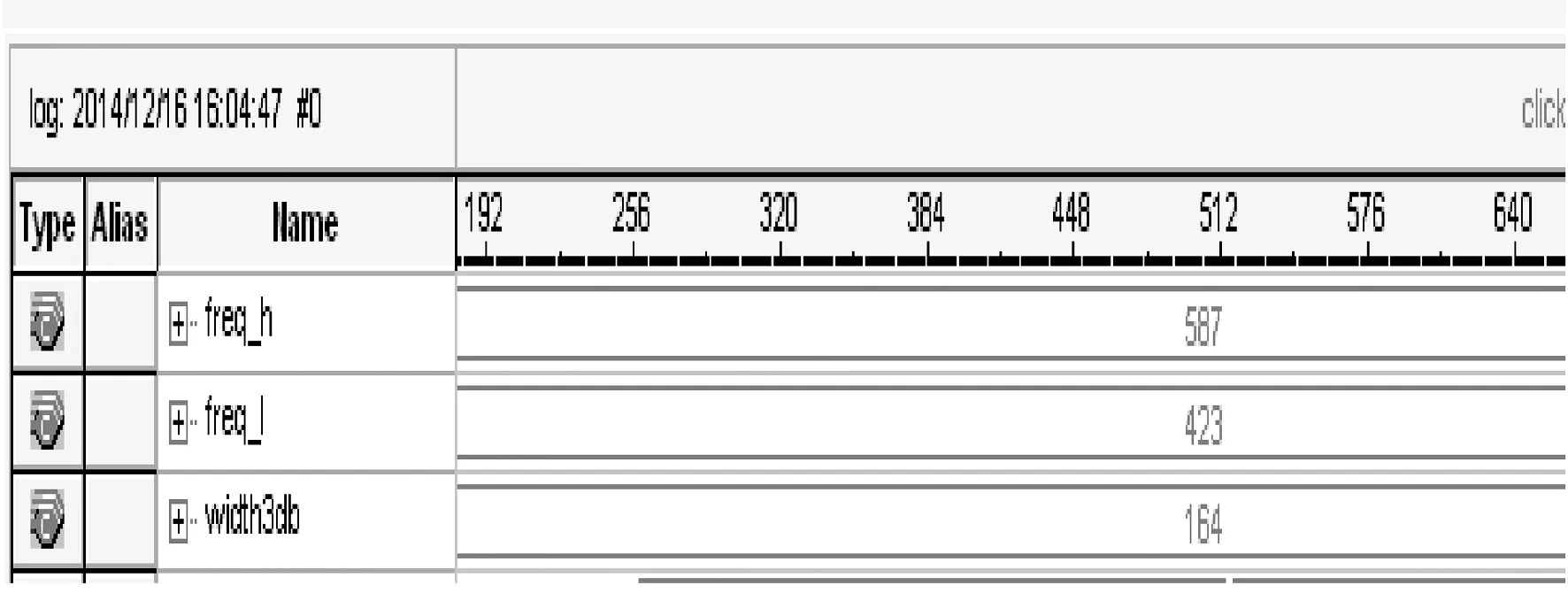

对相位信息进行一阶差分运算得到的瞬时频率信息进行判断识别,即可算得其起始频率和截止频率,通过起始频率和截止频率之差即可得到带宽.对于线性调频号其结果如图10.

图10 频率带宽计算结果图

图10中是线性调频信号的起始频率、截止频率和带宽的计算结果图,其中freq_h信号为信号的起始频率量化结果,freq_l信号为信号截止频率量化结果,width3db信号为其带宽量化结果.图中对中心频率为125 MHz,带宽为8 MHz,脉宽为10 μs的信号进行测量的结果,由于对应的量化关系为处理时钟对应于量化值1 024,图中所示其对应的量化值为587、423、164,通过计算得到起始频率结果为128.662 MHz,截止频率结果为120.654 MHz,带宽结果为8.007 MHz.

5 结 语

本文完成了基于FPGA+DSP的雷达干扰效果评估接收机设计,研究了基于CORDIC算法的信号瞬时特征参数提取.其中说明了提取信号瞬时幅度、瞬时相位、瞬时频率、信号脉宽、带宽的方法,并根据该数学模型完成在FPGA内部的VHDL程序编写,并在信号发生器模拟正弦信号的基础上完成对信号瞬时特征参数的提取将结果通过串口上传给上位机.其中对比了这两种方法测频的时间与精度,CORDIC算法计算很快且精度较为0.39 M.本实验中保证系统采样率不低于100 M,可连续采样10ms数据,时间测量精度100 ns,脉宽测量精度精度20 ns.基于这些参数信息,通过对干扰信号进行数分析,即可得到改干扰信号在时域、频域上的特征,对其进行综合分析,即可得到对雷达干扰能力的综合评估.

[1] GJB891A, 电子对抗术语[S].

[2] 徐 飞, 张冠杰, 陈 矛. 基于FPGA的一种电子战接收机信道化设计[J]. 火控雷达技术, 2008, 37(1): 74-78.

[3] HE T, JING X R. Modulation classification using ARBF networks[C]// Beijing: ICSP, 2004. 1809-1812.

[4] 杨小牛, 楼才义, 徐建良. 软件无线电原理与应用[M]. 北京: 电子工业出版社, 2001.

[5] 刘 奕, 曾文海. CORDIC算法在数字在变频中的应用[J]. 电视技术, 2006, 04: 14-16.

[6] ZAHIRNIAK D R, SHARPIN D L, FIELDS T W. A hardware-efficient, multirate, digital channe1ized receiver architecture [J]. IEEE Transactions on Aerospace and Electronic Systems. 1998, 34(1): 137-151.

[7] HARRIS F J, DICK C, RICE M. Digital Receivers and Transmitters Using Polyphase Filter Banks for Wireless Communications [J]. IEEE Transactions on Microwave Theory and Techniques, 2003, 51(4):35-40.

[8] 付永庆, 李 裕. 基于多相滤波器的信道化接收机及其应用研究[J]. 信号处理, 2004, 20(5): 517-520.

[9] 樊宏伦.基于FPGA的GMSK调制器的设计实现[J].哈尔滨商业大学学报:自然科学版,2014,30(3):361-364,373.

Design of radar jamming effectiveness evaluation receiver based on FPGA

LI Yang, ZHENG Hui

(School of Information and Telecommunication, Harbin Engineering University, Harbin 150001, China)

To gain radar jamming effect evaluation results, characteristic parameter of radar single added interference should be extracted. The jamming effectiveness evaluation receiver was required to receive the IF signal, which was the scrambled radar signal after frequency converting, amplifying, filtering by microwave front-end. Through the high-speed A/D sampling, the FPGA system was able to calculating the signal frequency, power, pulse width, bandwidth, timing and other parameters. Information of the test results reported via a serial port to the PC to complete the interference effect estimates

FPGA; CORDIC; jamming effectiveness evaluation receiver

2014-12-17.

中央高校基本科研费专项基金(HEUCF140803).

李 洋(1989-),女,硕士,研究方向:宽带信号检测与识别.

TN972

A

1672-0946(2015)06-0735-06