标准数字CMOS工艺正交压控振荡器设计*

潘达杉,黄金明,冯 勇,闵 昊

(1.专用集成电路与系统国家重点实验室,复旦大学,上海; 2.上海高性能集成电路设计中心,上海 201204)

标准数字CMOS工艺正交压控振荡器设计*

潘达杉1†,黄金明2,冯 勇2,闵 昊1

(1.专用集成电路与系统国家重点实验室,复旦大学,上海; 2.上海高性能集成电路设计中心,上海 201204)

正交压控振荡器是高速链路中的一个关键部件.片上集成高质量品质的电感电容等无源器件是影响压控振荡器性能的关键因素.为了兼容传统的数字工艺,采用超深亚微米的数字CMOS工艺进行片上电感电容的集成,并基于此无源器件实现了基于电容耦合的正交压控振荡器,实现中心频率16.12 GHz,频率调节范围为10 %,1M频偏处的相位噪声为-112 dBc,相位误差小于0.39°.

QVCO; phase noise;CMOS工艺

超级计算机的研究者们越来越多的将研究重点聚焦在系统的高能效而不单单是系统的峰值性能.因此,单芯片集成多核心的发展方向取代了追求单芯片单核心频率提升的发展方向.单芯片可以集成的核心数量随着工艺特征尺寸的下降而增多,核心间的数据通信逐渐成为制约芯片整体性能的关键因素,提高处理器核心间数据通路的聚合带宽成为设计者的一个研究重点.高传输率的通信接口必将成为多核处理器的关键部件.UCLA的Frank等人在2007年左右提出了射频互连(RF-I)该方案可以进行单芯片集成,达到单数据通路>10 Gbps的传输率[1].该方案的原理是将基带数据调制到更高频带的载波上,通过数字频带数字基带同时传输来提高单数据链路的聚合带宽.该射频互连系统的一个重要模块是生成载波的振荡源.

为了避免单数据链路各频带间的干扰,通常需要将载波间的频率间隔设计为远远高于基带频率.对于差分传输系统来说,一个相位误差小的正交压控振荡器(以下简称QVCO)有利于提高系统的信噪比,因而改善其信噪比.

一般来说,高频压控振荡器采用电感电容谐振来实现.电感电容压控振荡器(以下简称LC-VCO)的性能由电感电容谐振腔的品质因数来决定.因此单芯片集成LC-VCO的设计难点在于高品质片上电感电容的设计.通常Foundry提供的RF CMOS工艺会对金属互连进行优化比如提高高层金属的厚度等.因此为了实现高品质因数的无源器件,设计者都会采用RF COMS工艺.对于数模芯片来说需要在单芯片上采用多种工艺,生产成本非常高.随着数模混合的需求的增长,很多射频模块有了数字实现的方案,因此采用标准的数字CMOS工艺来实现射频模块必将大大降低生产成本.本文采用超深亚微米标准数字CMOS工艺进行了片上电容电感的集成,并设计实现了中心频率为16 GHz,低相位噪声,低相位误差的QVCO.

本文的主要内容安排如下:第二节介绍QVCO的结构;第三节介绍片上无源器件的设计和QVCO的电路设计;第四节介绍QVCO的仿真结果;第五节为总结.

1 QVCO的结构

正交信号的产生有多种方式,比如RC-RC相移网络、正交分频器等等.对于QVCO的实现,目前最有吸引力的实现方式是通过两个对称LC-VCO的耦合来实现[6-8].传统的基于MOS管耦合的QVCO其相位误差因受到耦合管不对称的影响变大,并且需要消耗更多的功耗[9-10].为了降低功耗同时保证低相位噪声,采用硅体耦合技术[11],采用这种方式来降低相位误差.Sanjeev Jain[12]采用背栅耦合进一步降低了AM-PM的转换噪声,通过采用PMOS耦合避免了谐振腔Q值降低.

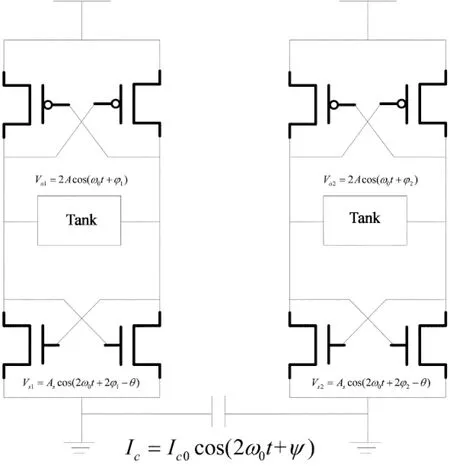

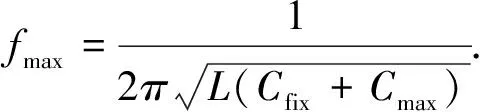

考虑到相位噪声、功耗和面积约束,本设计采用通过共源点电容直接耦合的方式,既实现了耦合又成为2倍频滤波电路的一部分,降低了相噪,同时保证了正交相位的精确性.其结构如下图1所示.

图1 本设计采用的电容直接耦合原理图

假设VCO的差分输出为

Vo1=2Acos(ω0t+φ1);

(1)

Vo2=2Acos(ω0t+φ2).

(2)

其中ω0是VCO的基频,A是单端振荡幅度,φ1和φ2是各自的相位.当VCO工作于电流限制区时,其共源极电压如下:

Vs1=Ascos(2ω0t+2φ1-θ);

(3)

Vs2=Ascos(2ω0t+2φ2-θ).

(4)

其中θ是输出与共源极之间的相位差.假设共源极的注入电流为

Ic=Ic0cos(2ω0t+ψ),

(5)

对于VCO1来说,该注入电流经过晶体管的下变频后流入到振荡器的电流为:

Iconv1=Aconvcos(ω0t+ψ-φ1).

(6)

振荡器要保持在ω0的振荡频率,需要注入电流与输出同相位,因此需要满足ψ=2φ1,从而使VCO1的相位锁定到注入电流相位的一半.而对于VCO2来说,注入的电流为

Iconv2=-Aconvcos(ω0t+ψ-φ2).

(7)

2 QVCO的设计

QVCO的设计主要是片上电感电容设计、互补交叉对管设计等.

2.1 片上电感电容设计

目标振荡频率为16 GHz,可以得到L*C=1.12e-22H*F,因此L为几百pH级,C为pF级,L使用单圈八边形拓扑结构,C采用金属侧壁电容以及累积型MOS管电容作为电压控制电容.

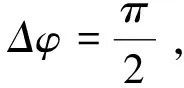

片上集成电感的难度在于金属厚度小,导致串行电阻过大,严重影响Q值.在65 nm工艺RF CMOS工艺中TOP层金属的厚度为3.4 μm,而在数字CMOS工艺中,TOP层金属的厚度为0.9 μm.因此使用标准数字CMOS工艺在进行片上电感集成时,难以获得足够高的品质因数,进而影响VCO的相位噪声.因此在进行电感设计时,我们综合考虑相位噪声及占用面积等制约因数,进行设计,使用最高层金属,对不同宽度和半径的拓扑进行仿真,图2是金属宽度为20 μm情况下电感的等效串联电阻、感值和Q值对电感半径的变化趋势.可以看到随着电感半径增大,Q值恶化的趋势变大.

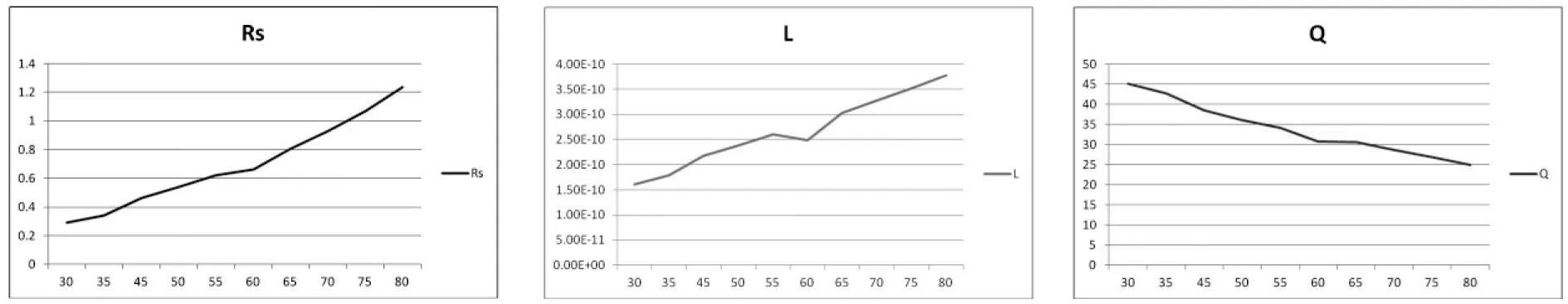

图3是电感半径在80 μm情况下电感的串联电阻、感值和Q值对金属宽度的变化情况,可以看到随着金属宽度的减下,等效串联电阻增加的程度大于L增加的程度,Q值在20 μm处有明显恶化.

图2 电感的等效串联电阻、电感及Q值对电感半径的变化情况(@16 GHz 20 μm线宽)

图3 电感的等效串联电阻、电感及Q值对金属线宽的变化情况(@16 GHz 80 μm半径)

根据上面的仿真,选取振荡器的电感为60 μm半径,20 μm宽度的单圈电感.如图4为所采用的电感版图,利用ADS的momentum进行电磁场仿真得到S参数模型供QVCO的系统仿真.

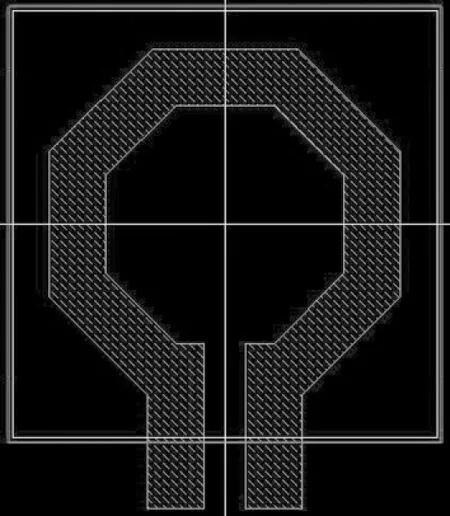

为了提高电感的品质因数,需要减少衬底的涡流损耗,因此在电感和衬底之间,加入了一层M1的十字交叉屏蔽层,如图5所示.

电液转向助力系统的特性曲线表达式为一个包含速度、方向盘转角(扭矩)、前轮气压和轴重等诸多因素的复杂非线性多元函数式.为了简化求解过程,在不影响分析结果的基础上,本文忽略次要的影响因素,只考虑2个主要变量:方向盘输入扭矩Td和速度v.全车速下助力特性曲线的函数表达式为

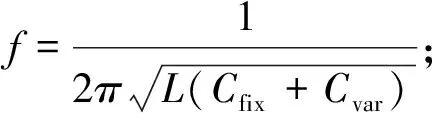

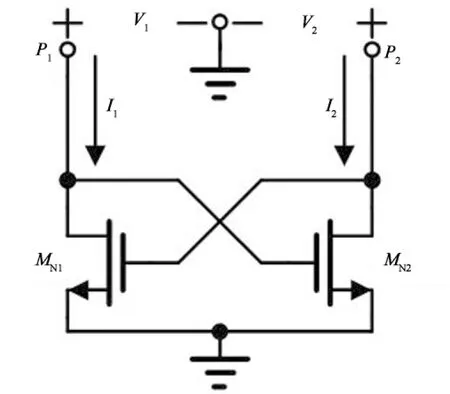

电容设计中使用金属侧壁电容及各种寄生电容形成Cfix,使用NWELL中的NMOS形成的积累型

MOS管电容作为Cvar,

根据频率公式以及10%的调谐范围,计算可得出Cfix=0.36pF,Cmin=60fF,Cmax=160fF

图4 电感版图

图5 电感衬底屏蔽版图

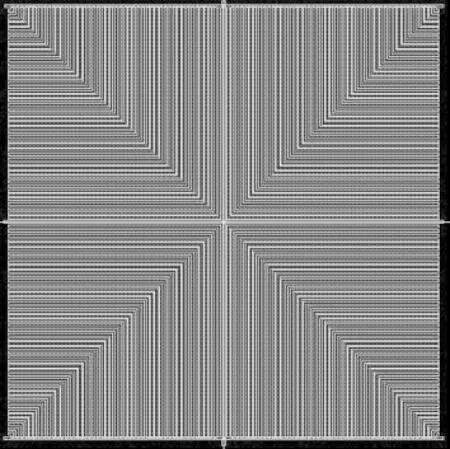

2.2 互补交叉对管

为了减小相噪,提高输出信号的幅度是其中一个方法,因此采用互补交叉对管来提供振荡器负阻.

由于振荡器输出信号为大摆幅的信号,因此在对负阻管子进行分析的时候需要采用大信号分析.

图6 负阻管大信号分析等效电路

V1gm2=I2;

V2gm1=I1.

(8)

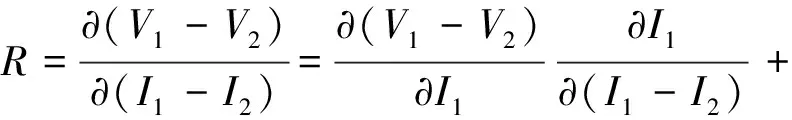

其中,gm2为对应于V1的Mn2管跨导,gm1为对应于V2的Mn1管跨导.由大信号得到阻抗,应由电压对电流取微分得到:

(9)

平衡态时,gm1等于gm2等于gm,得到负阻为-2/gm. 在LC振荡器中采用互补的交叉耦合管,其提供的负阻由PMOS 差分对和NMOS 差分对的跨导相加得到,即:

(10)

根据振荡器起振条件,需要满足Rp≥R,增加一些余量Rp≥3R.在保证PN管子gm一致的情况下决定P、N管子的尺寸.

2.3 低相位噪声设计

为了降低振荡器相位噪声,采取了如下低噪声设计技术.

1)去除尾电流

在高频振荡下,尾电流已经无法对流入tank的电流进行偏置,加上尾电流管子会引入额外的1/f噪声,因此在本设计中去除尾电流的设计.

2)采用2倍频滤波技术

采用在共源极增加电感电容在2倍频出谐振,提高共源极的阻抗.从而降低噪声.

3)电感提高目标频率下Q值

电感的版图设计时增加衬底隔离,见图7.

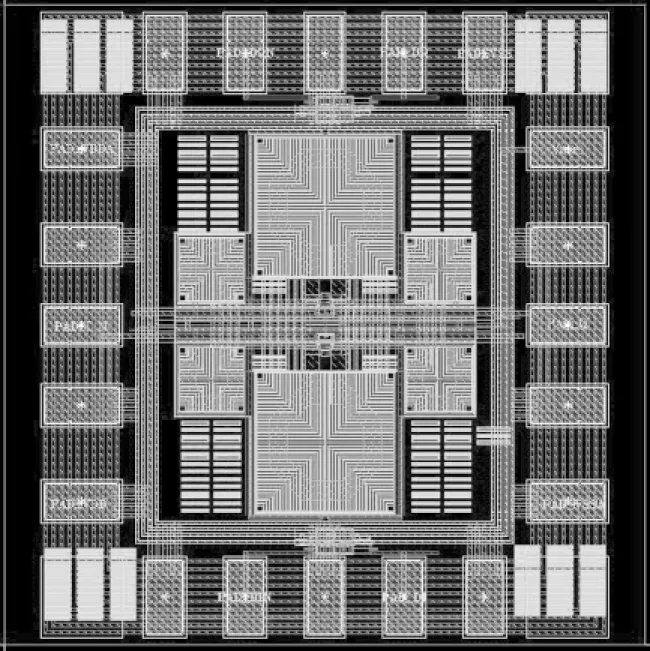

图7 QVCO的芯片版图

3 QVCO的仿真

在TT corner下仿真结果如下.

3.1 QVCO的中心频率

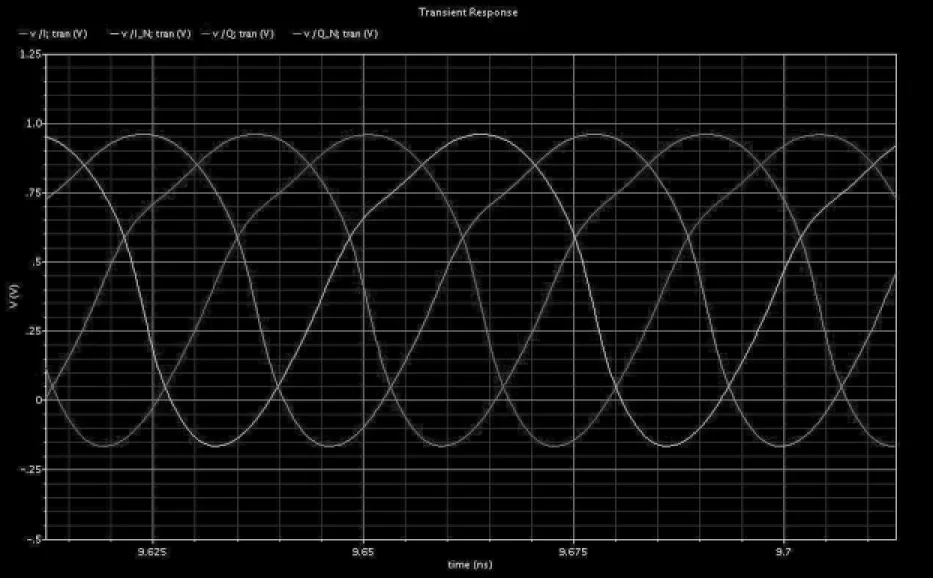

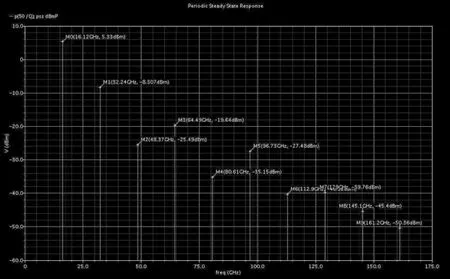

图8为QVCO的瞬态波形,图9为输出信号的各次谐波的输出,可以看到QVCO的基波频率为16.12 GHz,输出功率为5.33 dBm.

图8 QVCO的瞬态波形

图9 QVCO的频谱图

瞬态的平均电流为5.384 mA,得到QVCO的功耗为4.8 mW

3.2 QVCO的调谐范围

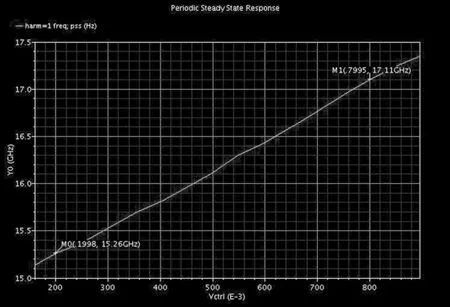

图10为QVCO的调谐范围,控制电压从0.2V调节到0.8V,其频率变化范围从15.26 GHz到17.11 GHz,条件范围达到11.5 %.

3.3 QVCO的相位噪声

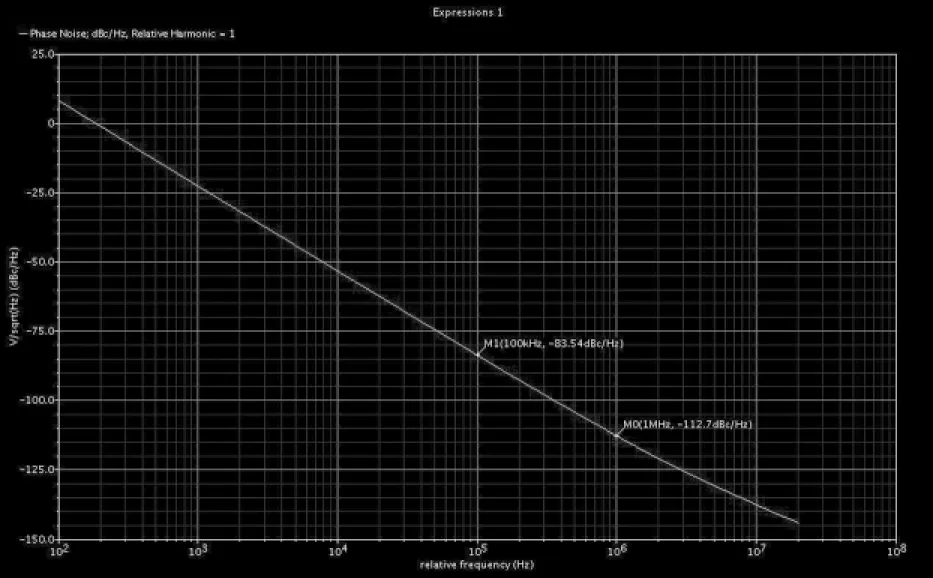

从图11可以看到该QVCO振荡频率为16 GHz时的相位误差在100 kHz频偏处为-83.53 dBc/Hz,在1M频偏处为-112.7 dBc/Hz.

图10 QVCO的调谐范围

图11 QVCO的相位噪声

3.4 QVCO的正交输出信号相位差

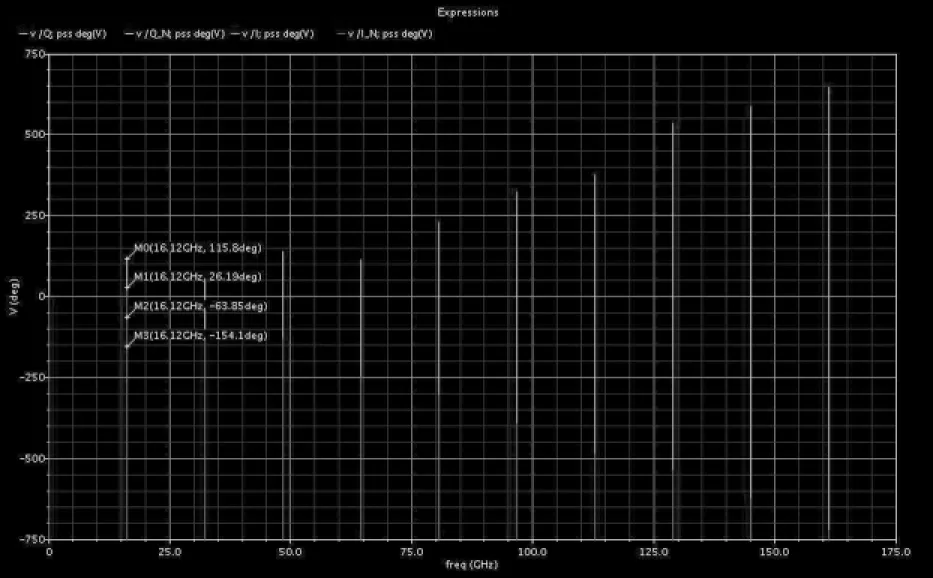

仿真环境下QCVO的正交信号相位差均小于0.39°,见图12,从仿真结果来看,基本满足设计预期.

图12 QVCO的正交信号相位差

3.5 设计比较

(13)

表1 QVCO FOM比较表

从表1可以看到本文的设计在FOM值上处于上游水平.

4 总 结

本文使用超深亚微米标准数字CMOS工艺实现了片上集成电感及金属侧壁电容,并基于该无源器件设计了一款基于电容耦合的正交压控振荡器,在仿真环境下,实现了10 %的频率调整范围,中心频率为16.12 GHz,相位噪声为-112 dBc@1Mhz,正交相位误差小于0.39°,QVCO核心功耗为4.86mW.目前该压控振荡器正在进行流片验证.该压控振荡器的设计表明了数字工艺进行微波射频设计的可行性,为微波射频收发器的全数字工艺集成提供了理论依据,可以进一步降低生产成本.该压控振荡器可为多核处理器芯片的高频PLL提供振荡源,也可为片上高数据传输率收发模块提供稳定的载波.

[1] SOCHER E, CHANG M-CF. Can RF help CMOS processors? [C]//Topics in Circuits for Communications, Communications Magazine, IEEE, 2007(8):104-111.

[2] TIEBOUT M. Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS [J]. Solid-State Circuits, IEEE Journal of, 2001,6 (7):1018-1024.

[3] GIERKINK S L J, LEVANTINO S, FRYE R C,etal. A low-phase-noise 5 GHz CMOS quadrature VCO using super harmonic coupling [J].IEEE J Solid-State Circuits, 2003,38 (7):1148-1154.

[4] HAJIMIRI A, LEET H.Design issues in CMOS differential LC oscillators [J]. IEEE J Solid-State Circuits, 1999,34 (5):717-724.

[5] YU S A, KINGET P.Scaling LCoscillators in nanometer CMOStechnologies to smaller area but with constant performance [J]. IEEETrans Circuits Syst II, Exp Briefs, 2009,56 (5):354-358.

[6] ROFOUGARAN A,RAEL J, ROFOUGARAN M,etal. A 900 MHzCMOS-oscillator with quadrature outputs[C]//IEEE ISSCC Tech Dig.1996: 392-393.

[7] JANG S L, HUANG SS,LEE C F. CMOSquadratureVCOimplemented with twofirst-harmonic injection-locked oscillators [J]. IEEEMicro w Wireless Compon Lett, 2010,18 (10):695-697.

[8] JANG S L, SHIH C-C,LIU C-C,etal. A0.18umCMOSquadrature VCO using the quadruple push-push technique [J].IEEE Micro w Wireless Compon Lett, 2010,20 (7): 343-345.

[9] TANG J, VEN P, KASPERKOVITZ D,etal. Analysis anddesign of an optimally coupled 5 GHz quadratureLC-oscillator [J]. IEEEJ Solid-State Circuits, 2002,37 (5):657-661.

[10]ANDREANI P, BONFANTI A, ROMANò L,etal. Analysis anddesign of a 1.8 GHz CMOSLC quadrature VCO[J]. IEEE J Solid-StateCircuits, 2002,37 (12): 1737-1747.

[11]LIU P, SAH S P, YU X,etal. Design techniques for load-independent direct bulk-coupled low power QVCO[J]. Microwave Theory & Techniques IEEE Transactions on, 2013, 61:3658-3665.

[12]JAIN S, JANG S L. Indirect Back-Gate Coupling Quadrature LC-VCO [J]. Microwave & Wireless Components Letters IEEE, 2014, 24(2):117-119.

[13]YI X, BOON C C, LIU H,etal. A 57.9-to-68.3 GHz 24.6 mW frequency synthesizer with in-phase injection-coupled QVCO in 65 nm CMOS technology [J]. IEEE Journal of Solid-State Circuits, 2014, 49(2):347-359.

[14]IKEDA S, KAMIMURA T, Sang-yeop LEE,etal. A transformer-based current-reuse QVCO with a capacitor coupling technique in 180 nm CMOS[C]//Proceedings of the 8th European Microwave Integrated Circuits Conference.2013:93-96.

Design of Quadrature VCO Based on Standard CMOS Process

PAN Da-shan1†, HUANG Jin-ming2, FENG Yong2,MIN Hao1

(1.State Key Laboratory of ASIC and System, Fudan Univ, Shanghai 200433, China;2.Shanghai High Performance IC Design Center, Shanghai 201204, China)

Quadrature VCO is one of the key components in high speed data link. High Q on-chip inductance and capacitance integration is a key fact, which highly affects the performance of Voltage Controlled Oscillator. In order to fully compact the traditional digital CMOS process, we have designed on-chip inductance and capacitance with ultra-deep submicron digital CMOS process, based on which a capacitive coupling quadrature VCO is implemented. According to the simulation, the center frequency of QVCO is 16.12GHz, with 10% frequency tuning range, -112dBc@ 1MHz phase noise and 0.39°phase error.

quadrature voltage-controlled oscillator;phase noise; CMOS technology

1674-2974(2015)08-0094-06

2014-06-20

2013年核高基“超级计算机处理器研发”课题(2013ZX01028-001-001-001);国家高技术研究发展计划资助项目 (2011AA010404);国际科技合作项目(2010DFB13040)

潘达杉(1983-),男,浙江富阳市人,博士研究生

†通讯联系人,E-mail:shot1123@163.com

TP302

A