高精度低功耗Sigma-Delta 调制器的设计

魏榕山,陈林城

(福州大学 物理与信息工程学院,福建 福州 350116)

随着半导体集成电路制造工艺的不断发展,片上系统(SOC)已成为设计技术发展的主流,并在手持音频设备和传感器等领域得到了广泛的应用。众所周知,SOC 设计是基于大量可重用的知识产权模块(IP)基础上。在这些IP 中,模数转换器(ADC)因处于连接模拟和数字信号的桥梁位置而受到关注。由于手持设备中的电池容量有限,又对音质等有较高要求,所以ADC 的设计重点在于低功耗和高转换精度。在各种类型的ADC 中,Sigma-Delta ADC 是实现中低速、高精度ADC 的首选,尤其在传感器和语音处理等领域得到了广泛的应用[1-2]。

本文设计了一个应用于音频和传感器领域的四阶单环一位前馈型的Sigma-Delta 调制器(Sigma-Delta ADC 的核心部分),通过开关电容型全差分电路的使用,有效减小了偶次谐波、衬底以及电源噪声;通过斩波技术的使用,降低了直流失调和低频噪声(主要是1/f 噪声),达到了提高信噪比的目的。该调制器采用Global Foundries 0.18 μm CMOS 工艺实现,电源电压为1.8 V,过采样率128,时钟频率5.12 MHz。仿真结果表明调制器的信噪比达100.2 dB,整个调制器功耗为380 μW,满足低功耗和高精度的设计要求。

1 Sigma-Delta 调制器系统设计

1.1 系统结构和参数的设计

Sigma-Delta 调制器有3 个重要的系统参数,分别位为量化器位数M,系统阶数L,以及过采样率OSR[3-4]。这些参数的不同组合,构成略有差异的量化噪声整形效果。带内残留噪声总能量,与OSR 的2L+1 幂次成反比关系[1]。从而增加OSR,或增加L均能明显降低残留噪声。增加量化器位数M,将减少量化阶梯。但若量化器的位数超过1 位,反馈器件间存在不匹配性,将降低系统转换精度。要使用动态器件随机算法(DER)才能消除不匹配性,这会设计增加难度[5-6],从而本设计选用1 位量化器。

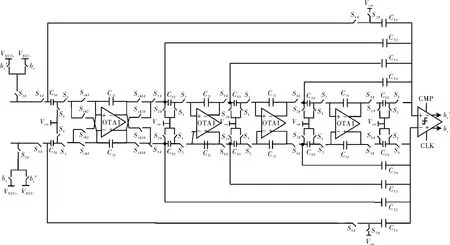

Sigma-Delta 调制器传递函数主要包括反馈结构(CRFB)和前馈结构(CRFF)。这两种结构均可实现积分器的输出信号中仅处理噪声分量,但实现条件不同。在CRFF 中,需满足的条件是bi=0(2≤i≤L),相反在CRFB 中需满足的条件是ai=bi(i≤L)[7]。对比之下,CRFF 结构需要更少的信号支路,从而需要更少的开关和电路,降低了支路上的噪声和积分器输出信号的幅值,从而减小整个Sigma-Delta 调制器的功耗。因此,从低功耗的角度,本设计采用CRFF 结构,如图1 所示。

图1 CRFF 结构四阶单环一位调制器原理图

综上分析,为实现设计目标,即转换精度在98 dB以上,以及留出一定的余量,最终选择的能够实现设计目标的解决方案是:OSR=128(OSR 通常为2 的N 幂次),L=4,M=1,CRFF 结构。选取系统传递函数NTF的带外增益Hinf=1.45(经验值,通过Matlab DStoolbox 对NTF 传递函数进行综合,得到整个系统系数。

1.2 系统电路的设计

根据Matlab 模型,结合系统工作时序,音频Sigma-Delta 调制器电路系统框图,如图2 所示。根据音频Sigma-Delta 调制器中系统框图,共需10 个时钟控制信号,分别为:S1,S2,Sld,S2d,Schl,Sch2,Schld,Sch2d,CLK,CMP。前面4 个时钟保证系统采样积分能正常工作;中间4 个时钟完成chopper 的功能,后面2 个时钟为比较器时钟。时钟S1,S2为非重叠两相位时钟。Sld,S2d分别为S1,S2的上跳变相同,下跳变延迟时钟,后面几组时钟类似。

在系统中,4 个OTA 组成4 个级联的积分器。积分器的增益由积分电容与采样电容比值决定。每一个积分器的输出,有一条前馈回路至量化器。参考信号VREF+,VREF-反馈到第一个OTA 的输入。量化器在S1相位即将结束时比较输入端信号幅值的相对大小,实现了对模拟输入信号的数字转换。在S2相位,依据当前输出数字信号,反馈VREF+或VREF-到第一级OTA 的输入,形成负反馈。第一级OTA 的4 个斩波开关用来实现斩波技术,将低频噪声和直流失调被调制到高频段,最终被Sigma-Delta ADC 的滤波器滤除掉,从而提高Sigma-Delta 调制器的信噪比,也使其能应用于超低频传感领域。

图2 Sigma-Delta 调制器原理图

2 Sigma-Delta 调制器电路模块设计

2.1 第一级采样电容

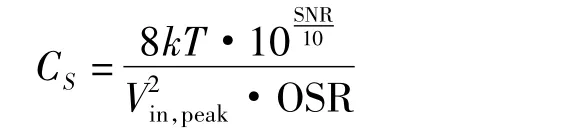

采样电容取值,取决于系统设计目标。过大的采样电容,将给运算放大器等具体电路设计增加难度。相反,由于电容热噪声,过小的采样电容,将增加电容热噪声密度。在两相位差分系统中,经过推导得到的采样电容取值表达式可写为

其中,Vin,peak为输入满幅信号幅值,于是得到采样电容的最小取值CS=1.63 pF。

2.2 其它电容

其他级热噪声均有被系统整形,带内残留的噪声很小,采样电容取值在1 pF 以下即可。为取值简单起见,文中将二、三、四级的积分电容都定为1 pF,然后根据积分系数便可确定各级采样电容的大小。前馈支路热噪声同样有被系统整形,电容取值也在1 pF 以下。

2.3 运算放大器

本文选择有较大输出电压摆幅的全差分型折叠式共源共栅的OTA 进行设计。本文设计的四阶调制器中,OTA 的增益通常应高于60 dB,对于折叠共源共栅式结构的运放来说基本都能够达到要求。OTA 的增益带宽积GBW 通常取时钟频率的3 ~5 倍,为节省功耗,增益带宽积应该尽量取小,但过小会降低积分器的积分精度、产生谐波失真等问题。因此,要在功耗和增益带宽积中进行折中处理。共模反馈电路一般分为开关电容型(SC)和连续时间型(CT)[8]。采用开关电容型共模反馈能够有效节省功耗,并且不会限制主运放的输出摆幅。

图3 OTA1 原理图

表1 各运算放大器性能参数

2.4 比较器

一位量化器通常由比较器构成。比较器一般分为静态锁存比较器、甲乙类锁存比较器和动态锁存比较器[8]。相对于静态锁存比较器、甲乙类锁存比较器,动态锁存比较器由于动态特性使其具有更低的功耗,有利于降低芯片的整体功耗。因此,本文采用动态锁存比较器,其结构如图4 所示,主要由预放大运放和锁存器构成。比较器由两个反相非交叠时钟控制,其中CLK 为比较器工作时钟,CMP 为比较时钟,时序如图4所示。

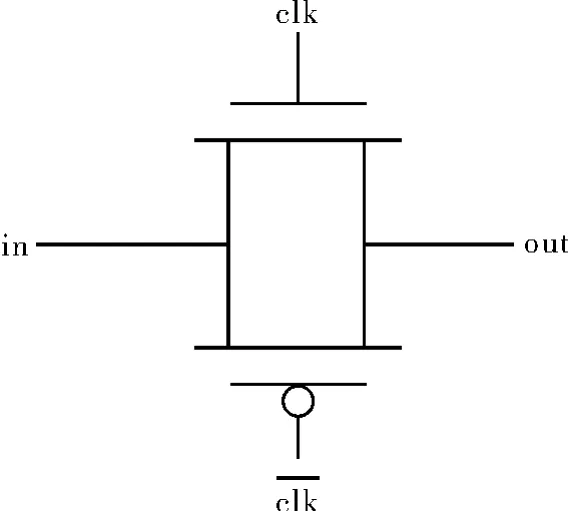

2.5 开关

在开关电容电路中,由于开关的非理想因素,存在导通电阻,影响电路的性能。为提高电路的线性度,一般采用传输门结构的CMOS 开关,其结构如图5 所示。这种结构的开关可提供轨到轨的反相输出,比单个MOS 管开关具有更好的线性度。因此,本文调制器中的开关均选用CMOS 开关。在设计时,通过设置合理的参数,使得NMOS 管和PMOS 管的导通电阻相等,这样并联后可得到最小的CMOS 开关导通电阻。

图5 CMOS 开关原理图

3 结果及分析

本设计电路基于Global foundries 0.18 μm CMOS工艺,电源电压为1.8 V,过采样率为128,时钟频率为5.12 MHz。Sigma-Delta 调制器频域特性曲线如图6所示。仿真结果表明,通过斩波技术的使用,把输入信号和开关型方波信号耦合再经同步解调后,信号的频谱不变,而低频噪声和直流失调被调制到高频段,最终被Sigma-Delta ADC 的滤波器滤除掉,从而有效降低了直流失调和低频噪声,一方面保证调制器的精度,另一方面也使设计能够应用于低频传感器领域;通过开关电容型全差分电路的使用,有效减小了偶次谐波、衬底以及电源噪声,从而保证了整个调制器的精度;通过采用CRFF 结构减少了信号支路,从而减少了开关和电路的数量,减低了支路上的噪声和积分器输出信号的幅值,从而使整个Sigma-Delta 调制器的功耗显著降低,整个调制器的功耗仅为380 μW,信噪比达100.2 dB,达到了高精度和低功耗的设计目的。

图6 调制器频域特性曲线

4 结束语

本文设计了一个应用于音频和传感器领域的四阶单环一位前馈型的Sigma-Delta 调制器。该调制器采用Global foundries 0.18 μm CMOS 工艺实现,电源电压为1.8 V,过采样率128,时钟频率5.12 MHz。仿真结果表明,调制器的信噪比达100.2 dB,整个调制器功耗仅为380 μW。通过斩波技术的使用,降低了直流失调和低频噪声,达到了提高信噪比的目的。通过开关电容型全差分电路的使用,有效减小了偶次谐波、衬底以及电源噪声,达到了提高精度和降低功耗的目的,满足高性能和低功耗的要求。

[1] Richard Schreier,Gabor C Temes.Understanding delta-sigma data converters[M].New Jersey:Wiley IEEE Press,2005.

[2] Steven R Norwworthy,Richard Schreier,Gabor C Temes.Delta-sigma data converters theory,design,simulation[M].New Jersey:Wiley IEEE Press,2004.

[3] Souri K,Chae Y,Makinwa K A A.A CMOS temperature sensor with a voltage-calibrated inaccuracy of±0.15 ℃(3σ)from -55 to 125 ℃[J].IEEE Journal Solid-State Circuits,2013,48(1):292-301.

[4] Razavi B,Wooley B A.Design techniques for high speed,high resolution Comparators[J].IEEE Journal Solid-State Circuits,1992,27(12):1916-1926.

[5] Marzia Annovazzi,Vittorio Colonna,Gabriele Gandolfi,et al.A low-power 98dB multibit audio DAC in standard 3.3 V 0.35 CMOS technology[J].IEEE Journal of So1id-State Circuits,2002,37(7):825-824.

[6] Yang Yuqing,Amiya Chokhawala,Mark Alexander,et al.A 114 dB 68 mW chopper-stabilized stereo multibit audio ADC in 5.62 mm2[J].IEEE Journal of Solid-State Circuits,2003,38(12):206l-2068.

[7] Benabes P,Gauthier A,Billet D.New wide band sigma-delta converter[J].IEEE E1etronic Letters,l993,29(17):1575-l577.

[8] Markus J,Silva J,Temes G C.Theory and applications of incremental sigma-delta converters[J].IEEE Transactions on Circuits and Systems I-Regular Papers,2004,51(4):678-690.