基于统计算法的DDR4 DQ 信号误码率眼图的实现

王怀亮,徐志华,严锦荣,李亚婷,姜 丰,周子翔

(西安电子科技大学CAD 研究所,陕西 西安 710071)

基于最大失真分析方法(Peak Distortion Analysis,PDA)的缺陷[1],以及链路结构变得越来越复杂,链路建模和仿真分析技术需要作出创新。现代链路分析算法都是基于统计域的。基于概率密度函数(Probability Density Function,PDF)、累积分布函数(Cumulative Distribution Function,CDF)以及相应卷积运算的统计信号分析方法正在逐渐取代传统落后的峰-峰值和方差等度量方法。国外在Intel 和Rambus 方面有许多专家学者进行了研究[2-5]。国内尚未找到相关报导。西安电子科技大学CAD 电路设计研究所信号完整性课题组已就此展开了相关研究。

1 链路体系结构

为了预估数Gbit/s 数据率时高速链路的误码率、确定接收器的最佳采样区域,首先介绍链路的体系结构与部件。图1 所示是一个简化的串行链路体系结构。

图1 串行链路体系结构

2 链路的LTI 等效模型

本文将线性时不变(Linear Time Invariant,LTI)理论作为发送器、信道或者媒质以及接收器链路子系统中噪声和抖动和信令建模的基础。高速链路的LTI 等效模型如图2 所示。

图2 高速链路及其LTI 等效模型

对于一个线性时不变的链路系统,计算出数据信号经过信道有损传输、串扰及抖动影响后信号的概率密度PDF,就可以计算链路的BER。

接收器判决器接收到的信号可以表示为

其中,ISI(t)表示经过通道后的符号间干扰(Inter Symbol Interference);Xtalk(t)表示来自进攻线的串扰;n(t)表示高斯白噪声,可以表征各种噪声以及抖动源。这些噪声抖动源都在图2 中有标示。

为得到x(t)的PDF 以便推断误码率,必须首先计算出ISI(t)、Xtalk(t)和n(t)的PDF。然后将这些PDF卷积即可得到x(t)的PDF 分布。

根据PDF 的卷积[6],经由信道发送到接收器的信号x(t)的PDF 可以计算如下

式(2)中,AWGN 是加性高斯噪声。值得注意的是,根据卷积性质,对上式可以稍做修改,即可加入串扰、抖动、接收器参考判决电压的不准确性等因素对误码率的影响。

在得到接收器收到的信号的PDF 之后,就可以利用这个PDF 计算BER 了。在建模链路BER 之前,应先对ISI 和串扰的PDF 建模。

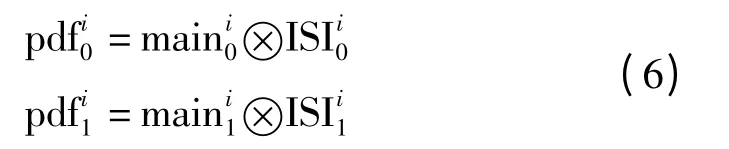

3 ISI 和串扰的PDF 建模

以图3 示例ISI PDF 的构建方法。

图3 ISI 的单个数据采样相位点处光标的划分

基于SBR(Single Bit Response)响应用卷积的方法对符号间干扰ISI PDF 建模。在获得SBR 响应后,按照图3 中虚线对SBR 响应进行划分。图3 中各光标对应的就是单个数据采样相位处的电压采样值。主光标(Cursor)前的光标的是前光标(Pre-cursor)。主光标后的是后光标(Post-cursor)。

下面是单个数据采样相位点的ISI PDF 建模算法,建模采用卷积的方法。主光标之前的第K 位ISI光标的PDF 如下

其中,P0和P1是发送码型0 和码型1 的概率。在实际系统中,可以假定发送器发送0 和1 的概率一样,P0和P1均为0.5。K 表示光标的序号,当K <0 时,表示前光标;K >0 时,表示后光标。由于发送器发送的数据流中的位与位之间不相关,从而可以对各个光标进行卷积运算,将不同光标的PDF 进行卷积,就可以获得ISI 的最终分布。

总的ISI PDF 可以通过将上述所有ISI 每个光标PDF 相卷积得到[7]

其中,i 代表对受害线产生串扰的第几个通道,i 为1 ~n。

主光标的PDF

每根线主光标受ISI 干扰后的PDF

这样,就得到了这个采样相位点的ISI PDF。

通道中不仅存在ISI 的影响,还有通道间串扰CCI。CCI 串扰噪声的PDF 建模方法与ISI PDF 方法相同。串扰的PDF 建模算法也是和ISI PDF 构建方法一样的,受害线上主光标受ISI 和通道间干扰CCI(Co-Channel Interference)干扰后总的PDF

式(7)中,如果是进攻线,则算的是该进攻线上加信号时在受害线上产生的串扰波形;如果是受害线,则算的是在该受害线上加信号,其他线置低电平时受害线上的波形。

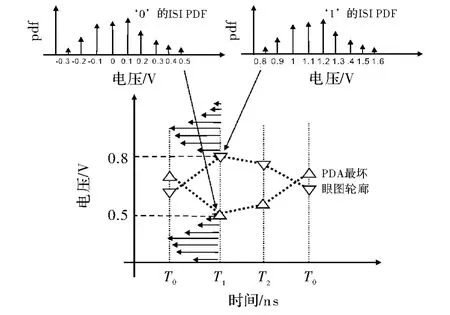

至此,通过上述过程完成了单个采样相位点ISI PDF 和串扰PDF 建模的算法。用图3 中的光标示例,进行PDF 卷积得ISI PDF 分布结果如图4 所示。从此图中箭头所示方向可以很直观地得出此相位时的PDA最坏眼图与ISI PDF 的对应关系。

如图4 中箭头所示:PDA 所求得的最坏‘1’的电平是0.8 V,对应于‘1’的ISI PDF 中值最小并且概率最小的电压;最坏‘0’的电平是0.5 V,对应于‘0’的ISI PDF 中值最大并且概率最小的电压。

在得到ISI PDF 和串扰的PDF 之后,接收器判决器收到信号的PDF 可以通过将串扰和ISI 的PDF 卷积得到[8]。现在可以对这个PDF 根据链路BER 的建模算法计算链路在ISI 和串扰影响下的BER。

图4 固定采样相位时ISI PDF 与PDA 最坏眼图

4 链路BER 建模

在一定的时间内,高速链路系统发送和接收大量的比特。误码率(BER)可以用于表示系统的整体性能

其中,(ts,vs)代表信号样本采集时的参考采样时刻ts和参考采样电压;Nerr表示接收到的错误比特数;N 表示同一时间间隔内传送的总位数。链路的误码率(BER)为采样时刻ts和采样电压vs的二维联合函数,以ts和vs为自变量绘制的图形就是BER 眼图。

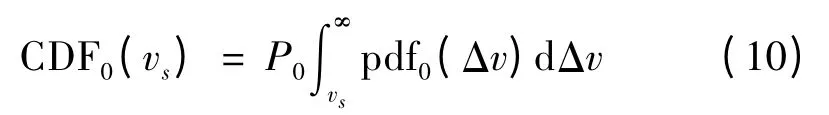

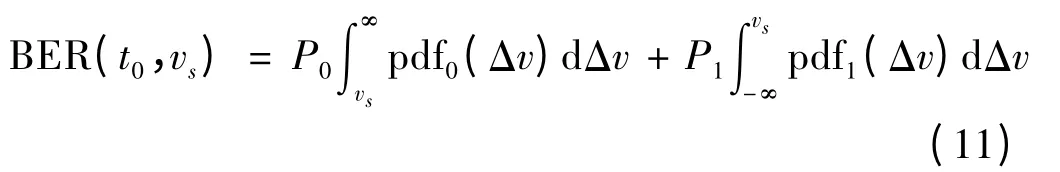

幅度噪声和BER 之间的因果关系与参考采样电压vs密切相关。如图5 所示在指定时刻处的逻辑1 幅度噪声PDF 被定义为pdf1(Δv)。比特1 跳变的概率为P1。对应于逻辑1 电位幅度噪声BER CDF1的表示为

图5 逻辑1 幅度噪声PDF 和以采样电压vs 为自变量的BER CDF 图示关系

以此类推,也可估计出与逻辑0 相应的噪声PDF所对应的BER CDF。在给定时刻处逻辑0 所对应的噪声PDF 为pdf0(Δv),发送器发送比特0 的概率为P0,则相应的BER CDF0如下所示

比特0 和比特1 所对应的噪声对总的BER CDF都有影响。现在得出接收器采样器采用判决时刻t0和参考判决电压vs时的系统误码率如式(11)所示

如图6 所示,对于给定的采样时刻和参考采样电压,对每个采样相位点的ISI+CCI“1”和“0”PDF 分别进行积分并加权即可得出在采样时刻t0采用参考采样电压vs时的BER。

图6 采用判决时刻t0 和参考判决电压vs 时系统的误码率

5 算法流程

基于Intel 的Haswell EP/EP 4S Processor on the Grantley Platform 平台的DDR4 互连的10 线模型[9]对DDR4 内存DQ 信号进行分析。10 线模型如图7所示。

图7 DDR4 10 线分析模型的信号分布图

本算法基于通道的SBR 响应对ISI PDF 进行建模。SBR 响应可以从S 参数获得,也可以利用Hspice仿真得到边沿脉冲响应波形.tr0 文件合成。

采用Hspice 方案获得SBR 响应。首先由Hspice仿真软件得到.tr0 文件,而.tr0 文件中得到的波形是阶跃响应波形。因此,将上升沿和下降沿阶跃响应合成为一个脉冲响应,详情参考文献[10 ~11]。然后根据ISI PDF 建模的方法进行卷积即可得到整个UI 内所有采样相位点的PDF。对CCI 串扰按照同样的方法得到串扰的PDF。耦合线系统的最终PDF 可以通过将串扰和ISI 的PDF 卷积得到。对这个最终的PDF 根据链路的BER 建模方法即可得到BER 眼图。假设接收器为理想采样,不考虑接收器参考采样电压的不准确性和采样判决参考时刻的抖动对误码率的影响。主程序设计框图如图8 所示。

图8 主程序设计框图

6 仿真结果分析

以DDR4 的DQ read 仿真得到的.tr0 文件做示例,频率选择1 333 MHz,仿真出最坏和最好情况结果如图9 所示,UI 是归一化为1 的位长度,无单位量纲。图形窗口中用户可以看到2 种颜色的线:上面的虚线表示最好的“1”,下面的虚线表示最好的“0”。实线是PDA 眼图,也就是只考虑ISI 和CCI 得到的最坏眼图。

图9 最坏情况和最好情况仿真图

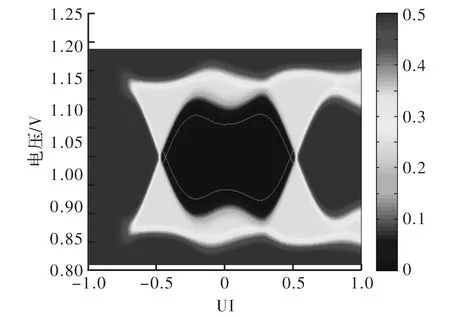

图10 所示是只考虑了ISI 和CCI 得到的BER 眼图。这是当接收端采用不同的判决时刻和参考判决电压时的BER 等高线眼图。图10 右边的色条用颜色的梯度来表示相应的误码率。随着颜色渐变,误码率也在降低。较小的BER 等高线表示接收器的最佳采样区域。

图10 考虑了ISI 和CCI 的3D 误码率眼图

图10 中曲线表示在不考虑接收端和发送端抖动的情况下,仅是由ISI 和串扰得到的最坏眼图,与图9中的PDA 结果相一致。图10 最外面的轮廓表示PDA结果中最坏的上冲与下冲波形。因为在这个例子中假设发送器和接收器是理想的,只考虑了通道的ISI 和CCI,没有考虑接收器参考判决电压的不准确性、发送器抖动和接收器抖动,所以得到的误码率眼图中误码率为零的区域很大。但算法留有接口,只要能得到DDR4 发送端抖动数据和接收端的判决电压和判决时刻的不准确性以及接收端判决时刻的抖动数据并求出其PDF,将这些数据添加进卷积算法,则可以计算出考虑整个链路各种因素作用下的BER 眼图。

7 结束语

本文分析了误码率统计分析算法,研究了链路统计分析算法在DDR4 DQ 数据中的应用,实现了DQ Read 数据误码率眼图的预测,并对眼图结果进行了分析。结果表明,该算法能够快速有效地实现ISI 和串扰对DQ 数据误码率眼图影响的预测,为进一步研究抖动和接收器判决时刻的不准确性等因素对误码率的影响做了准备。

[1] Santanu Chaudhuri,James A McCall,Joe H Salmon.Proposal for BER based specifications for DDR4[C].Austin,TX:Electrical Performance of Electronic Packaging and Systems(EPEPS)IEEE 19th Conference,2010.

[2] Ganesh Balamurugan,Bryan Casper.Modeling and analysis of high-speed I/O links[J].IEEE Transactions on Advanced Packaging,2009,32(2):237-247.

[3] Oh D,Lambrecht F,Chang S,et al.Accurate method for analyzing high-speed I/O system performance[C].Santa Clara,CA:Design Conference,2007.

[4] Bryan K Casper,Matthew Haycock,Randy Mooney.An accurate and efficient analysis method for multi-Gb/s chip-to-chip signaling schemes[C].Honolulu,HI:Symposium on VLSI Circuits Digest of Technical Papers,2002.

[5] Arun Reddy Chada,Wu Songping,Fan Jun,et al.Efficient complex broadside coupled trace modeling and estimation of crosstalk impact using statistical BER analysis for high volume,high performance printed circuit board designs[C].Las Vegas,NV:Electronic Components&Technology Conference,2013.

[6] Li Mike Peng.高速系统设计—抖动、噪声和信号完整性[M].李玉山,潘健,译.北京:电子工业出版社,2009.

[7] Oh Dan,Yuan Xingchao.高速信令-抖动的建模、分析及预算[M].李玉山,初秀琴,路建民,等,译.北京:电子工业出版社,2013.

[8] Wu Hsinho,Masashi Shimanouchi,Li Mike Peng.Highspeed link simulation strategy for meeting ultra long data pattern under low BER requirements[C].Santa Clara,CA:IEC Design Conference,2014.

[9] Intel.Haswell-EP/EP 4S processor DDR4 HSPICE* signal integrity model user's guide.[M].Santa Clara,CA:Intel Conperation,2013.

[10]史晓蓉.基于DDR3 数据的信号完整性分析[D].西安:西安电子科技大学,2013.

[11]彭莎莎.基于高速有损信令系统的最大失真分析算法[J].电子科技,2013,26(3):124-127.