UltraDMA控制器的FPGA实现

赵志勇 ,吕玉祥*,赵晓龙,马维青*

(1.太原理工大学物理与光电工程学院,太原 030024;2.山西省电力公司阳泉供电分公司,山西阳泉0 45000)

目前,在图像、视频和音频处理以及信息家电的实际应用中都需要存储大量的数据,针对以往ATA接口控制器工作时需要CPU的控制访问不符合低成本、高速度的数据传输要求。本研究将通常由主机实现的ATA控制流程提取出来,选取其中的UltraDMA方式,实现一种脱离主机的硬盘访问系统,这样可以有效节省处理器和内存资源,提高数据存储速度[1]。

目前市场上的ATA IP核都是面向IC设计的,不利于在FPGA上集成,因此本研究基于Virtex-II FPGA实现的可独立工作的UltraDMA控制器IP核,对国内逻辑IP核的发展起到了推动作用[2]。

1 系统硬件实现

1.1 总体架构

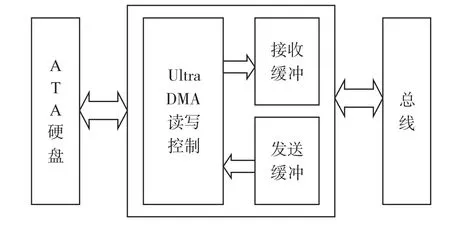

本文所设计的数据传输控制器包括了以下3个模块,分别是UltraDMA读写控制模块、发送缓冲模块以及接收缓冲模块。UltraDMA读写控制模块实现对硬盘寄存器的访问和用户数据的传输,是整个读写控制器中最重要的部分。接收/发送缓冲模块采用双端口RAM技术分别用来缓存用户发送的数据和接收的数据。总体架构如图1所示。

图1 总体架构

1.2 UltraDMA简介

ATA技术是一个关于IDE(Integrated Device Electronics)的技术规范族。在ATA协议中,主机和ATA硬盘互联的物理、电气特性,信号传输以及相关命令的规范都有着明确的定义。ATA的传输模式主要包括以下3种:PIO模式、MDMA模式和Ultra⁃DMA模式。PIO模式是一种通过CPU执行I/O端口指令来进行数据的读写的数据交换模式,传输速率只能达到16.7 Mbyte/s,对处理器资源的占用量极大,目前应用已经较少;MDMA模式在传输速率上和PIO模式同样达到了16.7 Mbyte/s,但是已经可以有效地减少对处理器资源的占用;UltraDMA模式传输速率可以达到133 Mbyte/s,已经能够明显超越PIO模式和MDMA模式,成为了目前主流的硬盘传输方式[3]。

UltraDMA在决定开始数据传输之前会对硬盘寄存器进行访问,通过寄存器的状态对硬盘的当前状态进行一次判断,从而决定是否开始传输数据。主机对硬盘的读写操作是通过向硬盘中的寄存器发送读写等命令来实现的[4]。与UltraDMA相关的寄存器如表1所示。

表1 寄存器组

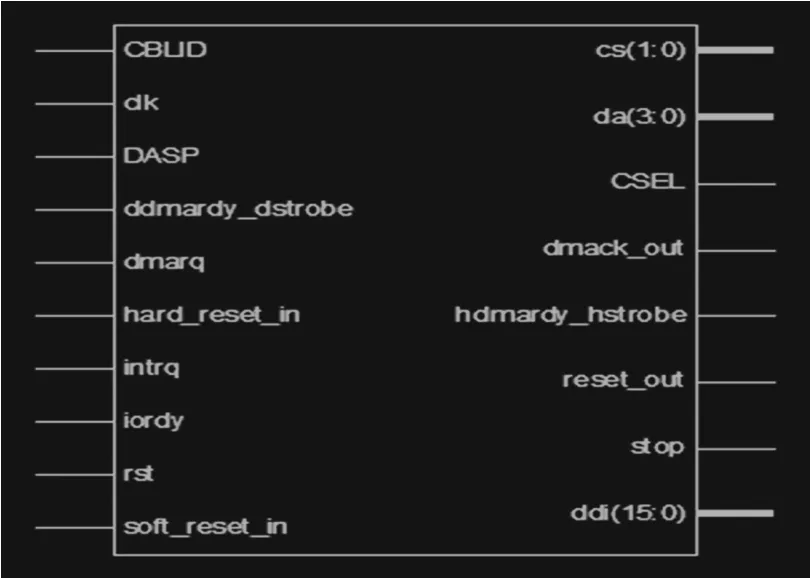

1.3 接口连接设计

ATA接口一共有40个引脚,其中DDI(15:0)为双向数据引脚;CBLID、DASP、ddmardy_dstrobe、dmarq、intrq和iordy控制硬盘数据进入主机,CS(1∶0)、DA(2∶0)、CSEL、dmack-out、hdmardy_hstrobe、reset和stop控制数据进入硬盘,共16个控制线。图2所示为RTL顶层封装图,图2显示了ATA协议中所需要的主要引脚位置,该封装为VHDL代码经ISE综合而成[5]。

图2 接口定义

1.4 UltraDMA控制器读写实现

UltraDMA的执行过程可以分为3个阶段:连接初始化、数据传输和连接终止。UltraDMA数据输入(主机读)的初始化过程:首先硬盘向主机发出DMA的请求,主机会在Tui的时间内将DMACK置1,stop置0,HDMARDY置1,硬盘主机准备接受数据,等待第1个DSTROBE的跳变,第1组数据通过数据总线(dd(15∶0))传输给主机,初始化结束。

当所有数据传输结束时,进入连接终止阶段。主机和硬盘均可终止连接,硬盘端启动终止连接程序:首先硬盘端使DMA请求信号无效;主机端检测到DMARQ无效后,在Tli时间内置高STOP信号、复位HDMARDY信号;硬盘在收到STOP跳变后的Tli时间内置高DSTROBE信号,表明此后没有数据等待传输;此后主机端产生DMACK-跳变沿,同时将CRC校验传入数据总线,硬盘收到校验结果与自己的校验值进行比较,以此判断传输是否错误[6]。

用VHDL实现UltraDMA控制器时,主要采用状态机来控制整个读/写流程,定义的状态转移图如图3所示,在每个状态执行固定操作,这样思路清晰易于实现。

图3 UltraDMA状态转移图

(1)st_idle 空闲状态;

(2)st_readst1 读状态寄存器;查看是否硬盘空闲来决定是否继续访问硬盘;

(3)st_selectdev 设备选择状态;写设备/磁头寄存器对将要访问的设备进行选择;

(4)st_readst2 读状态寄存器;读取硬盘状态,空闲进入下一状态,否则保持;

(5)st_setfeature 设置接口特性;01000写入扇区寄存器高5位,设置接口为UltraDMA模式,010写入低3位,选择模式2;

(6)st_readst3 读状态寄存器;

(7)st_weparameter 写命令参数;扇区数寄存器存储本次需要传输数据所占扇区数;

(8)st_wec 写命令;C8H为读操作,CAH为写操作;

(9)st_initiate UltraDMA初始化;

(10)st_transdata 数据传输状态;

(11)st_crc 终止连接和发送CRC校验值;

(12)st_readst4 读状态寄存器;

(13)St_err状态 错误状态。当有错误发生时进入此状态。

2 系统验证

本文选择的编译环境为ISE10.1,编程语言选择使用VHDL,通过编译、综合和布局布线,最后下载到开发板上进行了验证。图4~图7为在UltraDMA控制器读写硬盘时用Chipscope软件抓取的数据情况。

本文首先进行了UltraDMA读(data_in)硬盘的验证。硬盘读取数据的过程可以总结为如下过程:数据读初始化、数据读取、数据读取终止。UltraD⁃MA硬盘读取的初始化过程如图4所示,硬盘发出请求,通过DMACK,stop和hdmardy的响应,主机做好接收数据的准备。随着第一组16位数据的传输,DSTROBE引脚发生一次跳变,结束数据传输初始化过程。图5显示了数据传输终止过程的时序图,引导区标记数据为AA55,CRC校验值为F445。在DMACK发生跳变时,该校验值传给硬盘,由此判断数据传输是否正确[7]。

图4 UltraDMA data_in初始化

图5 UltraDMA data_in终止

图6 UltraDMA data_out初始化

图7 UltraDMA data_out终止

本文同样验证了UltraDMA写(data_out)硬盘的功能。设定向硬盘写入0 000 h-00 FFh共256个512 byte(一个扇区)数据,此数据预先存入发送缓冲区。图6为data_out初始化阶段,硬盘与控制器“握手”完成后,由控制器产生第1个HSTROBE跳变,同时把第一个数据(0 000 h)传入数据总线,此后数据按顺序传输[8]。图7为传输结束阶段,硬盘首先使ddmardy(低电平有效)和dmarq无效,主控制器端则产生stop信号,并在最后一个HSTROBE跳变沿传输最后两字节数据(00 FFh)。用户数据传输完后在DMACK跳变沿将CRC校验值(8 985 h)传给硬盘。

整个验证过程在无CPU环境下进行,控制器的读/写由各自使能信号控制完成,因此该控制器可以作为一个独立的模块应用于系统中[9]。

3 总结

本文采用FPGA实现符合ATA标准的UltraD⁃MA读写控制器,在无CPU的情况下,能够独立完成对硬盘的读写操作。经测试,本控制器与希捷、迈拓、三星等公司的多种型号硬盘连接均能正常工作。若对控制器稍加改动,如配合相应文件系统,如FAT32或者EXT,将可用于嵌入式设备中,实现海量数据存储,使系统具有更好的实用性。

[1]于明喆,李晖,申婷.Nios系统基础上的UltraDMA数据传输模式[J].单片机与嵌入式系统应用,2006(2):32-35.

[2]孙伟,郭宝龙,武晓玥.等.DSP视频存储关键技术研究及实现[J].电视技术,2009,33(6):30-32.

[3]Information Tichnology-AT Attachment with Packet Interface-7(ATA/ATAPI-7)(S):2003.

[4]胡伟,慕德俊,刘航,等.嵌入式ATA主机控制器IP核设计[J].计算机测量与控制,2009,17(1):192-194.

[5]于祥凤,刘学斌,胡炳樑,等.UDMA突发数据传输中CRC的应用[J].电子器件,2008,31(5):10-31.

[6]Bo Li,Yu Peng,Liu Da tong.A High Speed DMA Transaction Method for PCI Express Devices[J].Journal Of Electronic Science And Technology Of China,2009,7(4):380-384.

[7]于磊,孟令军,张园,等.基于FPGA的PCI-Express接口卡设计[J].计算机测量与控制,2014,22(1):152-154.

[8]杨立成,刘丹峰,史继辉.基于DMA的大批量数据快速传输模块设计[J].电子科技,2012,25(12):49-51.

[9]何琼,陈铁,程鑫.DMA在高速实时数据采集系统中的应用[J].仪表技术与传感器,2012(3):49-52.

赵志勇(1988-),男,汉族,山西省吕梁市人,硕士研究生,研究方向为电子设备的研发,zhaozhiyong217@163.com;

吕玉祥(1964-),男,汉族,山西省太原市人,太原理工大学教授,主要研究领域为光电子技术及电力电子设备的研究,lyx823@126.com。