高速PCB设计中的差分等长处理及仿真验证*

杨章平

(中国电子科技集团公司第三十研究所,四川 成都 610041)

高速PCB设计中的差分等长处理及仿真验证*

杨章平

(中国电子科技集团公司第三十研究所,四川 成都 610041)

在进行高速PCB(Printed Circuit Board)设计时,通常需要对差分信号线的相对时延进行控制,以满足信号完整性要求,因此,如何处理差分线的等长,是需要解决的一个问题。通过分析不同相对时延对差分及共模信号波形的影响,得出相对时延对信号的影响及与信号的上升/下降时间有关,并给出了确定信号上升/下降时间的方法,最后对DSP(Digital Signal Processor)和DDR3(Double Data Rate Tree)内存之间的信号进行了仿真分析,验证了前述分析结果的正确性。

差分信号;共模信号;相对时延;上升/下降时间;仿真

0 引 言

差分线对是指一对存在耦合的传输线。差分信号的传输是利用两个输出驱动来驱动差分线对,一根携带信号,另一根携带它的互补信号。实际需要的就是差分线对间的电压差,它携带着要传输的信息[1]。差分发送器两个单端发送的信号大小相同,相位相反,如果两个信号同时到达接收端,那么信号将得到正确的接收。但是,信号在传输线上传输时,会产生时延,如果某一单端信号的传输距离较长,其时延也会较大,两个信号之间就存在相对时延,这相当于其中一个信号发生了相移,接收端接收到的差分信号就会在一定程度上产生失真。如果失真幅度过大,可能出现信号在接收端无法正常接收等问题,使得电路功能无法正常实现。因此,要尽量减小差分对的两个单端信号之间的相对时延。

PCB Layout工程师在进行PCB设计时,由于元器件的密集度和布局布线的复杂性,走线中不可避免的会出现拐角,拐角的存在使得差分信号线两线长度出现不一致,差分信号对之间产生相位差[2],因此通常需要对差分线对进行等长处理。可是相对时延需要控制在多大范围内,经常会使我们犯难,如果相对时延过大,信号可能会发生较大的失真,信号完整性得不到保障,相对时延过小,处理起来有时候比较麻烦,特别是当差分对比较多时,过于严格的等长控制会消耗不少的精力,而且由于印制板加工工艺的限制,过于精细的设计往往难以达到。因此,在实际设计中,只需要将等长控制在适度范围就可以了。

本文以差分理论及信号完整性理论为基础,采用作函数图的方式,阐述了差分对间的相对时延对差分信号的影响,提出了使用信号时钟周期或频率来估计差分等长控制大小的简单方法,并通过仿真验证,说明了该方法的可行性。

1 相对时延对信号的影响

差分信号线中传输的信号包含了信号的差模分量和信号的共模分量。

差分信号的大小为两个信号之差,即:

Vdiff=V1-V2

(1)

共模信号的大小为两个信号和的一半,即:

(2)

因而,单根信号线的电压变化,必然会对差分信号和共模信号同时产生影响。下面,我们通过使用graph软件作数学函数图,分别研究信号相对时延对差分和共模信号的影响。为了便于研究,将信号近似为上升时间和下降时间相等的梯形波形来进行分析。

1.1 对差分信号的影响

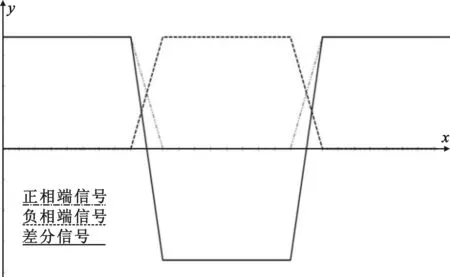

差分线对的正相端信号、负相端信号及差分信号如图1所示(图1-3中,y轴表示信号电压,x轴表示时间),其中实线为差分信号波形。

图1 差分信号波形

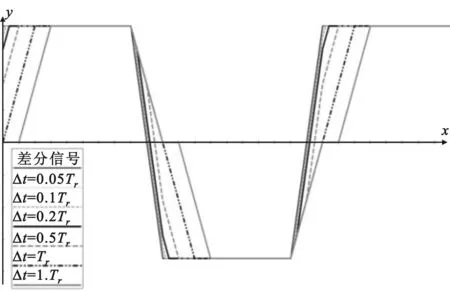

如果正相端信号相对于负相端信号有一个相移,正相端信号和负相端信号之差在上升或下降沿处将会发生改变,其变化随着相移大小的不同而不同。使用Tr来表示上升或下降时间二者中最小的一个值。图2给出了不同相移时的差分信号波形。从图中可以看到,在相移小于Tr的0.2倍时,信号失真较小,随着相移的增大,差分波形的失真逐渐增大,当相移超过Tr时,波形出现了非单调的区域。此处的非单调区域是一条直线,但是对于实际信号,由于存在反射等因素,非单调区域可能出现较大的起伏,形成干扰脉冲,造成信号的误触发,是应该避免的。此外,从图中可以看出,差分波形的上升沿随着相移的增大逐渐变缓,对于数据信号,可能造成建立时间不足,而对于时钟信号而言,可能造成保持时间不够等时序问题。

图2 差分信号波形的变化

1.2 对共模信号的影响

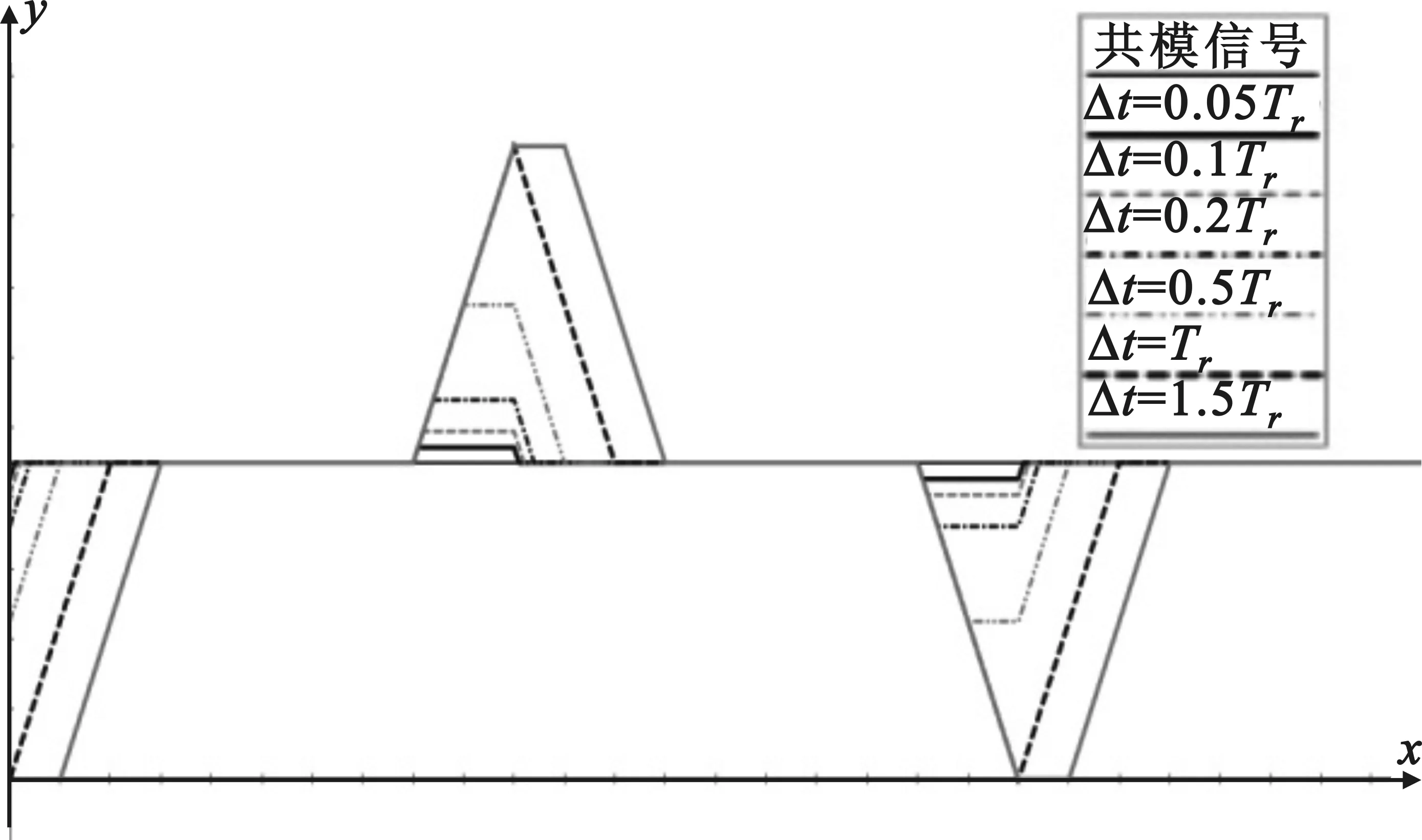

单端信号的相移不仅会影响差分波形,同样,也会使得共模信号的波形产生改变。当正相端信号产生相移时,共模信号会出现波动,图3给出了不同正相端相移时,共模信号的波形图。从图中可以看到,共模信号的波动幅度跟相移大小有关。当相移大小分别为0.05Tr、0.1Tr、0.2Tr和0.5Tr时,共模信号的波动幅度约为原幅值的5%、10%、20%和50%。当相移增大到Tr及以上时,波动幅度约为100%,达到最大波动幅度。共模信号的变化可能会引起EMI(Electro Magnetic Interference)问题,而且由于许多情况下,共模信号并没有被端接,会在接收端形成反射,造成信号振铃,因而,应尽量减小共模信号的波动。

图3 共模信号波形的变化

综上所述,差分对之间相对时延过大可能造成信号的误触发、信号反射、EMI以及时序问题。而相对时延对信号的影响程度取决于其相对于信号Tr的比例因子。取这个比例因子为0.05,从图2可以看出,此时差分信号的失真度几乎可以忽略不计;而对于共模信号,取0.05的比例因子,可以使共模信号电压波动控制在约5%电压幅值,这样,即使在发生全反射的情况下,叠加在信号线上的反射电压也只有约原幅值的10%,通常这是一个可以接受的值。因而,在进行高速PCB设计时,布线约束规则中差分信号线的相对时延可以设置为0.05Tr,这样足以满足信号完整性的要求。

2 相对时延范围的确定

通过以上分析可以知道,确定差分等长范围,即确定差分对间相对时延大小,关键在于确定差分信号的上升/下降时间中最小的值Tr。输出上升时间和下降时间,在某种意义上,是输出阻抗和电容的组合[3],因而其未接负载时的上升/下降时间是其固有上升/下降时间。

可以按以下三种方法来得到Tr的值。第一种方法是直接从器件手册上获取上升或下降时间。但是很多时候,这个参数并没有给出。第二种方法是从器件IBIS(Input/Output Buffer Informational Specification)模型中Ramp关键字下获取Tr的值。Ramp关键字下的上升/下降时间参数通常是输出端口接50欧姆电阻测得,为20%到80%最终电压值的时间,且由于此处的参数没有考虑封装的影响,因而我们使用这个上升/下降时间作为Tr的值是比较严格的。 最后一种是根据输出信号的最小时钟周期或最大时钟频率来进行估算。由于在大多数高速数字系统中,分配的上升边大约为时钟周期的10%[4],因此,知道了驱动端输出的最小时钟周期Tclk,就可以大概估算Tr的大小。即有:

Tr=Tclk×10%

(3)

使用时钟周期进行估算的结果通常也是比较严格的,因为器件的封装寄生参数或者负载会使晶体管固有的上升/下降时间大幅减缓。

实际工作中,很多时候,电路设计人员并没有向PCB Layout工程师提供Tr的信息,PCB Layout工程师从电路设计人员那里得到的只有进行差分等长控制的模糊要求。因而如何确定差分等长控制大小就显得很重要,第三种方法无疑为PCB Layout工程师提供了一种简单的解决方案:只需获得信号线上的最高时钟频率就可以了。而最高时钟频率是设计人员心里最有数的设计参数,且通常在PCB设计之初就会提供给PCB Layout工程师。

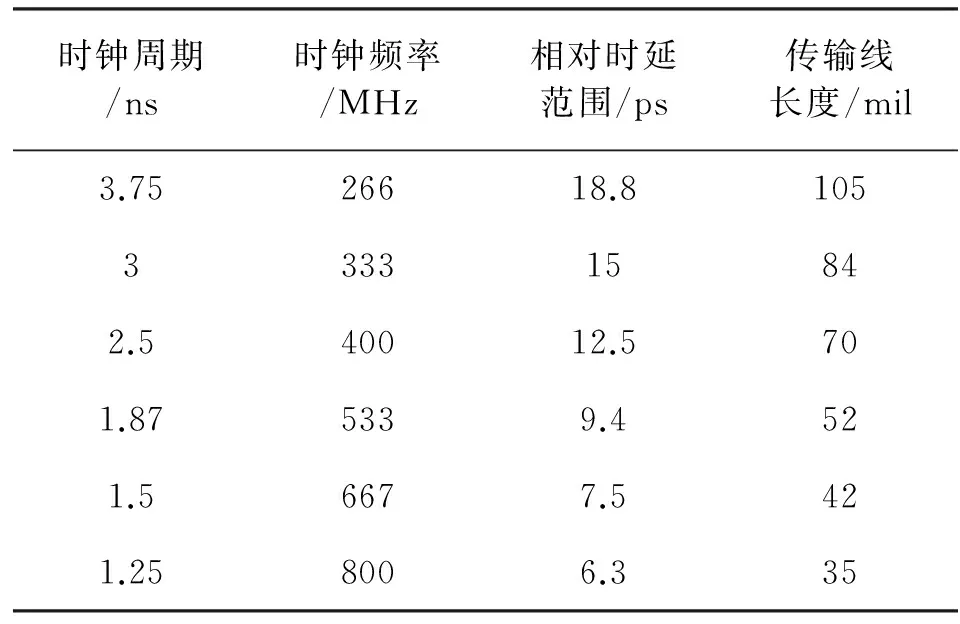

通过使用最后一种方法进行估算,给出常见时钟周期下差分对间相对时延(0.05Tr)控制范围的参考值,如表1所示。

表1 常见时钟周期下差分等长控制范围

3 仿真验证

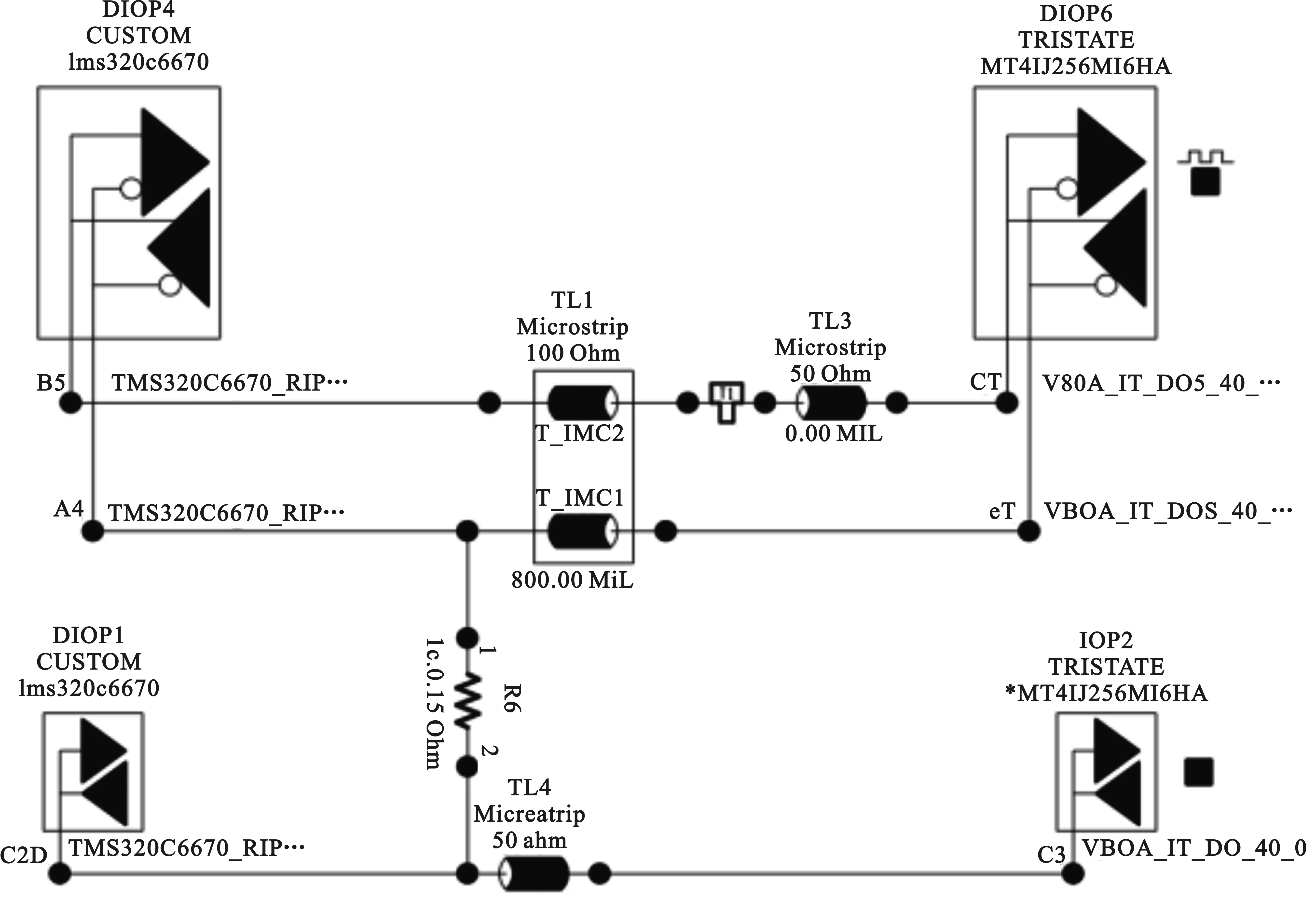

以TMS320与MT41J256M16之间的DQS(Data Strobe)差分信号为例,使用Cadence仿真软件仿真内存控制芯片向DRR3内存发送DQS信号的情形,并分析其对数据信号建立保持时间的影响,来对前面的分析进行验证。仿真电路如图4所示,其中输出引脚的参考电压为1.5 V,内存控制芯片与内存芯片之间直连,采用ODT(On-Die Termination)模式,传输线长800 mil,差分阻抗100欧姆,仿真时钟周期800 MHz。在DQS正相端串接一段50欧姆的传输线来模拟差分对的不等长现象。差分等长时,50欧姆单端传输线长为0 mil。

图4 仿真电路

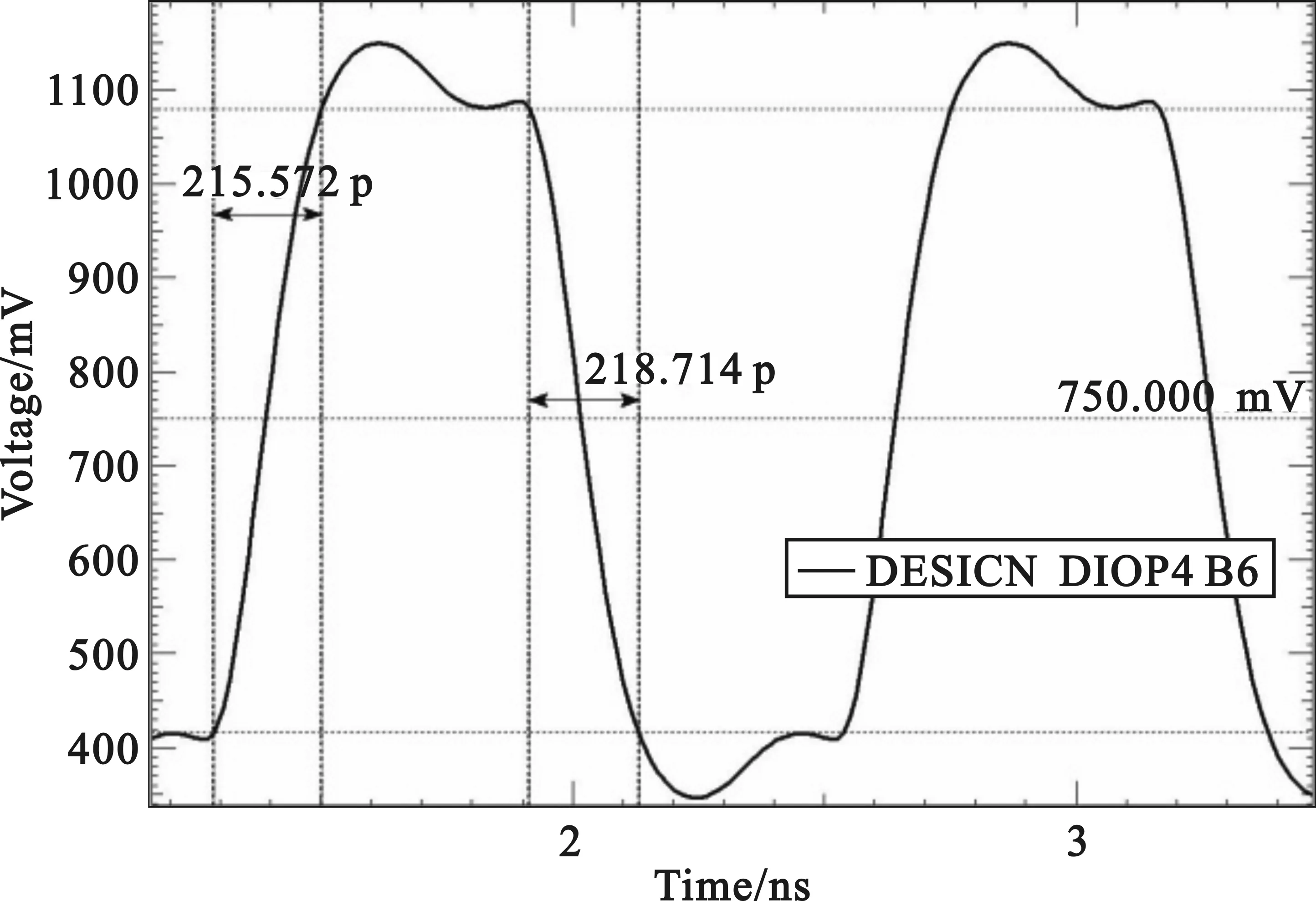

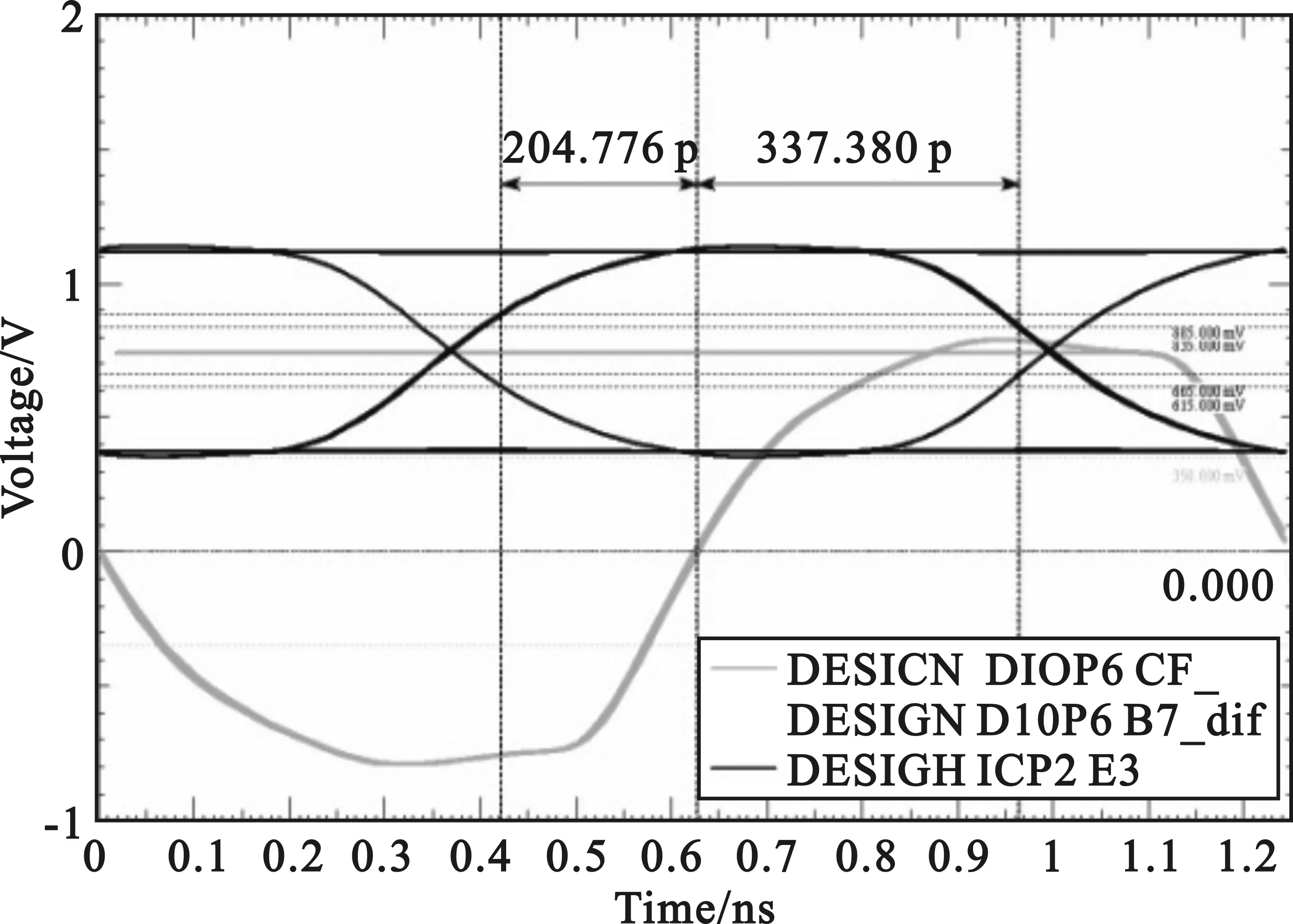

对差分等长时的电路进行仿真。图5所示为差分信号正相端的输出信号,测得其上升时间约为216 ps,下降时间约为219 ps,因而最小上升/下降时间Tr为216 ps。图6所示为仿真得到的数据信号DQ和选通信号DQS的眼图,测量得到建立时间约为205 ps,保持时间约为337 ps。根据仿真得到的DQS和DQ信号的翻转速率,查找数据手册可知,接收端对数据信号最小建立时间的要求为85 ps,最小保持时间为95 ps,因而,最小建立时间裕量为120 ps,保持时间裕量为242 ps。

图5 输出信号上升/下降时间

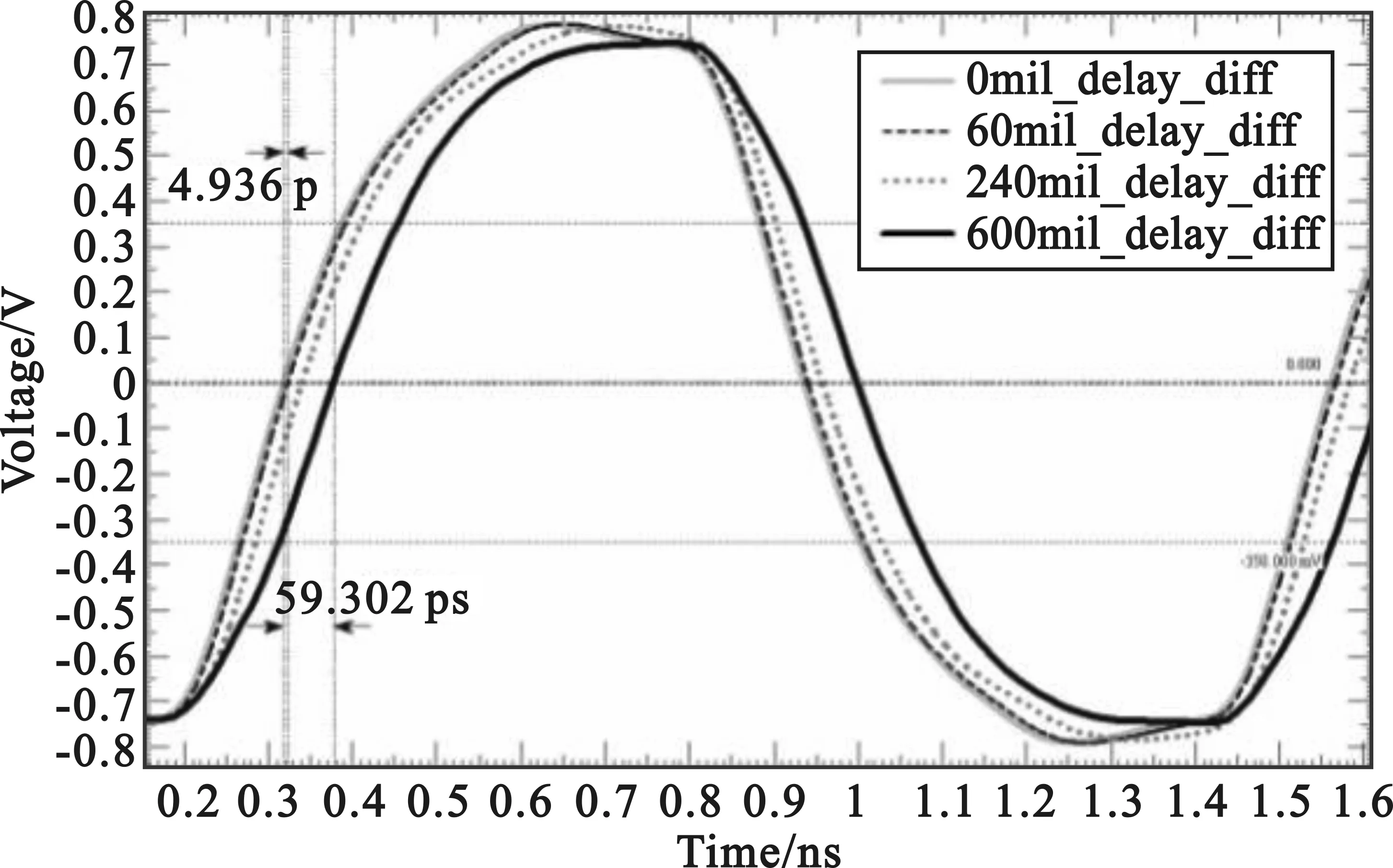

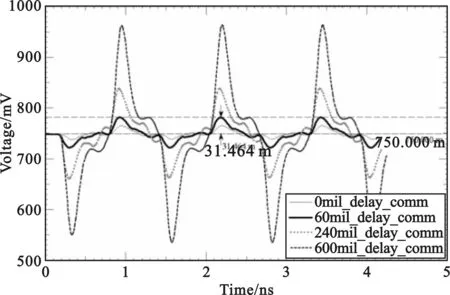

再分别考虑正相端存在0.05Tr相移、0.2Tr相移和0.5Tr相移时的情况。将单端传输线长度分别设置为60 mil、240 mil和600 mil来对电路进行仿真。四次仿真得到的差分信号波形和共模信号波形如图7和图8所示。

图6 DQ和DQS信号眼图

从图7可以看出,当差分线存在0.05Tr和0.2Tr的相对时延时,失真度较小。特别是当相对时延为0.05Tr时,差分信号相对于无相对时延的差分信号波形只有约5 ps的偏移,这个偏移使得数据信号的建立时间裕量增加了约5 ps,保持裕量时间减少了约5 ps。虽然保持时间裕量有所减小,但对于242 ps的保持时间裕量来说,这个偏移量是很小的,对于时序的影响可以忽略不计。而对于相对时延为0.5Tr时的情形,此时DQS信号波形的偏移量达到了约60 ps,虽然这个偏移量仍然在裕量范围内,但还是应该引起足够的重视。

图7 不同相对时延的差分信号波形

再来看图8所示的共模信号波形,其随着相移的增大,波形逐渐呈现出明显的周期性波动,并且波动幅度越来越大。分别对相对时延为0.05Tr、0.2Tr以及0.5Tr时,共模信号的峰峰值进行测量,得到测量结果分别约为61 mV、176 mV、430 mV,最大值是最小值的7倍。其最大波波动幅度分别约为4.3%、12%和29%。

由此可见,仿真结果与前面使用数学函数图分析得到的结果是比较符合的,当差分线对间的相对时延小于0.05Tr时,其对信号的影响已经很小了。

图8 不同相对时延的共模信号波形

再使用输出端输出信号的最小时钟周期对相对时延控制范围进行估算。从器件手册中查知,器件的最小时钟周期为1.25 ns,即时钟频率为800 MHz。由表1可知,相对时延应控制在6.3 ps以内,即传输线长度约35 mil。显然,这个值比仿真得到的0.05Tr(60 mil)的相对时延控制范围小得多。由此可见,估算得到的相对时延控制范围是比较保守的,其要比通过仿真得到结果要严格。

4 结 语

本文分析了上升/下降时间对差分信号的影响,得出了高速PCB设计中,差分等长的控制范围应在0.05Tr以内,并提出了使用信号最小时钟周期或最高频率来确定信号Tr的方法。使用该方法确定差分等长的控制范围,简单而实用,可以大大提高PCB Layout工程师的工作效率。需要注意的是,使用该方法来确定差分等长控制范围,主要适用于信号频率在100MHz到 5.5GHz时的高速PCB设计。这是因为频率较低时,差分等长没有那么严格的要求,只需进行适度的控制即可;而频率较高时,计算得到的结果将接近工艺极限,计算也将失去意义。

[1] 邱剑. 差分线对的PCB设计要点[J]. 通信技术,2010,43(06) :221-223. QIU Jian. Main Point on PCB Design of Differential Signal[J].Communications Technology 2010,43(06) :221-223.

[2] 侯莹莹,胥佳. 线形结构对差分传输线信号完整性的影响[J]. 电子测试,2009(2). HOU Ying-ying, Xu Jia.Impact of Different Shapes of Differential Transmission Lines on Signal Integrity[J].Electronic Test,2009(2).

[3] Geoff Lawday,David Ireland,Greg Edlund. 阎照文译.信号完整性指南——实时测试、测量与设计仿真[M].北京:电子工业出版社,2010:43. Geoff Lawday,David Ireland,Greg Edlund. YAN Zhao-wen Translated.A Signal Integrity Engineer’s Companion Real-time Test and Measurement and Design Simulation[M]. Beijin:Electronic Industry Press,2010:43.

[4] Eric Bogatin.李玉山译.信号完整性分析[M].北京:电子工业出版社,2005:12. Eric Bogatin.LI Yu-shan translated.Signal Integrity Analysis[M].Beijin:Electronic Industry Press,2005:12.

Isometric Processing of Differential Lines and Simulation Verification in High-Speed PCB Design

YANG Zhang-ping

(No.30 Institute of CETC,Chengdu Sichuan 610041,China)

Generally in high speed PCB design, relative time delay of between the two transmission lines of differential signal needs to be controlled, so as to maintain the signal integrity. Thus, how to deal with the difference of the two lines is a problem that needs to be solved. Based on the analysis of different relative time delays affecting the differential and common-mode signal waves, a conclusion that the above effect is associated with the signal rise/fall time is drawn, and method to determine the rise/fall time also given. Finally, simulation of the signals of between DSP(Digital Signal Processor)and DDR3 DDR3(Double Data Rate Tree) memory indicates the correctness of above analysis result.

differential signal; common-mode signal; relative time delay;rise/fall time;simulation

10.3969/j.issn.1002-0802.2015.05.024

2014-12-05;

2015-04-09 Received date:2014-12-05;Revised date:2015-04-09

文献标志码:A 文章编号:1002-0802(2015)05-0626-05

杨章平(1980—),男,硕士,工程师,主要研究方向为SI/PI。