综合化航电设备中数字交换网络系统应用需求与实现

朱 宇

(中国西南电子技术研究所 航空事业部,四川 成都 610036)

0 引言

随着电子技术的发展,航空电子设备综合化、集成化的程度越来越高。高度综合化航空电子设备与传统的分立式航空电子设备不同,它将机载传感器信道按照处理频段进行划分,对相同频段上的信道资源采用通用化模块设计[1]。功能软件资源亦采用模块化设计,驻留在基带信号处理模块上。系统通过对信道软硬件资源进行配置及重构实现各项功能线程[2]。

信道资源通用化模块设计,必然需要传感器模拟信号数字化不断前移,信号采样频率越来越高,导致射频信道模块与数字处理模块之间传输的数字信号速率越来越高,达到几百 Mb/s,甚至超过 1 Gb/s,因此传统的机载总线技术,如1553B、VME等已远不能满足高速数字信号传输的要求。

为满足综合化航电系统资源可配置与可重构的应用需求,多个通用射频信道模块与多个数字信号处理模块之间需要完成数据路由和数据交换。数字交换网络系统实现了通用射频信道模块与数字信号处理模块之间的高速数据传输与数据交换功能。

1 综合化航电系统对数字交换网络需求

1.1 综合化航电系统架构

综合化航电系统是一个基于软件无线电技术的高度综合化系统。系统包含通信、导航、识别类别数十个传感器功能。当系统需要某项传感器功能时,与此功能相关的软、硬件资源在系统统一调度下进行组合,构建成与此功能相关的从天线、射频信道、信号处理、数据处理、接口处理的完整链路处理通道,同时通过加载运行相关的功能软件,构成一个功能线程,完成该功能项的接收/发射和信号/信息处理[3]。

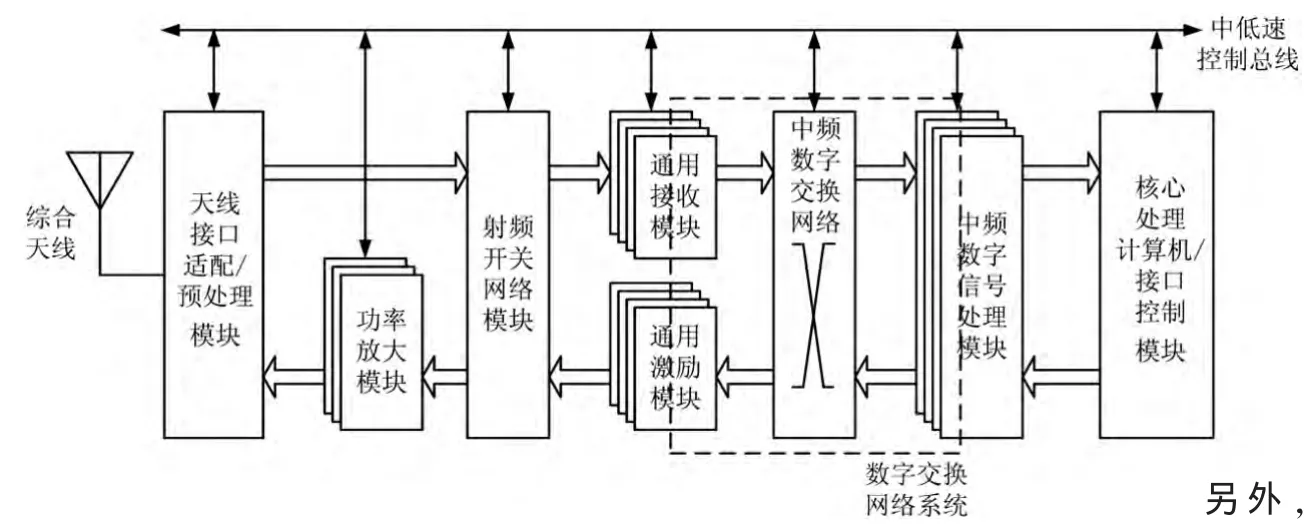

综合化航电系统模型如图1所示。

工作原理:传感器信号接收时,射频信号由综合天线接收,经射频开关网络路由后送入通用接收模块进行下变频、放大、滤波等处理,再经过A/D采样数字化后成为标准数字中频信号,送入中频数字交换网络模块,经路由后送至中频信号处理模块进行解调处理,最后解调完成的基带功能数据送入核心处理计算机/接口控制模块进行处理,组成下行链路。

图1 机载设备综合化射频传感器系统模型

传感器信号的发送为接收过程的逆过程,核心处理计算机/接口控制模块输出的基带功能数据送入中频信号处理模块进行调制,基带调制数据经过中频数字交换网络模块路由后,送入通用激励模块中进行D/A变换、上变频、激励后成为射频信号,将射频信号经射频开关网络路由后送通用功率放大模块进行功率放大,将功率放大后的射频信号经天线接口适配模块送相应天线发射,组成上行链路。

1.2 综合化航电系统对资源可配置及功能重构的需求

一个典型的飞机作战任务阶段可以分为:滑行/起飞、战术导航、作战、归航、进场/着陆。根据飞机当前任务阶段,所需要的传感器功能不尽相同[4]。例如:飞行全过程都需要超短波话音通信功能,精密测距功能只在进场着陆时使用,航管应答功能在除作战的所有阶段均需要使用,而敌我识别功能只有在作战阶段使用,飞机处于不同的飞行阶段就会触发系统对硬件资源进行配置和重构,组合出所需的传感器功能。

系统每一个通用信号处理模块中,都驻留了该信号处理通道重构所需的所有功能软件,一旦飞行阶段发生变化,通用信号处理模块就会根据重构策略重新加载功能软件,与其他信道资源共同实现新功能。例如,作战模式时,系统占用航管功能处理资源,加载敌我识别功能软件,实现敌我识别功能;非作战模式时,系统重新加载航管功能软件,实现航管功能。

另外,不同的传感器功能优先级不同。当优先级高的功能链路发生故障被系统监测到,则优先级高的功能会占用优先级低的功能的资源,系统功能重构。例如,飞行全过程都需要超短波话音通信功能,并且超短波话音通信功能优先级最高,一旦超短波话音功能发生故障,则超短波话音功能会抢占其他超短波链路资源实现超短波话音功能。

1.3 数字交换网络系统在综合化航电设备中的应用

由于综合化航电设备对系统功能重构的需求,通用接收模块A/D采样后的中频数据可能会送到不同的通用信号处理模块进行处理,通用信号处理模块发送的中频数据可能会送到不同的通用激励模块进行处理。这样在通用射频信道模块(通用激励、通用接收)与通用数字信号处理模块之间就需要数字交换网络系统来实现通用射频信道模块数据信号与信号处理模块数据信号的动态路由和高速数据全交换功能。

2 数字交换网络系统实现

2.1 数字交换网络系统功能框图

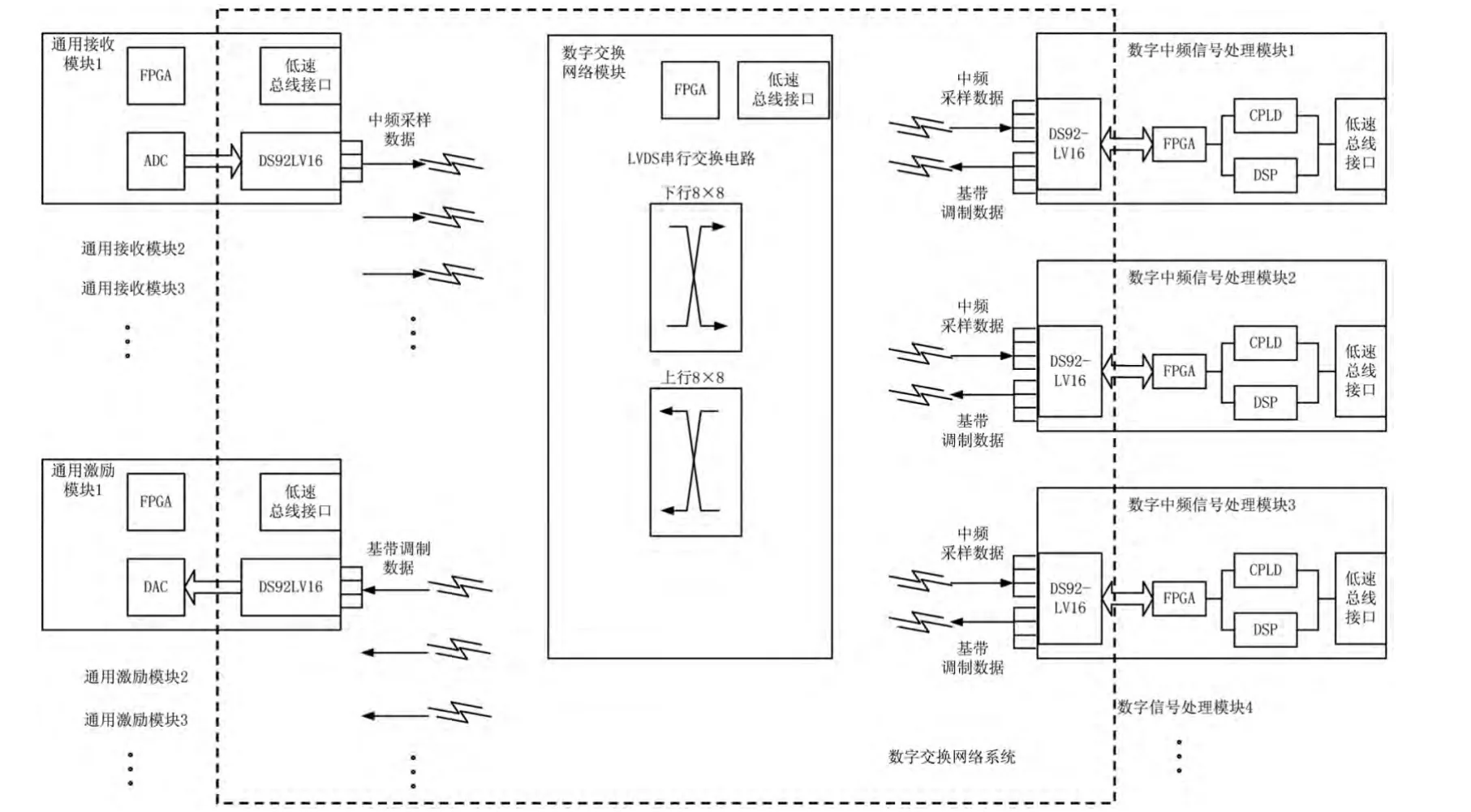

通用接收模块A/D采样后并串转换为串行LVDS信号部分,通用激励模块D/A变换前LVDS信号串并转换部分、中频数字交换网络模块及中频数字信号模块LVDS信号接口部分共同构成数字交换网络系统,如图2所示。

图2 数字交换网络系统框图

数字交换网络模块完成下行8×8(中频到信号处理)和上行 8×8(信号处理到中频)高速LVDS信号的全交换功能。

2.2 数字交换网络模块实现

数字交换网络模块主要由FPGA功能单元、CAN总线接口单元、下行8×8交换矩阵和上行8×8交换矩阵组成。FPGA功能单元采用Xilinx公司生产的Spartan-3系列FPGA XC3SD3400A-4CS484LI,其中集成了功能强大的32位微处理器软核MicroBlaze,在其上运行数字交换网络模块的应用程序,MicroBlaze处理器通过OPB总线挂接了商用成熟的SJA1000 IP Core和交换矩阵控制IP Core,SJA1000 IP Core用于实现CAN总线协议处理,交换矩阵控制IP Core实现对下行8×8交换矩阵和上行8×8交换矩阵的控制。CAN总线接口单元实现数字交换网络模块与系统CAN总线接口的功能。FPGA通过接收系统控制命令,输出控制信号实现对数字交换网络路由的控制。

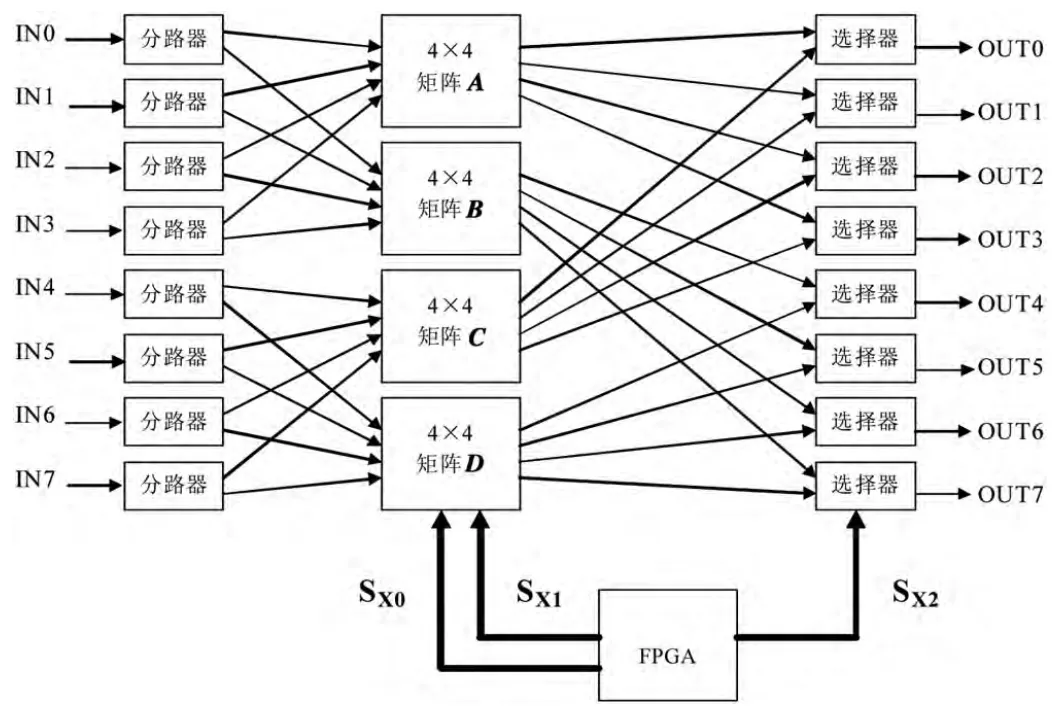

数字交换网络模块的核心是8×8交换矩阵电路,下行矩阵与上行矩阵设计相同,方向相反。交换矩阵采用专用集成电路实现。目前支持LVDS电平的交换矩阵专用集成电路芯片最大规模为 4×4,方案采用4片4×4的LVDS交换芯片、8片分路器和 8片选择器来搭建 8×8的下行交换矩阵。分路器(Splitters)采用MAXIM公司的MAX9174EUB,最高数据率达 800 Mb/s。4×4的交换矩阵(Crosspoint Switch)采用 TI公司的 SN65LVDT125A实现,最高数据速率达1.5 Gb/s。选择器(Multiplexers)采用MAXIM公司的MAX9176EUB实现,最高数据率达800 Mb/s。

如图 3,每个输入信号通过一个1分2的分路器将输入信号同时送入2个 4×4的交换矩阵中,其中 IN(0~3)被送入矩阵 A和矩阵 B,IN(4~7)被送入矩阵 C和矩阵D。矩阵A的4个输出端口和矩阵C的4个输出端口一一对应并接在一起得到输出端口OUT(0..3),矩阵B的4个输出端口和矩阵D的4个输出端口一一对应并接在一起得到输出端口OUT(4~7)。对于输出信号并联的控制采用一个2选1的选择器实现,通过对输出端口使能信号的控制,保证在任一时刻并接输出的信号只有一个处于输出状态。

图3 8×8交换矩阵网络原理框图

FPGA 产生通道选择信号 SX2、SX1和 SX0(X=0,1,…,7)。通过这8组共24根选择信号线,在选择信号与通道输出组合之间形成一一对应的关系。整个模块类似于8个8选 1的数据选择器,对于任意的一路输入 I(x),通过对通道选择信号的设置,使其对应于任意一路输出O(x),完成数据全交换的功能。

2.3 数字交换网络技术可行性分析

(1)LVDS传输技术适用于系统级背板传输

高速并行数据总线之间的串扰、布线等长及背板走线规模等问题[5],使得通用信号处理模块与通用射频信道模块之间无法采用并行传输方式。另外试验表明,LVDS串行传输电缆长度达到5 m,传输速度仍超过1 Gb/s[6],满足系统720 Mb/s的速率要求。因此LVDS串行传输技术在传输方式和传输速率上满足系统设计需求。

(2)强实时传输与交换

数字交换网络传输的中频信号数据流需要数据传输的强实时性以及延迟确定性,否则将会导致功能信号的失真。LVDS传输技术将中频数字信号直接串并转换进行传输,无协议封装和解析的开销,满足系统强实时传输及传输延迟确定的要求,并且,传输通道的切换依靠交换节点芯片自身电气特性,切换延迟小于10 ns,远远高于其他网络交换技术。

(3)高性能与低成本

LVDS传输技术1 Gb/s的传输速率远远高于RS-422/485、ARINC-429等串行传输方式规定的传输速率[7],同时,与RapidIO、FC等高性能传输方式相比,LVDS传输技术在体积、功耗和成本等方面开销要小得多。

3 测试验证

3.1 数据传输功能及误码率测试

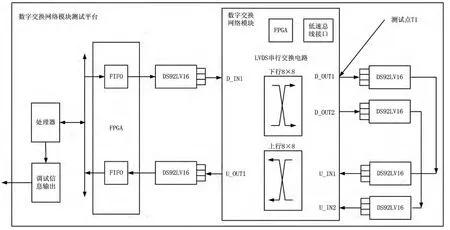

在系统上按照图4搭建测试验证环境,使用测试平台上的处理器构造16位周期数据,并存入FPGA发送FIFO中,FPGA以50 MHz的频率将FIFO中的数据向DS92LV16发送,并串转换后送入数字交换网络模块D_IN1,默认输出通道为D_OUT1,在测试平台上进行回还后输入U_IN1,默认输出为U_OUT1,通过串并转换后送入FPGA的接收FIFO中。处理器读取接收FIFO的周期数据与发送的周期数据进行比较,并将比较结果由调试端口输出。

通过测试,实际传输数据大小为 1.7×1010bit,错误位数为0,因此证明数字交换网络系统在传输速率为800 Mb/s时,误码率小于 1×10-10,满足系统 720 Mb/s的传输速率要求。

3.2 通道切换功能测试

图4 测试验证系统

通过系统CAN总线下发下行链路通道切换指令,将下行链路默认通道D_IN1-->D_OUT1输出切换为D_IN1-->D_OUT2,测试平台处理器无法接收到回环测试数据。再通过系统CAN总线下发上行链路通道切换指令,将上行链路默认通道U_IN1-->U_OUT1输出切换至U_IN2-->U_OUT1,测试平台处理器重新接收到回环测试数据,说明数字交换网络系统通道切换功能正常。

4 结论

本文介绍的数字交换网络系统很好地满足了综合化航电设备系统资源可配置、系统功能重构的需求,是综合化航电设备的重要组成部分。同时,介绍的数字交换网络技术作为一种高性价比的背板高速数据交换技术,还可以应用于其他类似通用化、模块化设计的无线电通信系统中。

[1]何志强.综合化航空电子系统发展历程及重要支撑技术[J].电讯技术,2004(4):1-5.

[2]茅成.综合通信导航识别系统中的多链路超短波通信的实现[J].电讯技术,2009(8):59-64.

[3]施刚,钱泰来.综合化航空电子的系统管理技术[J].计算机工程,2008(S1):43-45.

[4]郭柳柳,甄国涌,刘东海.基于LVDS传输电缆均衡器的可靠性分析[J].电子技术应用,2014(10):40-42.

[5]严俊.特种任务飞机综合航空电子与任务系统体系结构研究[J].航空电子技术,2012(4):10-15.

[6]邱伟.机载电子设备间高速数据传输研究[J].现代电子技术,2014(12):35-36.

[7]王康,郭志勇.基于FPGA的低成本长距离高速传输系统的设计与实现[J].电子技术应用,2010(10):12-15.