基于FPGA的5B6B编译码器的设计与测试

袁玉英,张连俊,袁慧祥,李鑫磊,罗永刚

(1.山东理工大学计算机科学与技术学院,山东 淄博 255049;2.中国移动德州分公司,山东 德州 253013;3.山东理工大学电气与电子工程学院,山东 淄博 255049)

基于FPGA的5B6B编译码器的设计与测试

袁玉英1,张连俊1,袁慧祥2,李鑫磊1,罗永刚3

(1.山东理工大学计算机科学与技术学院,山东 淄博 255049;2.中国移动德州分公司,山东 德州 253013;3.山东理工大学电气与电子工程学院,山东 淄博 255049)

为避免简单的二电平码对数字光纤通信系统传输的影响,设计适用于数字光纤通信系统的5B6B编译码器,实现对简单二电平码进行码型变换,保证传输的透明性。该设计利用码字数字和(WDS)进行编码码字的选择,采用正、负两种模式交替的方法,在保证平均误码增值系数最小的基础上,以6种码变换规则中的一种为例完成设计。该设计采用FPGA设计流程,运用Verilog HDL语言完成5B6B编译码器各个模块的设计,并在Quartus II软件上进行仿真测试。仿真结果表明:该设计功能正确,可根据需要实现不同码表中相应5B与6B码之间的转换,实现简单,应用灵活,并能减少数字码流中连“0”或连“1”的数目,减小基线漂移。

光纤通信;5B6B编译码器;FPGA;Quartus II;模式交替;仿真测试

0 引 言

在数字光纤通信系统中,电发射机输出适于电缆的双极性码;但光源不能发出负脉冲,因此必须把信号转变为单极性码,才能满足在光纤中传输信号的要求[1]。但是在简单的以二进制方式传输的随机数字码流中,可能会出现较长连“0”或连“1”串的情况,这会带来一些问题,如导致码流中的直流分量发生基线漂移,给定时提取带来一定困难;同时,不能实现在线误码检测,对长途通信系统的维护也将产生不利影响。因此,在数字光纤通信系统中,不适合用简单的二进制码作为系统的线路码。为了保证传输的透明性,数字光纤通信系统经常采用的一种码型为5B6B码。国外的5B6B编译码器大多采用组合电路,即把整个器件集成在一块芯片上,组成一个专用集成块[2]。国内一般采用码表法:就是把预先设计完的码表全部存入到一块可编程只读存储器(programmable read-only memory,PROM)内。早期的码表法实现5B6B编译码器基于单片机完成;近年来,现场可编程门阵列(field-programmable gate array,FPGA)发展迅猛。FPGA具有串/并行工作方式、宽口径适用性、高速度等优点[3]。本文介绍基于FPGA设计实现的5B6B编译码器,并采用Quartus II软件完成了功能测试。该设计方法简单、易于实现,并且具有灵活性。

1 5B6B码编码原理

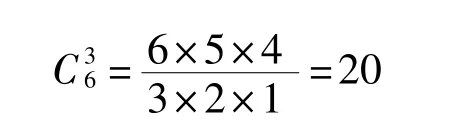

5B6B码属于mBnB码,是将输入的码流每5bit作为一组,称作一个码字,然后通过编码把5 bit的输入码字在相应时隙内转换成6bit的码字输出。其码率提高了6/5倍[4]。在mBnB码中一般n>m,如果一个nB码字中的“0”、“1”个数差别比较大,把这样的nB码字作为禁字,通常把剩余的可以使用的码字按照“1”、“0”的个数分为正和负两种模式(“1”多的为正模式,“0”多的为负模式),并且两种模式交替工作。通常使用码字数字和(WDS)来判断码字是否均匀,并且将选择WDS最好的码字在系统中进行传输,从而确保线路码传输特性等。如果在nB码码字中,把“0”码当作“-1”,把“1”码当作“+1”,那么整个码字所对应的码字和即为码字数字和(WDS)。选取nB码的原则是:尽量采用最小的码字,禁止采用最大的。对于5B6B码,总共有25,即32个 5B码码字,而6B码可以组成的码字共有26,即64个,其中:WDS=0,表示6B码字中含有3个“0”和3个“1”,其码字数为

同理,WDS=+2的码字数为15个,WDS=-2的码字数也为15个,因此可供选择的具有较小WDS的码字一共有50个。然而5B码仅有32个码字,那么只需要从中选择32个6B码码字。为了减少码字中连“1”和连“0”的数目,删除:000011、110000、001111和111100 4个码字,当然也禁止使用WDS=±4和WDS=±6的码字。

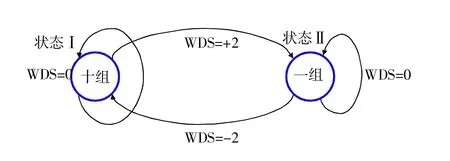

5B6B码有6种码变换规则,其中一种码变换如表1所示的5B6B变换规则,其平均误码增值系数(error multiplication factor,EMF)最小(EMF=1.28),因此,本文选择表1所示的码变换组。表中的“+”组(即模式I)中选用了19个WDS=0的均等码字和13个WDS=+2的不均等码字。在“-”组(模式II)中选用了19个WDS=0的均等码字和13个WDS=-2的不均等码字。“+”组和“-”组交替使用,其交替规则如下:当6B码字为WDS=0的均等码字时,此时不论“+”组或“-”组,其下一个6B码字在上一个6B码字的同组中选择,即不发生交替,此时其下一组栏中标以码字所在组的相同组别符号;例如,“+”组中6B码字为110010,这个码字为WDS=0的均等码字,所以,其下一组栏标“+”,即下一个6B码字仍在“+”组中;当6B码字为不均等码字时,如果6B码字WDS=+2,即这个码字处在“+”组中,其下一个6B码字为WDS=-2不均等码字,下一组栏标“-”。这时6B码字发生交替,以减小累计不均;反之,6B码字为WDS=-2不均等码字,表明这个6B码字处在“-”组,其下一组栏标“+”,即下一个6B码字应在“+”组,码字状态发生交替。交替结果,使6B码字的不均值达到平衡。

上面所述的5B6B码两种模式的交替,也可以用状态图表示,如图1所示。

图1 状态转换图

2 5B6B编码器设计

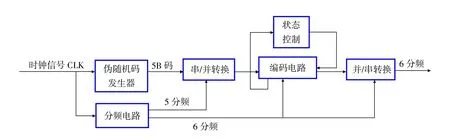

5B6B编码器是将输入的二进制码流按5 bit单元进行分组,组成输入码字。然后将每组5bit的码字在相同时隙内变换成模式I(+组)或模式II(-组)的6bit一组的码流输出。图2为5B6B编码器框图。

表1 5B6B码码表

由图可知,编码器电路由伪随机码发生器、分频电路、串/并间转换电路、状态控制电路及编码电路组成。

2.1 伪随机码发生器

伪随机码是确定序列,但具有随机序列的基本特性,有预先可确定性,可重复产生与处理[5]。伪随机码是利用序列发生器的输入时钟脉冲产生的,为与总时钟同步,在顶层模块设计中先将CLK取反后再输入伪随机发生器。

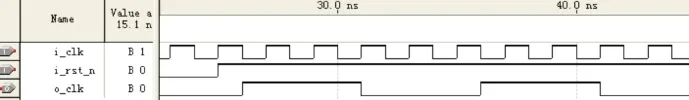

2.2 分频模块

系统会产生一个标准时钟信号clk,此分频电路产生供编码电路和译码电路工作使用的时钟,将分频成5分频和6分频,之间的关系是:f6b=6/5f5b,分别控制串并转换、编码和并串转换。

1)5分频:序列发生器的输入时钟脉冲5分频,可实现每输入5 bit的串行信号同步转换输出5位的并行信号,实现时钟信号的同步[6]。

2)6分频:序列发生器的输入时钟脉冲6分频,实现时钟信号的同步。

2.3 串/并转换模块

此模块实现信号的串行输入、并行输出,或实现信号的并行输入、串行输出[7]。

串/并转换模块:当串行输入5 bit的信号时经过该模块输出并行的5 bit信号[8]。

并串转换模块:由编码模块转换输出的6 bit并行信号进入该模块转换成串行输出,得到所需要的6B码[9]。

2.4 状态控制模块

状态控制模块的原理是当输出的6B码为“+”组时,若WDS=0,则下一个flag不变,若WDS=+2,则令flag=1,从而跳转到“-”组码;当输出的6B码为“-”组时,若WDS=0,则下一个flag不变,若WDS=-2,则令flag=0,从而跳转到“+”组码。这就实现了6B码两种状态“+”组和“-”组模式码的交替,减小了5B6B码的累计不均。

2.5 编码模块

图2 编码器电路框图

此模块是完成5B码转换成6B码的核心环节,在此模块中串并转换输出的并行5 bit信号,受到6分频信号和状态控制模块控制,转换为并行的6 bit信号。此模块由PROM构成,把预先设计好的码表存储在PROM内,利用并行接收的5bit码字作为地址码,查询存储的码表,输出与之对应的并行6B码。

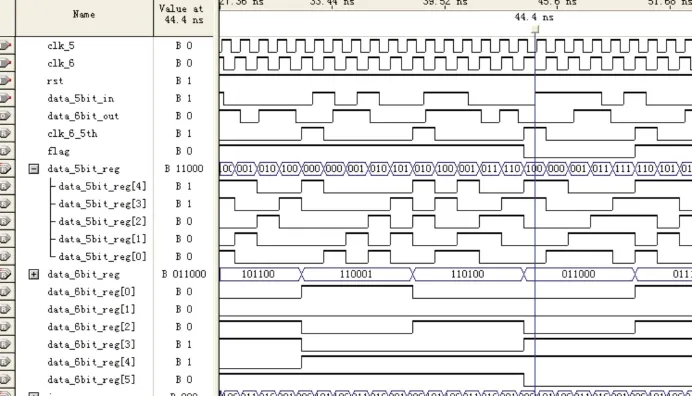

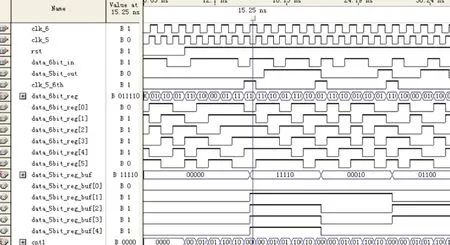

图3是5B6B编码器中主要模块的仿真波形图。该仿真是在Quartus II软件上完成的[10]。

图4是包括编码模块、状态控制模块和串/并转换模块的仿真波形图。输入的串行数据data_5bit_in经串/并转换变为5位并行码,暂时存储于data_5bit_reg,后经编码变为6 bit并行数据,暂存于data_6 bit_reg中,最后经并/串转换变为串行数据data_6 bit_out输出,图中把rst=1且clk_6_5th为高电平时所对应的输入5bit码变为6bit。

flag为组别控制信号,flag=0对应于正组,flag=1对应于负组。

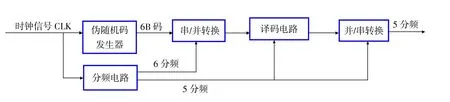

3 5B6B译码器设计

5B6B译码器的功能是把输入的6B码流经过译码正确还原成与5B6B码编码前一致的5B码流。从功能作用来看,5B6B码的译码器变换是5B6B码编码的反变换,图5为5B6B码译码器电路框图。其中,伪随机码发生器、分频电路以及串/并转换电路的设计与5B6B码编码器设计中的类似。

译码模块是将并行输入的6B码转换成相应的5B码,与编码模块类似,其由PROM构成,在5分频信号的控制下,根据预先设计好的码表完成6B至5B码的转换。

图6是5B6B译码器中译码模块和串/并转换模块组成电路的仿真波形图。其把rst=1且clk_5_6th为高电平时所对应的输入6bit码变为了5bit。

4 结束语

本文论述了5B6B编译码器的设计和实现方法,该方法简单,且与组合逻辑电路设计方法相比更加灵活,可根据需要实现不同码表的5B与6B码之间的转换。通过该设计,既减少了数字码流中连“0”或连“1”的数目,减小了基线漂移,又使得系统的误码增值系数减小,累计不均值降低,从而保证了数字光纤通信系统传输的透明性。

图3 5分频模块仿真图

图4 编码器仿真图

图5 译码器电路框图

图6 译码器仿真图

[1]刘增基,周洋溢,胡辽林,等.光纤通信[M].2版.西安:西安电子科技大学出版社,2012:93-94.

[2]卢志茂,冯进玫,陈丽娟,等.光纤通信[M].北京:北京大学出版社,2010:102-103.

[3]杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-727.

[4]汪胜蕾.基于线路编码和RSOA上行再调制的WDMPON系统研究[D].杭州:浙江大学,2013.

[5]赵嘎,王小军,宋鸣,等.基于FPGA的可配置伪随机序列发生器的设计与实现[J].云南大学学报:自然科学版,2012,34(2):147-151.

[6]徐杰,曹小虎,张新文,等.5B6B码的编码仿真与实现课程设计报告 [EB/OL].豆丁网,2014.http:∥www.docin. com/p-756236169.html.

[7]付秀兰,孙立宏.基于65nm CMOS工艺的高速串并转换电路设计[J].中国集成电路,2012(4):57-60.

[8]严刚峰,方红,杨维,等.采用FPGA实现同步串行数据的并行采集[J].自动化仪表,2014,35(9):84-86.

[9]孙志雄,谢海霞.基于FPGA的高速串并/并串转换器设计[J].现代电子技术,2014,37(8):151-152.

[10]Vincent S.Quartus_II软件使用教程[EB/OL].道客巴巴,2013.http:∥www.doc88.com/p-803993007005.html.

The design and test of 5B6B encoder/decoder based on FPGA

YUAN Yuying1,ZHANG Lianjun1,YUAN Huixiang2,LI Xinlei1,LUO Yonggang3

(1.College of Computer Science and Technology,Shandong University of Technology,Zibo 255049,China;2.China Mobile Dezhou Branch,Dezhou 253013,China;3.School of Electrical and Electronic Engineering,Shandong University of Technology,Zibo 255049,China)

Designing the 5B6B encoder/decoder in the digital optical fiber communication system was to avoid the impact of the simple two-level code to the digital optical fiber communication system transmission.So that we can carry out the code type conversion to the simple two-level code to ensure transparenttransmission.Based on considering the minimum average error multiplication factor,the design was performed taking one of the six kinds of code transformation rules for example,using WDS to select the encoding words,taking the mathod of the positive mode and the negative mode alternation.The design adopted the FPGA design process,used Verilog HDL language to complete the design of each module in the 5B6B encoder/decoder and employed Quartus II software for simulation test.The simulation results show that the functions of the design are correct and the conversion between the 5B code and the corresponding 6B code in the different code tables can be achieved according to the needs,so the design can be realized simply and applied flexibly.The design can also decrease the consecutive-zero or consecutive-one number in the digital stream and the baseline drift.

optical fiber communication;5B6B encoder/decoder;FPGA;Quartus II;mode alternation;simulation test

A

:1674-5124(2015)10-0076-05

10.11857/j.issn.1674-5124.2015.10.017

2015-01-30;

:2015-03-27

2013年山东省淄博市科学技术发展计划项目(2013GG02104)

袁玉英(1979-),女,山东德州市人,讲师,硕士,主要从事光纤通信设备研究。