基于FPGA的多通道遥测采编器设计

袁 强, 焦新泉, 方 炜, 李 功

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

基于FPGA的多通道遥测采编器设计

袁 强1,2, 焦新泉1,2, 方 炜1,2, 李 功1,2

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

针对某模型弹遥测数据的采集,设计了一种多通道遥测采编器。采用FPGA作为逻辑控制器,提出了一种模拟开关级联模式采集电路,实现了40路传感器信号的数据采集,并对采集的数据统一编帧存储到存储器中。对采集电路中出现的震荡现象做出分析并提出了解决方案,给出了多路混合数据编帧方法和采集控制时序。试验结果表明:该采编器性能可靠,采集精度高,并具有很好的通用性。

遥测; 现场可编程门阵列; 数据采集; 震荡; 控制时序

0 引 言

目前,数据采集技术已广泛应用于航空航天、雷达等领域,比如:飞行器飞行过程中的多项动态参数,如过载﹑压力﹑冲击﹑噪声等进行记录和回读分析以便对飞行器进行验证和完善[1]。针对某模型弹遥测数据的采集,本文设计了一种多通道遥测采编器,该遥测采编器以现场可编程门阵列(FPGA)作为主控制芯片,主要完成40路传感器数据的高精度采集与编帧,并将打包后的数据送至存储器中,待飞行试验结束后,通过配套地面测试设备和上位机将数据回读进行分析。

1 总体结构

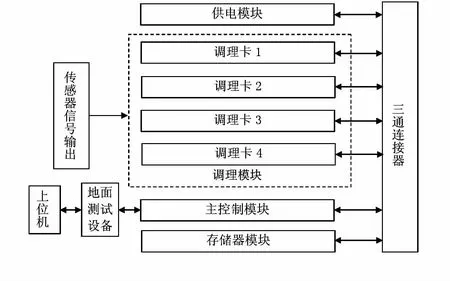

采用模块化设计原则以保证遥测采编器的通用性,按功能分为调理模块、主控制模块、存储器模块和供电模块。调理模块按40路传感器信号种类分成4块调理卡,既保证了采集效果又达到了通用性设计,调理卡将传感器输出信号降噪调理到满足A/D转换器的范围后供A/D转换器采集[2]。主控制模块主要接收地面测试设备下发的记录﹑监测等指令,实现模拟开关切换,各调理卡数据采集编帧以及对存储器读数、写数等功能。供电模块为采编器各用电模块和传感器提供电源以保证系统正常工作。各模块之间通过可插拔式96针三通连接器连接,避免总线上点数不够的可能性。组成框图如图1所示。

2 硬件电路设计

2.1 级联模式采集电路设计

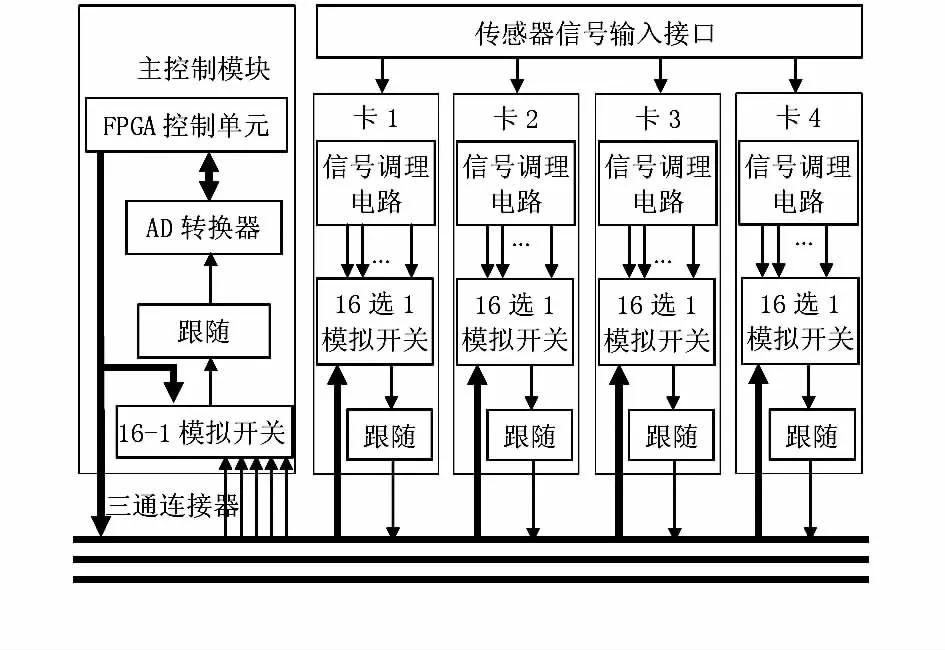

本遥测采编器为提高测量装置的通用性,提出了一种级联模式采集电路。该模式下,主控制卡上设有一个16选1模拟开关作为一级模拟开关,用于选通某块调理卡,每块调理卡上都有一个16选1高速模拟开关作为二级模拟开关,用于选择该调理卡上的通道,通过主控制卡上FPGA控制两级模拟开关的使能端和地址端实现40路传感器信号的通道切换,且可根据实际应用背景,增加或减少调理卡,真正实现了遥测采编器的可扩展﹑可替换。级联采集电路原理框图如图2所示。

图1 系统总体框图Fig 1 Block diagram of system as a whole

图2 级联采集电路原理框图Fig 2 Principle block diagram of cascade acquisition circuit

2.2 模拟开关与运放选型

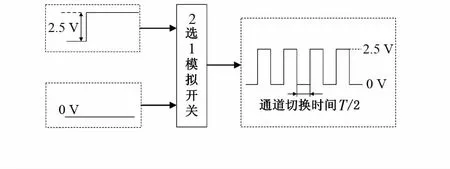

由于不同通道信号经模拟开关通道切换的原因,会导致后级运放输入端为一系列的阶跃信号,可近似为方波。为简化分析,以2选1模拟开关为例,两输入信号分别取AD7667转换电压极值0 V和2.5 V,模拟开关切换输出波形如图3所示。

图3 模拟开关切换输出波形Fig 3 Output waveform switched by analog switch

遥测采编器总采样率为400 kHz,则上图所示模拟开关输出方波信号幅值2.5 V,输出频率为f=200 kHz。因为周期方波信号满足狄利克雷条件[3],将该方波信号展开为傅里叶级数

(1)

式中 脉冲宽度τ=T/2 。可知方波信号是由直流分量和n次谐波分量组成(n=1时又称基波分量)。直流分量F0和各谐波分量幅值Fn表达式如下

(2)

(3)

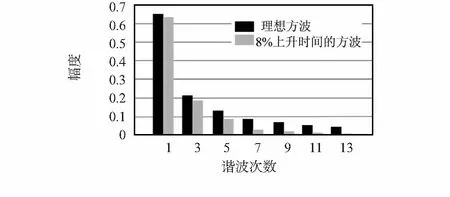

理想方波与实际方波的振幅频谱如图4所示。

图4 理想方波和实际方波的振幅频谱图Fig 4 Amplitude spectrum of ideal square wave and actual square wave

从图4可以看出:方波的1,3,5次谐波分量的实际幅值占理想方波相应谐波分量幅值的极大部分, 而从7次谐波以后,这个比例会迅速衰减。

综上所述,模拟开关的切换速度和后级跟随运放的不失真带宽需大于400 kHz×5=2 MHz。本设计中高速模拟开关选用16路的ADG706,其切换速度达16 MHz,-3 dB带宽高达25 MHz。后级跟随运放选用AD8031,AD8031是一种4路﹑支持单电源或双电源供电﹑低失调电压芯片,其-3 dB衰减率为 80 MHz,压摆率典型值达到30 V/μs,满足系统技术指标要求。

2.3 运放震荡现象分析与消除

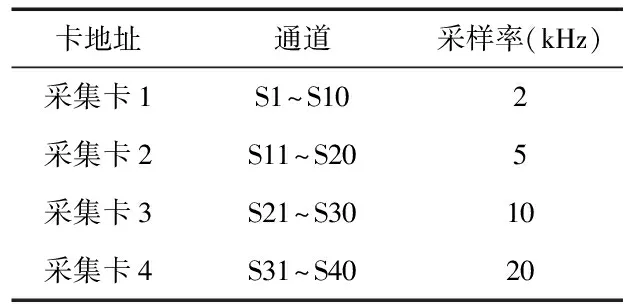

采编器调试过程中发现二级模拟开关和A/D转换芯片前端的运放AD8031的输出端出现震荡现象,如图5所示。

图5 信号震荡现象Fig 5 Signal oscillation phenomenon

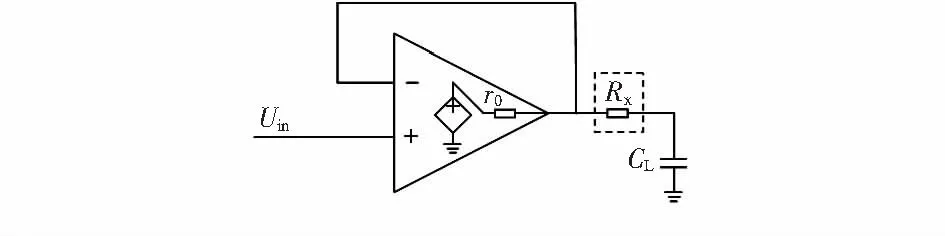

经分析,这是因为高速运放AD8031驱动容性负载的能力有限导致。运放均有一个开环输出电阻r0,而高速模拟开关ADG706存在通道寄生电容,A/D转换芯片内部存在采样电容,当运放做跟随器与容性负载CL连接时可等效为如图6所示电路。

图6 运放内部等效电路Fig 6 Internal equivalent circuit of op amp

3 采集控制逻辑实现

3.1 多通道数据编帧

本设计中,将所有传感器信号按相应采样率采集后通过一定的数据帧格式统一打包编帧并存储。最后上位机软件根据帧结构提取出同一信号的所有采样点数据,从而得到各通道的实测波形。

帧结构决定了各通道信号的采样顺序,而编写帧结构的关键在于能否保证所有信号的均匀采样。在设计采样帧

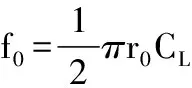

结构时,既要使所有通道的信号满足各自的采样频率,还要尽量减少总的数据量,避免采集数据过于冗杂。本设计中各信号采样率如表1所示。

表1 40路传感器信号采样频率

Tab 1 Sampling frequency of 40-channel sensor signal

卡地址通道采样率(kHz)采集卡1S1~S102采集卡2S11~S205采集卡3S21~S3010采集卡4S31~S4020

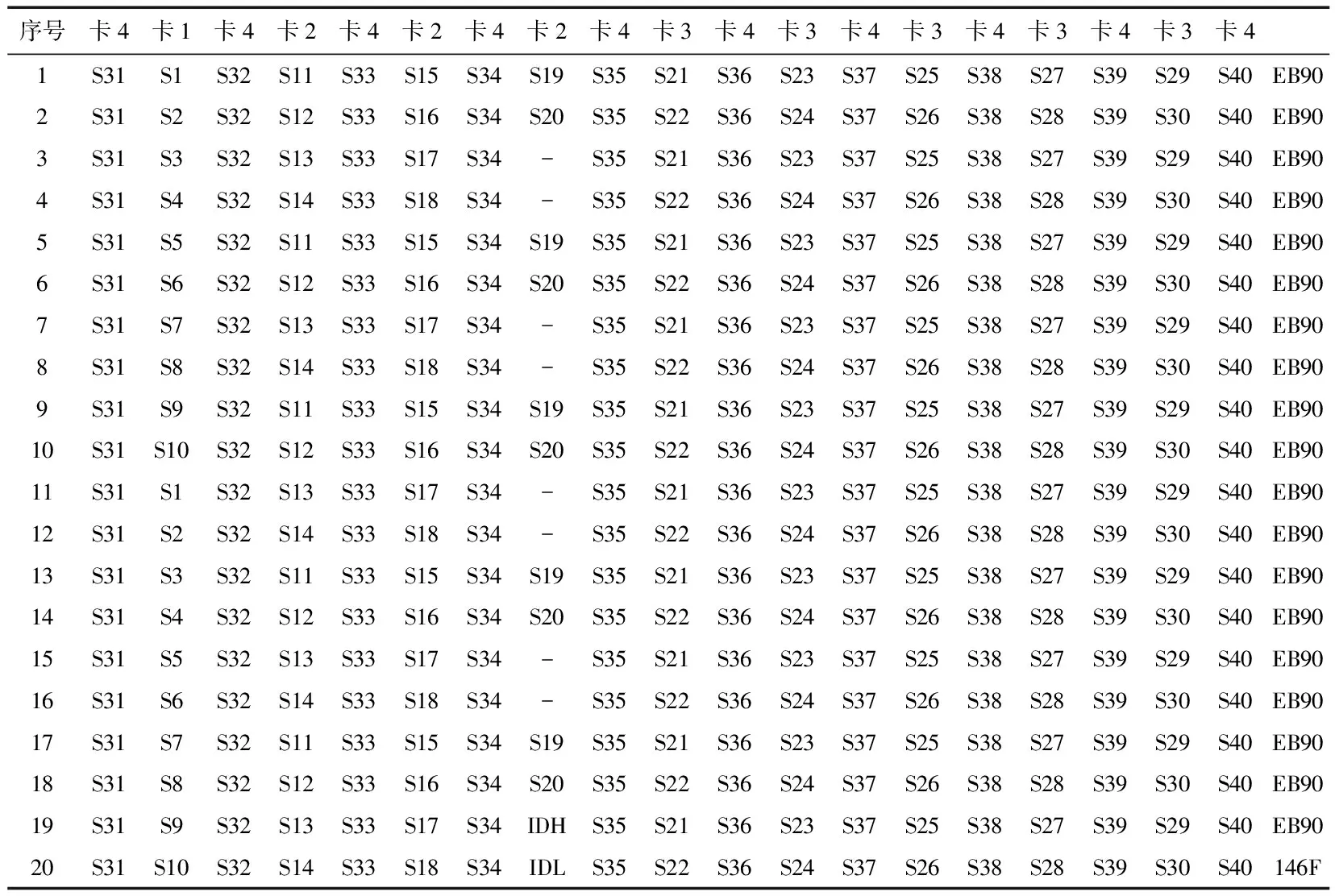

表1中信号采样率均是1 kHz的整数倍,故每个采样点采样频率取1 kHz,则在一个数据帧结构内S1~S10均匀采样2次,S11~S20均匀采样5次,以此类推。为方便上位机回读数据时检查帧结构有没有丢帧和误帧的情况,在帧结构中添加由行结束标志EB90﹑帧结束标志146F以及帧计数IDH,IDL组成的勤务信号[6]。同时为降低通道串扰应保证不同采集卡之间间隔分布。本设计中最终帧结构如表2所示。计算得一帧数据的总采样率为400 kSPS。且每个信号的采样点在一帧数据内或帧与帧之间都是均匀的,满足采样要求。

表2 采集帧结构

Tab 2 Acquisition frame structure

序号卡4卡1卡4卡2卡4卡2卡4卡2卡4卡3卡4卡3卡4卡3卡4卡3卡4卡3卡41S31S1S32S11S33S15S34S19S35S21S36S23S37S25S38S27S39S29S40EB902S31S2S32S12S33S16S34S20S35S22S36S24S37S26S38S28S39S30S40EB903S31S3S32S13S33S17S34-S35S21S36S23S37S25S38S27S39S29S40EB904S31S4S32S14S33S18S34-S35S22S36S24S37S26S38S28S39S30S40EB905S31S5S32S11S33S15S34S19S35S21S36S23S37S25S38S27S39S29S40EB906S31S6S32S12S33S16S34S20S35S22S36S24S37S26S38S28S39S30S40EB907S31S7S32S13S33S17S34-S35S21S36S23S37S25S38S27S39S29S40EB908S31S8S32S14S33S18S34-S35S22S36S24S37S26S38S28S39S30S40EB909S31S9S32S11S33S15S34S19S35S21S36S23S37S25S38S27S39S29S40EB9010S31S10S32S12S33S16S34S20S35S22S36S24S37S26S38S28S39S30S40EB9011S31S1S32S13S33S17S34-S35S21S36S23S37S25S38S27S39S29S40EB9012S31S2S32S14S33S18S34-S35S22S36S24S37S26S38S28S39S30S40EB9013S31S3S32S11S33S15S34S19S35S21S36S23S37S25S38S27S39S29S40EB9014S31S4S32S12S33S16S34S20S35S22S36S24S37S26S38S28S39S30S40EB9015S31S5S32S13S33S17S34-S35S21S36S23S37S25S38S27S39S29S40EB9016S31S6S32S14S33S18S34-S35S22S36S24S37S26S38S28S39S30S40EB9017S31S7S32S11S33S15S34S19S35S21S36S23S37S25S38S27S39S29S40EB9018S31S8S32S12S33S16S34S20S35S22S36S24S37S26S38S28S39S30S40EB9019S31S9S32S13S33S17S34IDHS35S21S36S23S37S25S38S27S39S29S40EB9020S31S10S32S14S33S18S34IDLS35S22S36S24S37S26S38S28S39S30S40146F

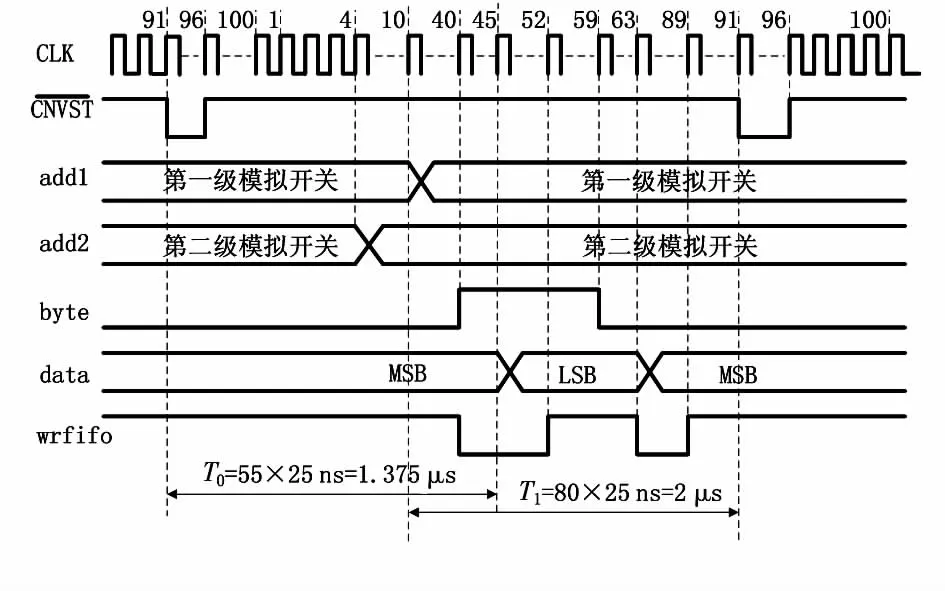

3.2 采集时序设计

采编器选用40 MHz的晶振,每帧数据总采样率为400 kSPS,易知每个采样周期有100个状态机可用,每个状态机时间为1/40 MHz=25 ns。A/D转换器选用16位的AD7667,AD7667有三种可选转换速度,本设计选用800 kSPS的转换速度,即A/D转换一次时间仅需T=1/800 kSPS=1.25 μs。

图7 数据采集时序图Fig 7 Timing diagram of data acquisition

4 测试结果

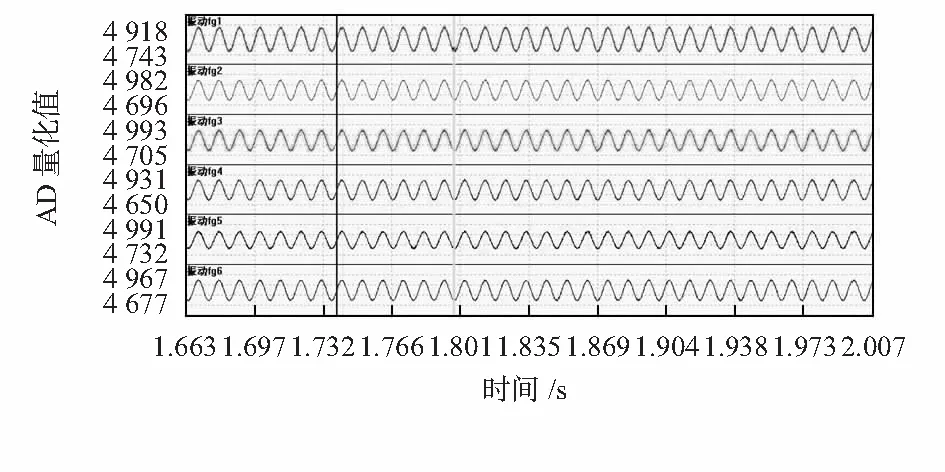

在试验阶段,利用标准信号源提供6路正弦信号给调理卡3输入端,即采编器以10 kHz的采样率对6路正弦信号进行采集并存储,上位机软件对数据进行回读分析并绘制图形如图8所示,分析知波形符合标准信号源的输出,采集无异常。

图8 正弦信号测试曲线Fig 8 Sine signal test curve

5 结束语

本文设计了一种基于FPGA的多通道遥测采编器,完成了40路传感器信号的采集。提出了一种两级模拟开关级联的采集电路,提高采编器的通用性,针对设计过程中运放震荡现象做出了分析并提出了解决办法,详细介绍了多路数据统一编帧的方法和逻辑时序设计。目前,该采编器已成功应用于某模型弹飞行试验,工作性能稳定。

[1] 张力敏.全球定位系统射频前端电路设计[D].大连:大连海事大学,2009:7-12.

[2] 甄国涌,郝晓鹏.基于级联模式的多通道数据采集系统设计[J].计算机应用,2011,26(2):50-52.

[3] Sergio Franco.Design with operational amplifiers and analog integrated circuits[M].西安:西安交通大学出版社,2009:310-353.

[4] 铃木雅臣.晶体管电路设计[M].北京:科学出版社,2014.

[5] 储成君,任勇峰,刘东海,等.基于FPGA的多通道信号采集电路设计[J].科学技术与工程,2013,13(19):5692-5695.

[6] 张鹏飞,李 鹏,沈三民,等.一种遥测数据采编器设计[J].计算机测量与控制,2011,19(2): 468-470.

Design of multi-channel telemetry collector based on FPGA

YUAN Qiang1,2, JIAO Xin-quan1,2, FANG Wei1,2, LI Gong1,2

(1.Science and Technology on Electronic Test & Measurement Laboratory,North University of China,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science & Dynamic Measurement,Ministry of Education,North University of China,Taiyuan 030051,China)

A multi-channel telemetry collector is designed to meet telemetering data acquisition of a mock bomb.Use FPGA as logic controller,propose an acquisition circuit based on analog switches cascade mode,it achieves data acquisition of 40 channels sensor signals and the collected data is compiled in form of frame and stored in memory.Analyze oscillation phenomenon appeared in acquisition circuit and propose solution,give method for multi-channel data frame-editing and acquisition and control timing.Experimental results show that property of the collector is reliable,acquisition precision is high and has good universality.

telemetry; FPGA; data acquisition ; oscillation;control timing

10.13873/J.1000—9787(2015)12—0097—04

2015—11—02

TP 274.2

: A

: 1000—9787(2015)12—0097—04

袁 强(1991-),男,安徽六安人,硕士研究生,研究方向为动态测试技术、高速电路系统。