基于METLAB和Simulink的FIR滤波器设计与仿真

赵杰

(商洛学院电子信息与电气工程学院,陕西商洛726000)

基于METLAB和Simulink的FIR滤波器设计与仿真

赵杰

(商洛学院电子信息与电气工程学院,陕西商洛726000)

为了设计一种FIR数字滤波器,利用MATLAB进行滤波器参数和性能分析,得到滤波器系数之后在Simulink环境下,借助Simulink库及相关工具箱模块,构建一个FIR低通滤波器,并设计完整的测试电路进行仿真与验证,最后生成相应的Quartus II工程。结果表明,该方式简单可行,开发周期短,可以方便地应用于数字信号处理算法的实现。

MATLAB;Simulink;FIR数字滤波器

数字信号处理目前已广泛应用于人工智能、通信、雷达、航空航天、语音处理、图像处理等方面。作为数字信号处理的主要分支,数字滤波器在应用中发挥着重要作用。数字滤波器从实现的网络结构或者从单位脉冲响应分类,可以分成无限脉冲响应(IIR)滤波器和有限脉冲响应(FIR)滤波器[1]。FIR滤波器是全零点滤波器,稳定性好,并且可以实现线性相位,因此,FIR滤波器得到了广泛的应用[2]。MATLAB在设计滤波器方面得到广泛应用,但多数只停留在初步设计获得滤波器系数阶段,距硬件工程实现还有相当距离[3]。 EDA技术的迅速发展,使得数字滤波器可以通过硬件描述语言在FPGA上实现,但是代码编写、调试、仿真均比较复杂,工作量大,开发周期长[4-6]。如果使用调试好的IP核可以减小工作量,但IP核需要单独购买[7]。利用Simulink工具设计滤波器近些年来也有应用,但多数在生成硬件工程仿真后并没有进一步考虑资源利用情况[8-9]。本文利用MATLAB软件工具,在Simulink工作环境下使用图形模型构建FIR滤波器,并进行仿真,将多个工具联合起来,避开复杂的代码设计,大大缩短了开发周期,降低了开发难度。

1 FIR滤波器基本原理

FIR滤波器的单位脉冲响应h(n)是时宽为N的有限长序列,相应的FIR系统函数为:

其特点是系统函数H(z)无极点,因此它的网络结构一般没有反馈支路。其差分方程为:

其直接型结构图如图1所示。

图1 FIR滤波器的直接结构

2 设计过程

以设计16阶FIR低通滤波器为例,其中采样频率50 KHz,滤波器截止频率10 KHz,输入信号序列宽度为9位。

2.1 滤波器分析

利用MATLAB的滤波器分析工具将参数频率和阶次参数代入,这里选用窗函数设计法(选择Kaiser窗),设置FIR滤波器,并对其进行性能分析,其幅频特性如图2所示。

将获得的滤波器系数进行量化,以便后续构建Simulink模型使用。

图2 幅频特性

2.2 FIR滤波器的Simulink模型

在Simulink中构建FIR滤波器系统,由于直接结构比较复杂,改为先设计4阶滤波器,将其作为子结构,再利用4阶滤波器级联构成高阶滤波器,形成完整结构,如图3所示。

上述模型还不能直接用于仿真测试,将其封装为模块“Subsystem”,外接扫频信号源和测量元件,形成完整测试电路模型,如图4所示。

2.3 仿真结果

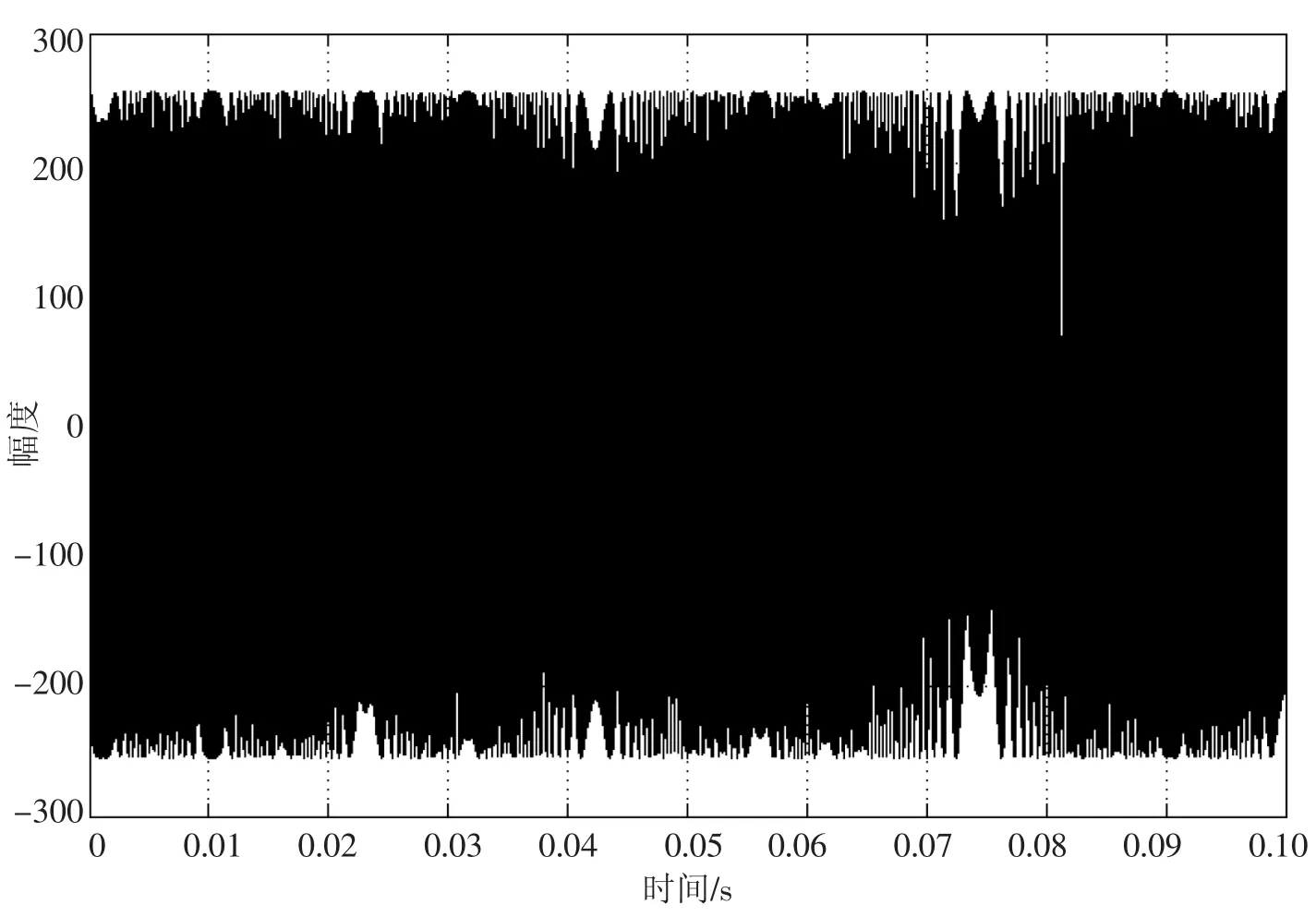

扫频信号源设置为在0.1 s内频率由7 KHz递增至20 KHz,然后进行仿真,观察扫频信号经过低通滤波器前后的波形变化,如图5和图6所示。

图5为扫频信号波形,经过滤波器后,其高频成分受到抑制。由图6可以看出,该波形经过滤波器后的变化情况符合图2所示的滤波器幅频特性,表明该滤波器具有较好的滤波作用。

滤波器模型在经过“SignalComplier”之后可以转换为Quratus II工程[10]。在实用中,还需考虑FPGA资源利用和工作速度情况,以便更好地优化设计。以两款不同芯片为例,进行对比,结果如表1所示。

由表1可以看出,EP2C明显比EP1C占用更少的LE,有更高的fmax。

表1 综合结果对比

图3 FIR滤波器模型

图4 FIR滤波器测试电路模型

3 结论

本文以窗函数为例设计FIR滤波器,利用MATLAB分析得到FIR低通滤波器系数,随后运用Simulink图形模块对滤波器进行模块化设计,设置模块参数,完成滤波器的测试与仿真;同时,该过程也可以方便地改用等波纹最佳逼近等其他设计方法。整个设计过程相对于代码编程的方式简单了很多,设计周期也较短,提高了开发效率。在实际应用中,根据所选器件、处理速度等要求,有可能需要对转化后的工程进行相应的优化。

图5 扫频信号波形

图6 低通滤波后波形

[1]高西全,丁玉美,阔永红.数字信号处理[M].北京:电子工业出版社,2010:135.

[2]丁玉美.数字信号处理[M].西安:西安电子科技大学出版社,2008:181.

[3]张志恒,王卫芳.基于Matlab信号处理工具箱的数字滤波器设计与仿真[J].电力学报,2007,22(1):54-56.

[4]何健标,王宏远,郭跃,等.一种基于FPGA的FIR滤波器实现结构[J].微电子学与计算机,2008,25(3):47-50.

[5]徐志军,王金明,尹廷辉.EDA技术与VHDL设计[M].北京:电子工业出版社,2012:337-349.

[6]谢海霞,孙志雄.可编程FIR滤波器的FPGA实现[J].电子器件,2012,35(2):232-235.

[7]吴继华,王城.Altera FPGA/CPLD设计基础篇[M].2版.北京:人民邮电出版社,2011:106-107.

[8]能芳.基于DSP Builder数字滤波器的FPGA设计[J].价值工程,2011,30(7):141-142.

[9]杜友杰,王紫婷.基于DSP Builder的数字滤波器设计与实现[J].电子测试,2012(8):43-46.

[10]袁博,宋万杰,吴顺君.基于FPGA的Mattab与Quartus lI联合设计技术研究[J].电子工程师,2007,33(1):6-8.

(责任编辑:李堆淑)

Design and Simulation of FIR Digital Filter Based on MATLAB and Simulink

ZHAO Jie

(CollegeofElectronicInformationandElectricalEngineering,ShangluoUniversity,Shangluo726000,Shaanxi)

The design of FIR digital filter was implemented based on MATLAB and Simulink.The parameters and response analysis were accomplished by MATLAB and the filter coefficients were obtained.The Simulink library and toolbox graphic module were used to construct the FIR filter.Then the test circuit model was designed to be simulated.Finally,the Quartus II project was generated.The experimental results show that this method is simple and shorten the development cycle.It can be conveniently applied to the implementation of algorithm.

MATLAB;Simulink;FIR digital filter

TP391

A

1674-0033(2015)02-0020-04

10.13440/j.slxy.1674-0033.2015.02.006

2015-02-28

商洛学院教育教学改革研究项目(13JYJX139)

赵杰,男,陕西汉中人,硕士,讲师