中频数字高斯白噪声的研究与实现

唐叶婷,陈国通,黄 丹,张晓琳

(河北科技大学信息科学与工程学院,石家庄 050000)

中频数字高斯白噪声的研究与实现

唐叶婷,陈国通,黄 丹,张晓琳

(河北科技大学信息科学与工程学院,石家庄 050000)

本文阐述了如何利用多采样的方法快速产生高精度中频数字高斯白噪声信号,采用映射函数的方法实现均匀分布随机序列到高斯分布随机序列的转换,并采用折线逼近法降低了运算量以及占用FPGA芯片的容量,通过多采样率的方法提高采样速率,以节约占用FPGA芯片资源,降低成本。

多采样率;折线逼近法;FPGA;高斯白噪声

1 引言

为了测试通信设备的性能并减少测试费用,信道模拟器是十分必要的,高斯白噪声是信道模拟器的一个重要组成部分,在信号处理和分析中有着重要作用,需要利用高斯白噪声信号源测试和检验导航系统的抗干扰性,导航干扰信号源作为导航对抗信号的生成设备,实现占用资源少、精度高的高斯噪声源对提高对抗信号的性能有着重大意义。

利用均匀分布和高斯分布之间的映射关系以及折线逼近法,可以有效地解决芯片资源与精度的矛盾。通过多采样可以在达到相同效果的前提下大大减少滤波器的抽头系数,大幅度降低占用芯片资源。

2 均匀分布随机序列的产生

2.1 均匀分布随机数的产生

产生均匀分布随机序列的方法有很多种,本设计采用m序列,m序列是由线性反馈移位寄存器产生的周期最长的一种序列,如果选用的反馈移位寄存器级数位n,那么生成m序列的周期为2n-1,状态的取值范围为1~2n-1,在给定初始状态为任意非零值时,m序列的周期不变,移位寄存器的状态值是服从均匀分布的随机数,n越大,产生的均匀随机序列周期就越长,相关性就会越小。综合考虑,本设计采用的是32级线性反馈移位寄存器,本原多项式为 x32+x28+x27+x+1。

2.2 降低m序列自相关性

由于高斯白噪声信号是一个随机过程,在任意不同的时刻采样信号的统计独立的。但是,我们从m序列的产生过程可以看出,相邻的几个状态值之间并不是相互独立的,显然这会对高斯白噪声采样信号之间的统计独立性产生影响,为了减小m序列之间的相关性,需要隔几个时钟周期输出一个状态值,本设计隔4个时钟周期输出一次状态值。

3 高斯分布随机序列的产生

高斯分布随机序列通过均匀分布和高斯分布的映射关系产生,考虑到在MATLAB环境下仿真,随机数位数过多将导致运算量超出内存的限制,因此,本方案截取线性移位寄存器产生的32位随机数的低18位作为均匀分布随机数的输出。根据均匀分布与高斯分布的映射函数

式中,x为服从均匀分布的随机数;y为服从高斯分布的随机数,考虑到高斯分布的实际情况,y仅在[-4,4]之间取值便可以代表绝大部分数值的分布情况,故y在[-4,4]之间取值即可,对y每隔0.01等间隔采样,共801个值。

图1 均匀分布向高斯分布映射曲线图

通过Matlab得到映射关系曲线图,如图1所示,可以看到,映射曲线在一定的区间内有线性关系,并且x绝对值越小,线性关系越明显,在考虑到精度的前提下,对x进行非均匀量化,用不同斜率的直线对关系曲线进行逼近,经过实验,认为23段折线已可以很好地拟合关系曲线,故本设计采用23段折线逼近法,映射曲线与23段折线拟合如图2所示。

图2 折线拟合图

将得到的23组横纵坐标、斜率存入到FPGA的ROM中以备调用。由于涉及到小数,本设计以浮点数的形式将横纵坐标值、斜率值存入到.mif文件中。

4 多采样调制

此时我们得到的高斯白噪声序列是基带中的,在实际应用中,我们需要产生中频上的高斯白噪声序列进而通过上变频调制到所需频段,所以对基带的高斯白噪声进行调制也是至关重要的。

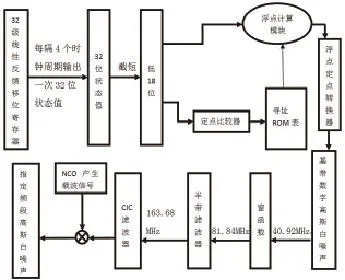

本设计通过多采样对基带信号进行调制,拟产生中心频率为40.92MHz,采样频率为163.68MHz的中频高斯白噪声信号。生成m序列的时钟频率为163.68MHz,为减小m序列的自相关性,输出状态值的时钟频率为40.92MHz,首先经过采样频率为40.92MHz的窗函数,截出所需的频段范围,再经过采样频率为81.84Hz的半带滤波器,最后通过采样频率为163.68MHz的CIC滤波器,这样可以将基带信号的采样频率提高至163.68MHz,与NCO核产生的采样频率为163.68MHz、中心频率为40.92MHz的载波进行调制,最终输出所需的中频信号。

5 FPGA实现

5.1 FPGA实现的整体框图

图3 FPGA实现框图

5.2 系统实现与仿真

在Quartus II开发环境中使用Verilog HDL语言实现上述模块的功能,本设计采用Stratix II:EP2S90F1020I4作为目标器件,仿真过程中,系统的输入时钟为10MHz,通过pll核倍频得到设计中的所需时钟。

图4 序列统计直方图

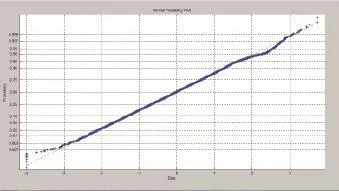

图5 正态检验概率图

将最终得到的高斯白噪声序列导入到MATLAB中进行仿真,分别调用hist函数和normplot函数得到序列统计直方图和正态检验概率图,分别如图4、图5所示。从两图可以看出得到的高斯白噪声的概率密度是高斯型的。

为了验证硬件实现的正确性,将程序下载到开发板中进行测试,通过频谱仪观察得到的高斯白噪声频谱以及功率谱是否满足要求,分别如图6、图7所示。从图中可以看出在通带内,功率谱密度比较平稳,近似为常数,这与我们所学的理论一致,故这种方法可以得到精度较高的中频数字高斯白噪声信号。

图6 高斯白噪声频谱图

图7 高斯白噪声功率谱图

6 结束语

采用折线逼近法以及多采样调制实现中频数字高斯白噪声的方案是可行的,在保证一定精度的前提下,可以大幅度减少FPGA芯片的占用资源,且简单易行,运算量小,由于采用Verilog HDL语言编写,有很强的可移植性,可以灵活的嵌入并应用于其他系统。

[1] 樊昌信,曹丽娜.通信原理(第6版).北京:国防工业出版社,2010

[2] 任文平,梁竹关,李鹏,申东娅.EDA技术与FPGA工程实例开发.北京:机械工业出版社,2013

[3] 刘福奇,刘波.Verilog HDL应用程序设计实例精讲.北京:电子工业出版社,2009

[4] 陈曦,邱志成,张鹏,何初冬.基于Verilog HDL的通信系统设计.北京:中国水利水电出版社,2009

[5] 刘东华.Altera系列FPGA芯片IP核详解.北京:电子工业出版社,2014

[6] 吴继华,蔡海宁,王城.Altera FPGA/CPLD设计(高级篇).北京:人民邮电出版社,2011

Resesrch and Implementation of IF Digital Gaussian White Noise

Tang Yeting, Chen Guotong, Huang Dan, Zhang Xiaolin

(School of Information Science and Engineering, Hebei University of Science and Technology, Shijiazhuang, 050000)

This paper describes how to use multi-sampling method to produce high-precision digital IF signal WGN quickly, using the mapping function method to achieve convertion of a uniformly distributed random sequence and Gaussian random sequence, and using a line approximation method to reduce the computational complexity and capacity of FPGA chip, Increasing the sampling rate by the method of multirate to save FPGA chip resources and reduce costs.

Multirate; Polyline approximation; FPGA; Gaussian White Noise

10.3969/J.ISSN.1672-7274.2015.07.009

TN927+.2

A

1672-7274(2015)07-0033-03

唐叶婷,女,1992年生,河北科技大学硕士研究生在读,研究方向为数字交换与传输。