孔电阻变异影响因素分析

张军杰 韩启龙 刘克敢(深圳崇达多层线路板有限公司,广东 深圳 518132)

孔电阻变异影响因素分析

张军杰 韩启龙 刘克敢

(深圳崇达多层线路板有限公司,广东 深圳 518132)

目前市场上越来越多的客户要求进行低电阻高绝缘的电子测试,这类PCB中,部分PCB线路不单是导线同时还是信号线,线路的阻值变化会造成信号的延滞和衰减,引发功能性问题。本文主要介绍了孔电阻的测试原理,通过对影响孔阻值变化的因素进行分析验证,并逐个分析论证,最终定位问题根源之所在。

孔电阻;镀铜;减成法

1 前言

通常情况下,PCB的开短路测试参数值中的开路阻抗设为25Ω,线路阻值大于25Ω时机器判断为开路,小于25Ω时机器判断为合格,对于阻值小于25Ω的线路则无法精确测试出其实际电阻值,25Ω以下的线路成为测试盲区。在实际生产中发现PCB的某些缺陷,如孔内无铜、空洞、铜薄、线幼、线路缺口等问题均会影响到线路阻值,当阻值小于25Ω时,用通常的开短路测试方法来测试以上缺陷板时,测试结果显示PASS,但客户经过高温焊接后阻值发生变化,导致开路问题发生。

现有的测量PCB导孔用的是普通的两线测试,测量导孔的电路共用一个电压回流以及电流回路,由于电压测量回路与电流测量回路本身也有阻抗,对导孔的测量值干扰太,造成测量精度不准,不能满足用户的要求,故目前PCB电测业界正在推广四线式测试法应用于PCB开路测试中。

2 PCB孔电阻原理介绍

2.1 四线测试孔电阻简介

孔电阻控制是一项既重要又具有特色的项目,有别于单纯的通断测试,更能反映孔壁铜厚的状况。下面对孔电阻测试方式作一简单介绍:开尔文连接方式(或称四线测试方式)如图1所示。

开尔文连接有两个要求:对于每个测试点都有一条激励线和一条检测线,二者严格分开,各自构成独立回路;同时要求检测线必须接到一个有极高输入阻抗的测试回路上,使流过检测线的电流极小,近似为零。

激励线即是电流供给回路,检测线即是电压测定回路,电流、电压两回路各自独立。电流供给回路两端子与电压测定回路两端子共计四端子,故称四线测试。可精确测定被测PCB 之微小阻值,其四线测试的测试精度可达到mΩ级。

图1 开尔文连接

2.2 孔电阻计算公式

R=ρ×L/S

式中:ρ——铜的电阻率:

0.017(mΩ×mm),L——板厚;

S——面积=πt(d-t)(mm2)[其中:d=孔径]

2.3 孔电阻的测试

孔电阻的测量用很简单的伏欧法R=V/I,其测试模型如图2。

图2 四线测试

3 PCB孔电阻变化差异原因分析

3.1 试验一:正常流程,两次沉铜+两次加厚铜

(1)试验设计

选则一款典型产品,最小孔径Φ0.25mm,厚径比12:1。拟订了下述两次沉铜、两次加厚铜流程:正常流程→钻孔→去钻污→沉铜1→加厚铜1→沉铜2→加厚铜2→图形转移→图形电镀→正常流程。

(2)试验结果及分析

终测后结果孔内无铜比例为30%~50%,切片分析主要原因为塞孔、图电镀铜及镀锡不良(图片见表1),缺陷率很高而且数量不稳定,需要进一步的验证分析。

表1 孔无铜原因分析

3.2 试验二:在试验一基础上进行工艺改良

(1)试验设计

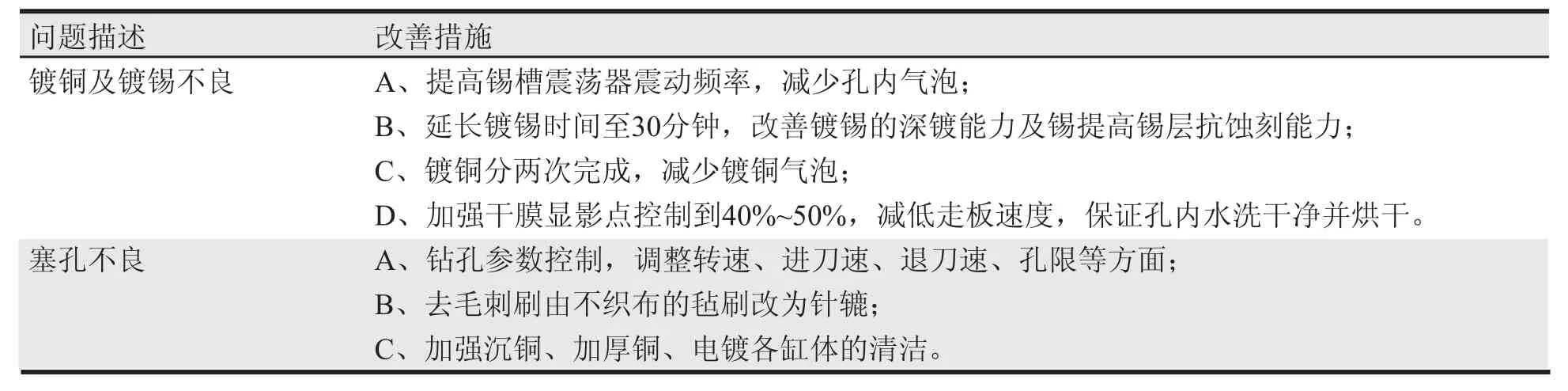

从不良切片显示可看出,解决镀铜及镀锡不良及改善塞孔非常重要。通过以往经验,决定从以下方法对上述问题进行改善。见下表2。

表2 孔无铜改善措施

(2)试验结果及分析

经过上述改善,终测后结果显示孔内无铜比例降至4.7%,孔电阻测试数据如下,要求孔电阻<2.9 mΩ。见图3,试验二条件下工艺改良的孔电阻测试数据,孔电阻值主要分布在(1.4~2.0)mΩ,12356个孔中有22个孔超出2.9 mΩ,缺陷率为0.178%,整体铜厚偏厚且不均匀。

图3 孔电阻分布图

(3)孔电阻超标原因分析

对孔电阻超标的孔做切片分析,发现两种现象存在,一是铜层由两头向中间逐渐变薄,孔中间仅5 mm ~10 mm;二是塞孔即孔内镀铜不良。见表3所示。

表3 孔内镀铜不良

造成铜层薄和镀铜不良的原因主要有:

①图形电镀铜时药水对孔内浸润不佳,造成孔内镀铜不良或深镀能力不够;

②镀铜后孔径减少(0.05~0.1)mm,提高了镀锡的难度,在蚀刻时形成较薄的铜层;

③在图形电镀铜前孔内有塞孔或毛刺;

④镀铜后孔壁经微蚀造成孔壁铜厚偏薄。

3.3 试验三:改正常法为减成法,解决孔电阻问题

(1)试验设计

流程更改为:正常流程→钻孔→去钻污→沉铜1→加厚铜→沉铜2→脉冲电镀铜→图形转移→酸性蚀刻→正常流程,因为通过流程的更改,还可以获得以下优势:

(A)避免镀锡不良问题;

(B)避免图形镀铜而引起的不良品;

(C)采用脉冲电镀,可提高镀铜的深镀能力;

(D)脉冲电镀生产线有振荡器及采用Edactor的搅拌方式,减少孔内气泡,改善孔内镀层质量。

加强钻孔工艺控制及操作,从保养、过滤系统改善、加强清洁等方面减少过孔毛刺及塞孔;

限制Entek的返工次数,减少因为返工造成的铜薄,规定只可返工一次来保证孔铜。

(2)试验结果

通过上述改良,重新制作样板,抽测18 pnl(共45036个孔)其孔电阻值未发现有孔电阻超标,具体测试数据阻值小于2.0 mΩ,最小铜厚28 mm。

4 结语

通过对PCB孔电阻变化差异原因分析,并进行一系列的试验验证,从工艺流程的优化、采用不用的电镀方式、钻孔工艺参数的优化、加强保养清洁规范化、限制Entek的返工次数等几个方面着手,解决了孔阻值超差的问题。

[1]刘璐. 印制线路板微孔镀铜能力的研究[J]. 印制电路信息, 2010/S1.

[2]陈于春. 高厚径比PCB深镀能力影响因素的研究[J]. 电镀与环保, 2009,6.

[3]周毅. 微孔无铜原因分析与改善[J]. 印制电路信息, 2012, 9.

[4]张炳龙,丁玉鲜. PCB孔金属化电阻的测量与分析[J]. 印制电路信息, 2010,8.

张军杰,从事线路板研发工作8年,高级工程师,负责HDI新产品的技术开发工作。

Analysis and argument difference root cause of the PCB hole resistivity

ZHANG Jun-jie HAN Qi-long LIU Ke-gan

On the market at present, more and more customers demands for low resistance and high insulation of electronic testing. For this kind of PCB, wire is not only part of the PCB line or signal lines, at the same time, line resistance changes will cause delay and attenuation of signals, cause functional problems. This article mainly introduced the hole resistance testing principle, made the analysis of factors influencing the resistance changes of hole, and analyzed one by one, finally located the root cause.

Through Hole Resistance; Copper Plating; Subtractive Process

TN41

A

1009-0096(2015)01-0023-03