基于可编程器件的通信检测系统接口设计

吴志抄,谭业双,李召瑞,孙慧贤

(军械工程学院 信息工程系,河北 石家庄 050003)

0 引言

1 系统整体设计

为提高对通信检测设备的灵活性和升级性,本文借鉴虚拟仪器结构,设计某型基层级检测系统,用于对通信设备进行快速检测[1]。使用通用计算机和多功能检测接口构建硬件平台,检测接口用于接收计算机生成的数字激励信号和将采集到的通信设备响应信号转换为数字信号传送到计算机。由于通信设备接口信号的多样性,检测接口应当具有重构能力,能够在不改变硬件结构的前提下通过软件重新配置,适应对多种信号的检测需求。

检测接口电路从功能上可以划分为激励生成通道和数据采集通道,分别使用DAC和ADC及相应的辅助电路完成数字信号与模拟信号的相互转换。FPGA是检测接口电路的信息传输与控制单元,向上提供与上位机通信的数据和控制接口,向下提供与ADC和DAC的数字信号通信接口,能够完成对采集信号的预处理,并用于整个接口电路的控制。

图1 检测系统结构框图

检测接口结构框图如图1所示。其激励通道由FPGA、DAC、滤波放大电路组成,用于将上位机发送的数字激励信号转换成与通信设备信号物理特性一致的模拟信号。数据采集通道由信号调理电路、ADC和FPGA组成,用于将采集得到的设备响应信号转化为数字信号传送到上位机进行分析处理。混合电路和变压器主要用于实现二线平衡双工传输功能,并提供对外二线接口。

2 硬件电路设计

从结构上,检测接口可以分为DAC单元、滤波放大单元、二线接口单元、混合单元、信号调理单元、ADC单元和FPGA系统单元。

2.1 DAC与滤波放大单元

DAC与滤波放大单元用于将数字信号转换为模拟信号,并完成对信号的调理、幅度调节与功率放大功能。其硬件电路如图2所示。

图2 DAC与滤波放大单元硬件电路

该单元由3部分电路组成,分别是DAC芯片电路、无源滤波电路和差分放大电路。

DAC芯片为ADI公司生产的高性能、低功耗CMOS数模转换芯片 AD9762,AD9762为 12位分辨率,支持最高125 MS/s的更新速率。该芯片使用5 V、3.3 V可选单电源供电,最高功耗175 mW,2 mA~20 mA差分电流输出,负载 RLOAD为 100Ω时输出电压范围为 0.2 V~2 V[2]。FS ADJ引脚连接外接电阻RSET,用于满量程电流输出调节。REFIO引脚用于基准电压VRFE输入/输出,选择内部1.2 V基准电源时通过一个0.1μF电容与模拟地连接。其差分输出电压VDOUT与输入的12位数字代码(DCODE)的关系式为:

无源滤波电路由电感与电容组成截止频率为20 MHz的7阶巴特沃斯低通滤波器,用于信号整形和消除毛刺干扰。

差分放大电路以全差分放大器AD8476为核心组成,用于将通过无源滤波电路的模拟差分信号进行增益调节和功率放大。AD8476是一款功耗极低的全差分精密放大器,其带宽为6 MHz,使用±5 V电源供电时的输出电压范围为-4.845 V~4.82 V[3]。检测激励信号的峰峰值为4.3 V和6.2 V,而DAC的输出峰峰值电压为2 V,因而差分放大电路的增益应当大于3.1,这样才能使得激励生成通道的输出信号幅值符合检测需求。考虑到DAC的转换效率和可能存在的误差,可设计差分放大电路具有两个略大于满幅度输出的增益值。

图 2中使用外部扩展电阻 R1~R6组成反馈电阻网络, 其中 R1=R2=10 kΩ 为输入电阻,R3=R6=24 kΩ、R4=R5=33 kΩ为两组反馈电阻。该电路的增益值分别为A1=R3/R1=2.4,A2=R4/R1=3.3。为了提高检测接口的自动化程度,使用1个 2路 2:1电子开关ADG736用于两组反馈电阻的切换,通过改变其控制端IN1和IN2的电平逻辑,完成开关动作。ADG736使用5 V供电时,导通电阻RON为 2.5Ω,带宽大于 200 MHz,通过峰值电压为5 V。

2.2 二线接口与混合电路单元

二线接口与混合电路单元用于为信号激励与数据采集提供对外二线接口和实现收发信号的双工传输。其硬件电路如图3所示。

图3 二线接口与混合电路单元硬件电路

二线接口电路由电压比为1的变压器以及电阻RS1、RS2和电容 C9、C10组成,用于提供检测电路对外的二线接口,实现接收与发送信号的传输,同时可以隔离外部直流信号。RS1、RS2用于与线路负载阻抗匹配并隔离远端反射和提供线路的能量交换,电容C9、C10用于配合组成激励发送端扩展滤波电路。

混合单元的功能是一阶模拟回波抵消,用于抵消本地发送信号。图 2中R7~R10为输入电阻,同时与 C3~C8组成一阶低通滤波器。两个仪表放大器AD8429用于将二线平衡信号转换为单端信号。AD8429为低噪声、高精度仪表放大器,其增益为1时增益精度为0.02%、CMRR为80 dB、带宽为15 MHz,使用±12 V电源供电时其输出电压范围为-10.1 V~10.7 V,使用单个增益控制电阻RG能够控制其增益范围为1~1 000,其增益控制关系为G=1+6 kΩ/RG[4]。

LT6600-10将一个全差分放大器与一个近似切比雪夫(Chebyshev)频率响应的四阶10 MHz低通滤波器集成在一起。芯片为低噪声全差分输入/输出放大器,内部集成两个运算放大器、电阻电容网络,组成1倍增益放大电路和一个10 MHz低通滤波器,使用±5 V电源供电时其输出电压范围可达到±5 V[5]。

在图 3中,U1为激励单元输出差分信号,U3为设备响应信号,RL为线路负载,假设通过变压器初级线圈与次级线圈的电流分别为i1和i2,则有:

式中,RS=RS1+RS2。同时有:

则由式(2)和式(3)可得:

在电路中,第一个AD8429电路和LT600-10电路的增益值均为1,则通过调节第二个AD8429的增益值,使其增益值G3=(RS+RL)/RL时,混合单元的输出差分信号U′3=U3×RS/RL。这样就达到消除近端发送信号的目的。

若线路电阻RS与负载电阻RL完全匹配,则第二个AD8429的增益值为2时,混合电路的输出U′3=U3。考虑到阻抗失配现象的普遍存在,因此选择电位器作为第二个AD8429的增益控制电阻,在线路阻抗失配的条件下,通过调节增益控制电阻来实现混合单元消除近端信号的目的。根据前文所述,可以得到混合电路输出信号U′3与二线输入信号U3比值跟增益控制电阻RG之间的关系式:

因此只要知道RG的值,就能够通过式(5)准确地对通过混合单元造成的输入信号幅值的线性误差进行修正。为了提高检测接口的自动化程度和实现对RG值的实时感知,选择数字电位计AD5272作为第二个AD8429的增益控制电阻。AD5272为1 024位分辨率、1%电阻容差误差、I2C接口和50-TP存储器数字变阻器,最大阻值为20 kΩ,可使用 5 V电源供电[6],其阻值调节步长为1.95Ω。

2.3 信号调理与ADC单元

信号调理与ADC单元用于将混合电路输出的模拟差分信号转换为输入信号并输入到FPGA,该部分为数据采集的核心单元,其硬件电路如图4所示。

图4 信号调理与ADC单元硬件电路

由于被测信号的最高频率不超过2.048 MHz,根据奈奎斯特采样定理,使用4.096 MHz采样速率进行采样就能得到信号完整的信息,但是在工程中,通常使用5~10倍速率进行采样。因此ADC选择12位、10 MS/s采样速率模/数转换器AD9220,其为+5 V单电源供电,70 dB信噪比,86 dB无杂散动态范围,内置片内高性能、低噪声采样保持放大器和可编程基准电压源,并具有满量程输出指示功能[7]。使用1 V基准电压时其输入范围为2 V(峰-峰值)。

信号调理电路应当具有抗混叠滤波和信号幅度调节的功能。该电路选择全差分放大器AD8476组成,考虑到检测时输入信号的幅值大于ADC的输入范围,因而选择其输入电阻为10 kΩ,选择数字电位器AD5272为反馈电阻RF,则其增益值G4=RF/10 kΩ,电路的增益值为0.000 2~2可调。放大器输出经过2个100Ω电阻和2个电容组成的低通滤波器后送至ADC。同时,AD8476以ADC的基准电压VREF为共模参考电压。

基于上述内容,则可得数据采集通道ADC的输入信号VIN与二线接口输入检测信号U3之间的关系为:

式中,RF为信号调理电路数字电位器AD5272的阻值,RG为混合电路数字电位器AD5272的阻值。

2.4 FPGA单元

FPGA单元以Xilinx公司的FPGA芯片XC3S400为核心电路组成,其程序存储芯片为XCF02S,使用40 MHz有源晶振,5 V电源供电,使用稳压芯片提供电路所需的3.3 V、2.5 V和1.2 V电源。USB接口作为微处理器常用的外部总线接口,目前已经得到了广泛的应用[8],因此考虑选用USB2.0接口作为FPGA与上位机之间的数据接口。同时采用JTAG接口用于FPGA和其配置芯片的程序烧写。关于FPGA电路的设计、开发技术已经较为成熟,本设计相比与其他通用FPGA电路的设计并无独特之处,因此不再对FPGA单元进行详细描述。

3 FPGA程序设计

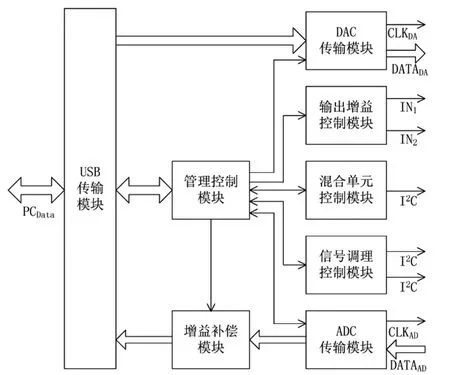

在检测接口电路的设计中,FPGA是检测接口电路的信息传输与控制单元的核心,其可编程配置能力和能够高速、并行处理数字信号的能力是检测接口的灵活性和升级性的关键。其内部程序使用 Xilinx公司的FPGA开发环境ISE进行设计并完成烧写。程序设计使用模块化设计思想,其结构示意图如图5所示,可以分USB传输、管理控制、DAC传输、输出增益控制、混合单元控制、信号调理控制、ADC传输控制和增益补偿8个模块。下面就各个模块的功能分别进行介绍。

图5 FPGA程序框图

(1)USB传输模块,用于通过FPGA单元上的USB接口电路实现FPGA芯片与上位机的信息传输,具有USB电路的配置功能,并实现标准USB信号封装、解封装功能,将接收到的上位机信号解封装为透明数据传送到管理控制模块和DAC传输模块,将管理控制模块、增益补偿模块输出信号封装为标准USB信号通过USB接口电路传输到上位机。

(2)管理控制模块,是整个程序的主控单元。该模块用于接收USB传输模块输出的控制信号,对其余的通信模块进行控制,并输出检测电路的工作状态到USB传输模块,最终传输到上位机。同时用于控制其余模块的工作状态,接收混合单元控制模块、信号调理控制模块、ADC传输模块输出的反馈信息进行工作状判断,根据混合单元控制模块、信号调理控制模块反馈信息控制增益补偿模块的补偿量。

(3)DAC传输模块,在管理控制模块的控制下工作,接收USB传输模块输出的激励信号,并将信号转换为DAC芯片的数据输入信号,同时为DAC芯片提供转换时钟。

(4)输出增益控制模块,用于在管理控制模块输出的控制信号下工作,根据需求通过两路输出信号IN1和IN2分别控制差分放大电路的2个电子开关ADG736。

(5)混合单元控制模块,用于在管理控制模块输出的控制信号下工作,根据需求通过输出I2C信号控制混合单元的数字电位计AD5272的阻值,完成信号混合功能,并将AD5272的阻值信息反馈给管理控制单元。

(6)信号调理控制模块,用于在管理控制模块输出的控制信号下工作,根据需求通过输出2路I2C信号控制信号调理电路的2个数字电位计AD5272的阻值,完成信号调理功能,并将2个AD5272的阻值信息反馈给管理控制单元。

(7)ADC传输模块,在管理控制模块的控制下工作,接收DAC芯片输出的采样数据,并将数据传输到增益补偿模块,同时为ADC芯片提供采样时钟。该模块同时接收ADC输出的满量程指示信号和数据输入指示信号,并传送给管理控制模块。

(8)增益补偿模块,用于接收来自ADC传输模块的采样数据和管理控制模块输出的增益补偿信息,对ADC芯片采样获得的信号进行增益补偿,实现检测信号的完整性。

4 结论

本文根据检测需求,选择了以通用计算机和专用检测接口结合的检测系统,重点描述了硬件检测接口的电路设计和FPGA硬件描述语言设计。差分放大、二线接口、混合、信号调理等电路单元通过仿真,功能、性能均能达到设计要求。本设计能够为类似检测系统接口电路设计提供借鉴参考。

[1]金伟,齐世清,王建国.现代检测技术[M].北京:北京邮电大学出版社,2007:270-272.

[2]Analog Devices.12-bit,125 MSPS TxDAC®D/A converter AD9762 datasheet[EB/OL].[2014-05-14].http://www.analog.com.

[3]Analog Devices.低功耗、单位增益、全差分放大器和 ADC驱动器AD8476数据手册[EB/OL].[2014-05-14].http://www.analog.com.

[4]Analog Devices.1nV/√Hz低噪声仪表放大器 AD8429数据手册[EB/OL].[2014-05-14].http://www.analog.com.

[5]Linear Technology.Very low noise,differential amplifier and 10 MHz low pass filter LT6600-10 datasheet[EB/OL].[2014-05-14].http://www.linear.com.cn.

[6]Analog Devices.V024/256位、1%电阻容差误差、I2C接口和50-TP存储器数字变阻器AD5272数据手册[EB/OL].[2014-05-14].http://www.analog.com.

[7]Analog Devices.Complete 12-bit 1.5/3.0/10.0 MSPS monolithic A/D converters AD9220 datasheet[EB/OL].[2014-05-14].http://www.analog.com.

[8]闫娜娜.基于USB接口的数模转换系统设计[J].电子技术,2013(5):35-37.