基于FPGA和AD5628多通道信号源的设计与实现

黄江鹏,崔永俊

(中北大学电子测试技术国家重点实验室;仪器科学与动态测试教育部重点实验室,山西太原030051)

航空航天电子测量技术领域中,多数电参量采用信号源作为激励。以往采用FPGA和直接数字频率合成DDS原理实现模拟信号源的设计中,多用D/A转换芯片(AD768/AD9744)和多路模拟开关(ADG1208)实现多通道模拟量的输出[1]。为解决该类信号源电路设计的复杂性问题,本文基于FPGA和PCI技术,巧妙选用AD5628进行设计,结合VB、VC上位机软件编译来实现48路模拟信号源的输出,在简化电路设计基础上降低硬件实现成本,并且大幅提高了该信号源的可靠性。

1 系统方案

1.1 系统结构

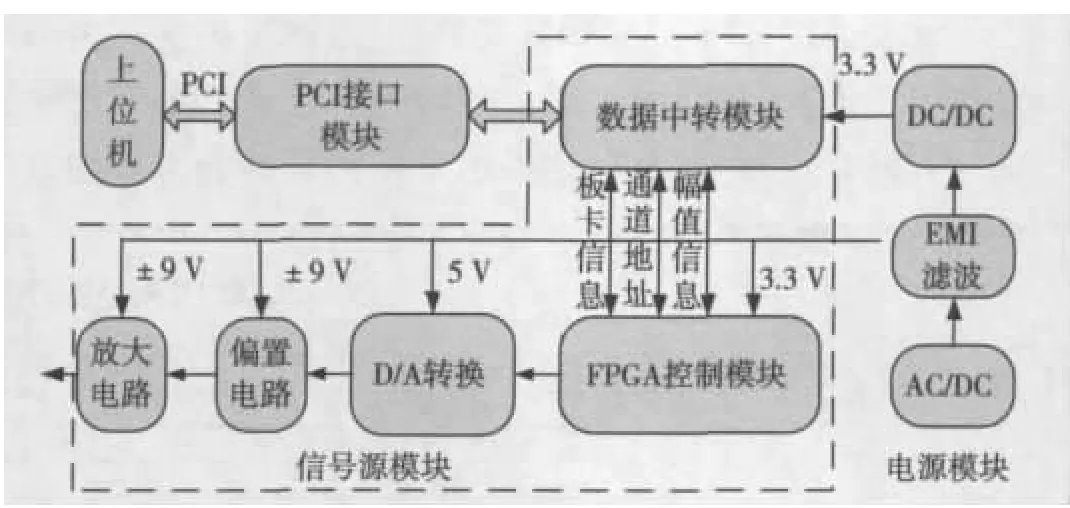

该信号源采用模块化设计思想,主要由电源模块和信号源模块两部分构成。电源模块主要为测试台背板和信号源模块分别提供定制±9 V、+5 V线性电源输出和+5 V隔离电源。信号源模块包括FPGA中央逻辑控制模块、D/A转换模块、信号源偏置放大模块、信号输出模块,各功能模块在FPGA控制下共同实现48路模拟量的输出。系统的总体方案设计框图如图1所示。

1.2 工作原理

测试台上电复位后,上位机将发送8位十六进制命令字,其中包括板卡号信息、寄存器地址通道信息及幅值信息,经过PCI总线接口打包成40位二进制数传给背板,背板通过判断并解析所收到相应命令信息后,经422总线差分传输至信号源模块中的FPGA中央逻辑控制中心,FPGA控制实现对高精度D/A转换芯片AD5628进行数模转换与通道选择,最后经偏置和放大电路完成48路模拟量信号的输出。

图1 系统总体方案设计框图

2 硬件电路设计

2.1 PCI接口模块

该模块是PCI总线和FPGA控制模块的中转站。将PCI卡设计成可插型板卡,方便与计算机的PCI卡槽相连,从而实现上位机与底层硬件电路的各命令信息和状态信息的通信[2]。设计采用PLX Tech公司的PCI9054,可支持32 bit/33 MHz PCI总线桥芯片,在突发状态下能够实现 PCI的全速数据传输,满足系统传输速率491.52 kbit/s的要求。

2.2 光电转换模块

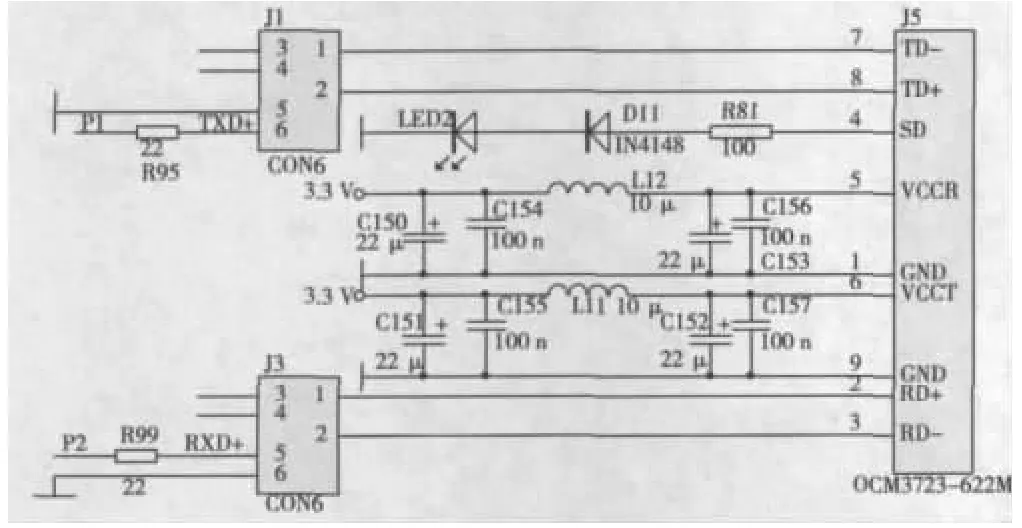

本设计对于模拟信号源的输出信号要求其抗干扰能力突出、精度高,同时适用于光纤传输高带宽、低延迟、对距离不敏感、拓扑灵活、支持多种上层协议等特点。在以往光电转换电路中光电转换模块多采用光电转换器OCM3443、OCM3723来实现相应低速、高速传输电路,其PCB板布线复杂,成本较高。本文通过设计2个接口CON6(等价于6个焊盘),巧妙实现了高低速复用光接口的功能,采用OCM3723芯片同时实现信号的高低速传输,在低成本的同时简化了电路设计冗余。以数据中转模块为例,上位机下发命令经由PCI总线接收转发差分信号至光接口的RD+和RD-端接收。根据系统传输速率不同而选通不同管脚以实现功能,若选低速,则CON6中管脚1与5、2与6用0Ω电阻选通,P1、P2连接至FPGA的I/O口;若选高速,则CON6中管脚1与3,2与4用0Ω电阻选通,后接DS92LV1023和DS92LV1224外围电路。如图2所示为系统采用低速通道的外围电路设计。

图2 OCM3723外围电路设计

2.3 信号源模块设计

2.3.1 隔离电路分析设计

在硬件电路设计中,常用的隔离技术有光隔离、磁隔离和电容隔离等。相对于光耦隔离器而言,磁隔离具有集成度高、功耗低、使用方便和可靠性强的优点,设计使用ADI公司基于磁隔离的通用型四通道数字隔离器AD-uM1400,采用5 V供电,由半导体工艺构成微型线圈,线圈之间加绝缘层,与变压器相类似[3]。其中,经FPGA发出的信号 D0,SCLK0,/SYCN0,/LDC0连接至 ADuM1400的3.3 V 端,经过该芯片隔离后输出信号 DIN0、CLK0、NC0、LDAC0至后续电路,各4路信号分别相互隔离、互不干扰。其电路设计如图3所示。

图3 ADuM1400隔离芯片电路原理图

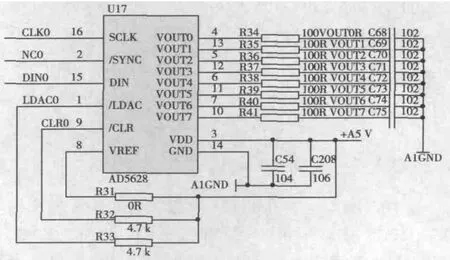

2.3.2 数模转换分析设计

DAC芯片是系统波形重构过程中的核心,理论上使用分辨率越高的DAC,输出波形的精度也就越高[4]。经计算,要实现系统精度指标必须选用至少8位分辨率的DAC,而实际的DAC输出必须考虑到DAC外围电路和外界条件所产生误差的影响,输出的信号无法达到DAC芯片所描述的精度[5],设计中选用12位分辨率的高精度AD5628芯片,并根据芯片性能要求,采用温漂系数为5 ppm/℃的配置电阻来提高输出信号的精度。

AD5628是低功耗、8通道、12位缓冲电压输出DAC,采用2.7~5.5 V单电源供电,内置一片内基准电压源,内部增益为2。上电时,片内基准电压源关闭,因而可以使用外部基准电压源。其中,内部基准电压源通过VHDL硬件语言编译操作实现使能。DAC的输入编码为二进制数。设计中采用内部基准电压源为2.5 V的芯片,并使用该芯片的内部基准电压,满量程可达到5 V,理论输出电压值的计算公式如式(1),电路原理图如图4所示。

式中:D是载入DAC寄存器的二进制编码的十进制等效值;N是分辨率。

图4 数模转换芯片电路原理图

本设计中 AD5628,D∈ (0,4 095),N=12。

假设上位机向AD5628发送命令为X“800”,对应十进制的值D=2 048,则输出的电压大小VOUT=2×2.5×=2.5 V 。

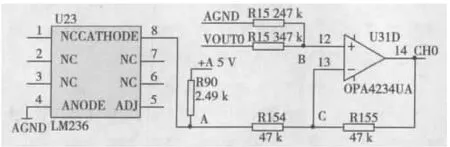

2.3.3 调理电路分析设计

根据数模转换芯片线性和运放芯片“轨对轨”特性,之前应用中线性芯片两端输出的模拟量精度相对较低,即0 V和5 V精度达不到设计要求。为解决该精度问题[6],采用偏置基准为2.5 V的稳压芯片LM236和运放芯片OPA4243来设计电路,如图5所示。VOUT0为AD5628所输出的0~5 V电压,A、B、C三点电压值设为VA、VB、VC,其中VA=2.5 V,根据集成运放的“虚短”和“虚断”特性,计算公式如下

即经偏置电路后,VCH0∈(-2.5 V,2.5 V)。

图5 偏置电路原理图

放大电路采用OPA4227运放芯片,该芯片工作模式为“轨对轨”,采用-9 V~9 V供电,放大倍数为A=1+,在实际电路中,选取R150=5.1 kΩ,R151=10 kΩ,使得放大倍数A≈3,保证A点输出电压VA∈(-7.5~7.5 V),达到幅值的放大要求。由于这样输出模拟量纹波较大,因此后面接RC滤波电路,提高信号精度。其电路设计如图6所示。

图6 放大电路原理图

3 D/A转换时序设计

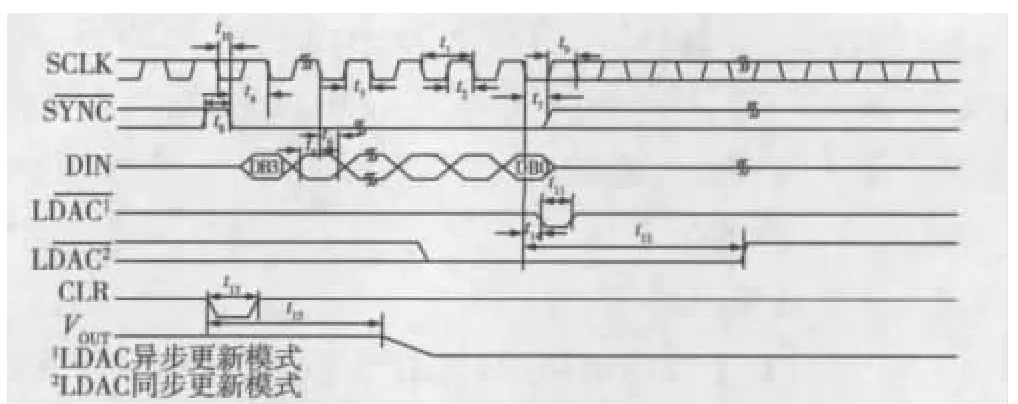

采用VHDL语言在FPGA内部实现对D/A转换的控制,AD5628接口采用3线串行接口(SYNC、SCLK和DIN),其典型写序列的时序图参见图7。串行时钟频率最高可以达到50 MHz,设计中FPGA晶振时钟频率采用40 MHz,因而AD5628能与其兼容。

当SYNC=“0”时,启动写序列;在SCLK脉冲的下降沿将DIN线的数据写入32位移位寄存器,在第32个时钟下降沿,最后一位数据被读入。在该阶段,SYNC线可以保持在低电平或置为高电平。但无论哪种情况,在下一个写序列之前必须保持SYNC至少15 ns的高电平,设计中等待了2个时钟(系统时钟为40 MHz),这样才能保证SYNC下降沿启动下一个写序列。

图7 AD5628串行写入操作

输入移位寄存器为32位宽(31~0)。对系统中使用的AD5628而言,(31~28)是无关位,程序中设为“0000”,(27~24)是命令位C3~C0(参见表1),可以看出,在往DAC中写入数据时,程序中应写为“0011”;(23~20)是4位DAC地址A3~A0,最后是12位数据字,用来控制D/A输出电压幅值的大小,该12位数据位在SCLK的第32个下降沿被送入DAC寄存器。

表1 命令定义

若现上位机向某寄存器发送X“A80”,则程序中C3~C0=0011,相应地址的12位数据为101010000000,从而通过式(1)计算出转换成模拟量的幅值。

4 关键技术实现

文中信号源实现的关键是对系统程控调幅的设计。以往设计中信号源主要是通过往寄存器中烧入相应幅值信息的抽样值,或在硬件嵌套多个DAC提供参考电压来完成。本文提出一种程控实现方法实现对幅值的控制。采用程控调幅的方法具有速度快、步进小、可扩展性高的优点,更适合多通道信号源的设计。上位机下发中低12 bit即为幅值程控系数,在FPGA内部调用IPCore,经减法器、乘法器和加法器后生成12 bit调制后数字量,输出至数模转换芯片AD5628。其示意图如图8所示。

图8 调幅设计示意图

5 测试结果

上位机开始界面上点击“系统复位”、“单机测试”后,在弹出的界面窗口有多路选择输出电压,默认取值为中间值,如图9a所示。使用高精度万用表进行多次测量,对模拟量进行标定后,保证上位机发送的命令使最终输出的电压值误差达到最小。

用示波器测量的纹波如图9b所示。系统上电后,不发送命令的情况下对系统进行纹波测试,将示波器耦合模式调为交流模式,所测纹波的峰峰值为84 mV,精度满足设计要求。

在上位机界面分别点击发送6 V和-6 V直流量,用示波器所测相应幅值的直流量波形如图9c、9d所示,用多功能万用表测量值分别为6.002 V和-5.998 V,完全满足了设计需求。

图9 测试结果(截图)

6 结论

本文以Xinlix公司Spartan-3系列的XC3S400和Analog Devices公司的 AD5628 为硬件平台,VB6.0、VC++为软件开发平台,将FPGA和PCI技术有机的结合起来,利用FPGA集成度高、速度快和现场可编程的优点,通过上位机对信号幅值进行调控,有序地实现了多路信号源系统的设计。实验结果证明该系统运行良好,信号源输出的信号具有高精度、稳定性好以及多路并行输出的优点。

[1]安震,张会新,卢一男,等.基于PCI总线与FPGA多通道模拟信号源的系统设计[J].计算机测量与控制,2012,20(9):2558-2560.

[2] PCI 9054 Date Book[EB/OL].[2013-09-20].http://wenku.baidu.com/link?url=e29UElfgITRgBHL5qX40lUmZ7FjVCFexYfmmfNbPGoa e-cVQfXgTsZTrPpPUE7MEWlGpbPIb8-69MkkG4UEeEnPWSHWC0dPZ pQxtew9Us-7.

[3]邸丽霞.基于FPGA的高速图像数据采集存储系统设计[J].电视技术,2013,37(13):49-52.

[4]胡小燕.基于PCI+FPGA的任意波形发生器的研究与设计[J].电子质量,2010(4):24-26.

[5]于晓光,张彦军.基于FPGA的数字量变换器的设计[J].通信技术,2010,43(1):203-204.

[6]王红亮,黄洋文.基于FPGA的可程控多路信号源设计[J].火力与指挥控制,2010,35(6):97.