一种DSP高可靠性快速数据传输方法的研究*

何航峰,郑步生

(南京航空航天大学电子信息工程学院,南京210016)

一种DSP高可靠性快速数据传输方法的研究*

何航峰,郑步生*

(南京航空航天大学电子信息工程学院,南京210016)

为了避免DSP串行数据传输容易出现数据不同步、误码率高的情况,介绍了一种以DSP为核心,通过FPGA/CPLD扩展外设,采取帧同步和CRC校验的数据传输方法。该设计在DSP数据传输硬件设计的基础上,依靠有限状态机帧同步法和按字节计算CRC,将两种方法相结合定义新的通信协议,将数据存放于所约定的数据帧中进行传输。测试结果表明该方法提高了整个DSP系统的效率、稳定性和安全性,适用于众多信息量大、高速数据传输的场合。

DSP;FPGA/CPLD;数据传输;CRC校验;帧同步

1 系统结构

图1 系统组成结构框图

从图1可以看出,DSP通过外部存储器接口EMIF与FPGA/CPLD相连,FPGA/CPLD再与串口控制芯片、AD芯片等外部芯片相连。通过配置EMIF和中断,达到了扩展DSP外部接口的功能;同时FPGA/CPLD又可以兼做数据预处理和缓存设置,从而能缓解DSP的压力[1,5]。

在软件运行上,DSP除了完成相关运算工作外,还要处理各种中断服务。若中断服务程序占用时间较长,在中断程序运行时又产生了新的中断,可能会造成数据的丢失。为了保证数据的可靠性和高速性,需要在通信过程中加入一种通信协议[4-6]。本文定义的通讯协议:将数据以数据帧传输,并在其中加入特点规则的同步和校验。图2所示的数据帧结构是本文所定义的帧结构,其中帧头是用于帧同步;帧长度和类型用于简单判断;校验采用CRC校验来判断数据是否正确。串口数据传输的可靠性主要依据帧头同步和CRC校验。

图2 数据帧结构

采用合适帧头同步方法和CRC校验算法,是保证数据可靠性和高速性的关键。下文将对这两种方法的选用进行分析探讨。

2 帧头同步研究

帧头一般是由一个或多个ASCⅡ字符组成,假定约定的帧头为两个字节——“0x11,0xBB”。在串口通信中,常用的帧同步方法有逐次比较法、FIFO队列法和有限状态机法。

2.1 逐次比较法

逐次比较法的原理就是将所需数据与约定数据逐一比较,它在编码、数据采集、数学等领域都有广泛应用。方法程序流程如图3所示。

图3 逐次比较法程序流程

逐次比较法所需代码量小,编程实现简单,可以简单扩展到多字节同步等。但是在串口数据传输量大、传输速率高的场合,容易出现同步耗时长、很难同步的情况。例如,串口数据接收队列为0x00、0x55、0x11、0x11、0xBB……,当比较第1个“0x11”时,该方法认为第1个接收字节正确,开始比较第2个接收的字节。第2个字节仍为“0x11”,发现不正确,必须等待新的字节重新比较第1个帧头,因此会导致帧头的第1个字节也没有同步上。事实上,前3个字节“0x00、0x55、0x11”为干扰,“0x11、0xBB”才是帧头。若同步帧头前干扰字节比较多,完成帧头同步所需时间也比较久。

该方法一般适用于以非中断方式接收串口数据,要求系统对实时性要求低,所传输的数据帧短的场合。

2.2 FIFO队列法

为了改进逐次比较法的缺点,可以进行双或多字节帧头比较。根据约定好的帧头长度,定义一个相同长度的全局字节数组,将数组看成一个FIFO队列,先进先出存放数据。本文所设计的硬件系统可以选择具有FIFO缓冲区的串口芯片或者在FPGA/CPLD建立FIFO缓冲区,可用于基于FIFO队列的帧同步方法。该方法的程序流程如图4所示。

图4 FIFO队列法程序流程

对于前面提到的队列0x00、0x55、0x11、0x11、0xBB……测试。帧同步队列中数据依次为:[0xFF、0xFF]→[0x00、0xFF]→[0x55、0x00]→[0x11、0x55]→[0x11、0x11]→[0xBB、0x11]。当检测出[Head2、Head1]=[0xBB、0x11],已经实现同步。

FIFO队列法在同步时间和准确性上比逐次比较法好,但是同步过程中需要进行大量的字节搬移,将占用大量内存,尤其是在中断时,服务程序将在搬运数据上耗费大量时间。

2.3 有限状态机法

该方法将数据的接收过程分为若干个状态:接收信息头Head1状态、接收信息头Head2状态、接收帧长度状态、接收数据类型状态、接收数据状态机及接收校验状态,状态转移图如图5所示。

图5 有限状态机转移图

对前面提到的队列 0x00、0x55、0x11、0x11、0xBB……测试。系统的接收状态依次为Head1→Head1→Head1→Head2→Head2→Length,此时已经是同步状态。同步后,程序按照协议开始依次接收数据帧长度、命令类型、数据和校验位。接收完后,重新设置系统接收状态为Head1。

由于采用了状态机和消息机制的结构,该设计方法可以快速有效的实现串口帧同步。该方法的程序编写结构清晰,后期也便于维护。而且,该方法的中断服务程序所需处理的工作量比较少,处理速度快,缓解了中断服务程序的压力。有限状态机法也是3种方法中更满足系统设计的需求。

3 CRC校验

循环冗余码校验 CRC(Cyclic Redundancy Check)编码简单、误判概率极低,被广泛的应用于控制及通信领域。在许多数据传输过程中,都需要这种方法对传输的数据进行校验。CRC计算可以依靠专用的硬件来实现,但对于应用DSP作控制或传输的系统,可以通过编程的方法完成编码过程,而无需外加硬件,实现更加灵活,减少硬件负担和成本[9]。

3.1 CRC校验原理

假设p位信息码为P(X),r位CRC码为R(X)。将信息码P(X)左移r位得到一个n=p+r的序列XrP(X),那么必然存在一个r位的多项式G(X),将XrP(X)模2除以G(X),得到的余数就是我们需要的r位CRC码R(X)。数据传输时,将R(X)加在P(X)后面进行传输,在接收端再次进行CRC校验,判断是否有误码。如式(1)所示,Q(X)为整数[11-12]。

生成步骤如下:

(1)将X的最高次幂为r的生成多项式G(X)转换成对应的r+1位二进制序列;

(2)将信息码左移r位,得到信息序列XrP(X);

(3)用生成多项式对信息序列进行模2除法,得到r位的余数;

(4)将于r位余数拼接到p位信息码后面,得到n=p+r的传输序列。

3.2 快速CRC算法

CRC校验的设计需要保证其在更短的时间完成更多的校验,尤其对于实时性要求高的场合,校验占用过多的时间和内存,将破坏系统数据交互的实时性,加重系统运算负担。为了提升DSP系统的CRC计算速率,合理利用DSP的内存。本文提出了一种按字节计算的快速CRC算法。

对于一个信息码P(X)可以表示为式(2),其中Pn为一个字节八位:

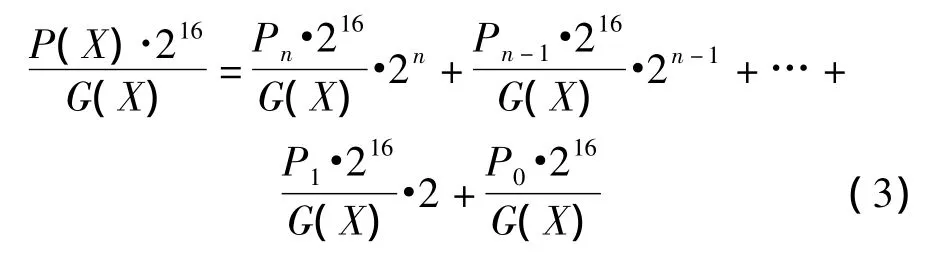

按照前面求该序列的CRC码方法,先左移16位,即乘以216,再除以多项式G(X),如式(3)所示:

设:

将式(4)代入(2)得到:

将Rn(X)分解成高八位RnH8(X)和第八位RnL8(X),式子如下:

Rn(X)·28=[RnH9(X)·28+RnL8(X)]·28(6)将式(6)代入式(5)得:

再设

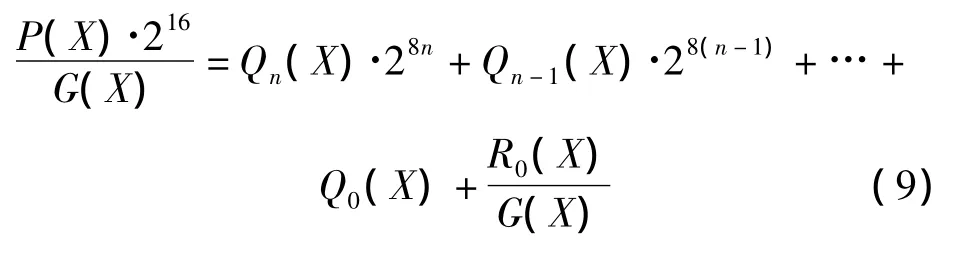

将式(8)代入式(7),通过类推整理后可得式(9),其中R0(X)便是要求的余数:

通过(9)可以得出结论:计算本字节后的CRC码等于上一字节余式CRC码的低8位左移8位,再加上上一字节CRC右移8位和本字节之和所求得的CRC码。根据该结论,只要计算出一个字节,八位二进制序列的CRC码,并将它放到表格里面,在计算CRC码时便可以方便查询。八位二进制序列的CRC码为256个,共占用内存512 byte。

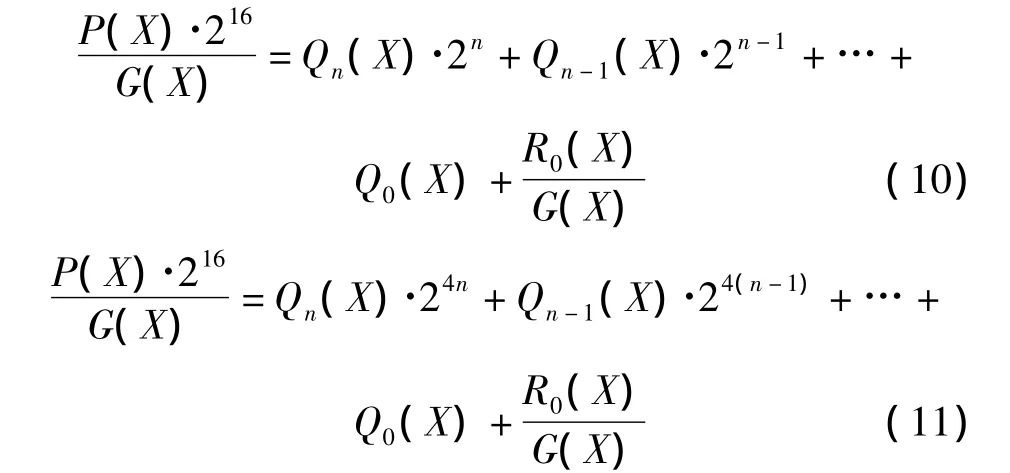

传统的CRC算法多采用按位计算CRC和半字节计算CRC。式(10)为按位计算CRC整理所得式子,式(11)为按半字节计算CRC整理所得式子。

根据(10),对于按位计算CRC可以得出结论:计算本位后的CRC码等于上一位CRC码乘以2后除以多项式,所得的余数再加上本位值除以多项式所得的余数。

根据式(11),对于按半字节计算CRC可以得出结论:计算本字节后的CRC码等于上一字节CRC码的低12位左移4位后,再加上上一字节余式CRC右移4位和本字节之和后所得的CRC码。通过这种方法,求解一长序列的CRC码,其实就是求解4位二进制序列的CRC码。4位二进制序列的CRC码为16个,所生成的表格将占用32 byte的内存。

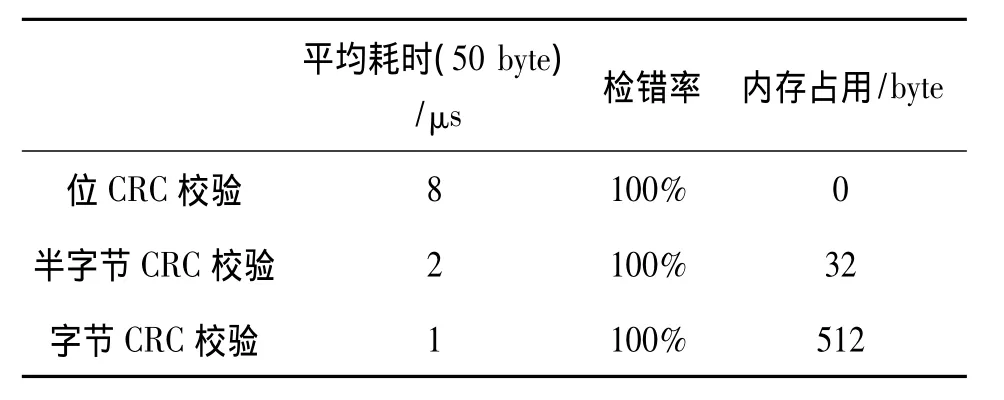

上述3种计算CRC校验的方法,按位计算CRC代码简单,所占用的内存比较少。但同时也带来了速度问题,一位一位计算CRC,在高速通信或者是信息码较长的情况下,占用了处理器的太多时间。该算法比较适用于内存小、对时间要求不高的系统。按半字节计算CRC内存占用32 byte,速度较按位计算CRC有明显的提高。半字节计算CRC比较适用于小内存的系统,它既不会占用太多内存,速度上也有显著的提高。

对于DSP系统,系统本身的内存比较大,数据的传输量也比较大。上面的两种方法在速度上未能达到数据高速传输的要求,而且对系统的内存资源利用率也不高。按字节计算CRC码在所占用512 byte内存,可以满足DSP的内存需求。在速度上,该方法较其他两种方法更加快速,满足了高速通信的要求。

4 方案实现

本文讨论的高可靠性数据传输方法在DSP上进行了实现和测试。DSP处理芯片选用TMS320VC5509A,将其工作频率设置在100 MHz; CPLD选用xilinx的XA2C256,工作频率设置在144 MHz,通过DSP的外部存储器接口EMIF和中断与CPLD连接,以此来扩展DSP的外部接口。将串口控制芯片、AD转换芯片等通过CPLD与DSP进行连接。在CPLD中设立了FIFO空间用于暂时存放数据,并通过CPLD对数据进行预处理,包括有限状态机法帧头同步等。在校验上采用按字节CRC校验,利用DSP软件实现。

测试分为2种:帧头同步测试和CRC校验测试。帧头同步测试:随机产生1 byte~10 byte的帧头干扰数据,加在约定的帧头前,通过串口传输到平台测试帧头同步。CRC校验测试:根据本文定义的数据帧,产生50 byte大小的数据帧,将其分为正确数据帧和人为错误数据帧,输入到DSP中进行测试。

在帧头同步测试上,应用有限状态机法,程序所需处理的工作量少,经过多次同步试验,相对于另两种帧头同步方法未出现同步错误,平均耗时短。

CRC校验测试结果如表1所示。按字节计算CRC校验在速度上明显优于其他两种算法,DSP也能够满足该算法占用512 byte的内存。针对不同的微处理器和系统,可以选择不同的校验算法来满足内存和速度的需求。

表1 CRC校验测试结果

在本文测试的硬件架构下对于按字节CRC校验,可以理解为以下几步:

(1)读取FIFO中的数据;

(2)查找输入字节对应的CRC码;

(3)将新输入字节的CRC码与原有的CRC码相加。

对于C5X系列,一般2个时钟周期可以完成一个字节的CRC校验。对于C6X系列,采用Galois域乘法指令,仅需1个时钟周期便可以完成一个字节的CRC校验[9-10]。

5 结束语

本文中讨论了一种DSP的高可靠性快速数据传输方法,硬件采用DSP扩展FPGA/CPLD实现。通过这一硬件方案,解决了DSP本身串口数量少的问题,利用中断查询等方法可以扩展到6个~8个串口;像AD等高速数据转换器可以通过FPGA/ CPLD与DSP进行连接,解决数据宽度时钟等不匹配问题;FPGA/CPLD可以对数据进行预处理,缓解DSP的运算压力。

通过有限状态机法同步和按字节计算CRC法的通信协议,避免了数据传输量大、高速情况下容易出线误码、干扰码的情况,确保了数据的可靠性。该协议保证了数据传输的高速率,满足高速传输系统的传输要求,并且能够保证传输的质量。将该方法稍作修改移植,可以应用于不同的系统。

[1]王永成,党源源,徐抒岩,等.基于CPLD实现DSP的UART设计[J].电子器件,2008,31(3):1067-1072.

[2]陈文鹤,毕欣,曹云侠,等.FPGA与DSP的雷达数据传输接口设计[J].控制工程,2011,18(S1):60-62.

[3]李乐,熊志辉,王斌,等.DSP+FPGA折反射全景视频处理系统中双核高速数据通信[J].电子与信息学报,2010,32(3):649-654.

[4]马秀娟,考丽,赵国良.基于FPGA和DSP的高速数据采集实时处理系统的设计[J].电子器件,2007,30(3):1009-1013.

[5]梁迅,熊水东,姚琼.基于TMS320C6000 DSP的FIFO—网络数据传输[J].电子器件,2008,31(3):1057-1060.

[6]冯华亮.循环冗余校验在TMS320C64x+DSP上的高效实现[J].电子技术应用,2008(7):38-40.

[7]罗友宝,李小文,谷向阳.LTE系统的CRC校验算法研究及DSP实现[J].集成电路应用,2010,36(9):71-73.

[8]汪春梅,孙洪波.TMS320C55x DSP原理及应用[M].电子工业出版社,2011.

[9]吕梅波,张科,赵军民,等.在DSP中实现高效的CRC算法[J].弹箭与制导学报,2005,25(3):225-227.

[10]成兰,崔亚量,田原.一种基于TMS320C55x DSP的UART通信设计[J].微计算机信息,2008,24(2):153-155.

[11]Campobello G,Patane G.Parallel CRC Realization[J].IEEE Transaction on Computers,2003,52(10):1312-1319.

[12]Lrvin D R.Cyclic Redundancy Checks with Factorable Generator[J].IEEE.Proc Commun,2003,150(1):179-191.

[13]Chen Z.A Method for DSPAsynchronous Serial Port Expansion Based on TL16C752B[C]//Proceedings of2011 International Conference on Business Management and Electronic Information,2011.

[14]Instruments T.TMS320VC5509A Fixed-Point Digital Signal Processer[M].2008.

[15]胡焰胜,王多,李天阳,等.一种用于DSP芯片的串行通信接口设计[J].计算机工程,2012,38(23):236-239.

[16]Zhangqi X,Kechu Y,Zengji L.A Universal Algorithm for Parallel CRC Computation and Its Implementation[J].Journal of Electronics,2006(4):528-531.

Study on High-Reliability and High-Speed Data Transm ission on DSP*

HE Hangfeng,ZHENG Busheng*

(College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

Asynchronous data and high error rate always happen in DSP data transmission.To avoid those problems,data transmission method is designed based on DSP,through FPGA/CPLD expansion peripherals,and taken frame synchronization and CRC.Based on a DSP hardware design,a new communication protocol is defined which depends on finite state frame synchronization and calculated by byte CRC.The data stores in the data frame to transport. Through some tests,themethod can improve the efficiency,stability,security of the DSP system.It also adapts the occasionswhich large amount and high-speed data transfer.

DSP;FPGA/CPLD;data transmission;CRC;communication protocol

随着科技的发展、应用环境复杂化,对数字信号处理系统的要求也越来越高。特别是在雷达、通信等大型数据处理系统中,数据传输量大、处理流程复杂、实时性及传输速率要求高[1]。传统的由单独DSP构成的数字信号处理系统,其自带的串口数量有限,难以满足与多个外设同时进行数据传输的需要[2];未经规范的串口数据传输,容易出现干扰码或产生误码,从而影响系统的可靠性[9]。因此,对DSP系统与外设之间在数据传输的高速且可靠性方面的研究是非常重要的。本文在 DSP与 FPGA/ CPLD硬件架构的基础上,通过帧头同步和CRC校验,来保证数据传输的高速且可靠。

TN913 文献标识码:A 文章编号:1005-9490(2014)01-0157-05

DSP系统与外部设备进行信息交流时,串口通信是最常用的通讯方式[1],但存在下几个问题:(1)串口数量,一般DSP自带的串口为2个~3个,但是现在外设越来越多,往往要求系统拥有3个以上串口;(2)DSP系统通常会遇到高速的数据,但是大部分的高速数据转换器不能直接与DSP相互连接; (3)一些数据的预处理会增加DSP的负担[2-4]。

为了克服上述问题,可在硬件上通过 FPGA/ CPLD来扩展DSP的外设,而在软件上重新定义新的通信协议。本系统组成结构如图1所示。

项目来源:江苏高校优势学科建设工程项目

2013-04-23修改日期:2013-06-04

EEACC:6210

10.3969/j.issn.1005-9490.2014.01.038

何航峰(1988-),男,汉族,浙江慈溪人,南京航空航天大学电子信息工程学院研究生,硕士,主要研究方向为电路与系统,172849190@qq.com;

郑步生(1961-),男,汉族,江苏滨海人,南京航空航天大学电子信息工程学院,副教授,主要研究领域为电路与系统、射频仿真等,bszheng@nuaa.edu.cn。