基于MCU和CPLD的微型动态应力存储测试系统

张海龙,马铁华*,谢 锐,刘双红

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.中北大学电子测试技术国家重点实验室,太原030051)

基于MCU和CPLD的微型动态应力存储测试系统

张海龙1,2,马铁华1,2*,谢 锐1,2,刘双红1,2

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.中北大学电子测试技术国家重点实验室,太原030051)

为了解决车辆履带上的动态应变压力测试问题,设计了一套微型应力存储测试系统。对于应变压力传感器采用电桥法测试应力并应用存储测试技术设计了整套测试系统。使用单片机和CPLD作为系统的主控芯片完成系统的微功耗设计,并设计了模拟电路部分和数字电路部分。经过冲击梁实验表明此测试系统和理论计算的误差在7%以下,可以对车辆履带上的应力进行测量。

应力;存储测试;微功耗;冲击粱

在现代军事、农业和建筑业等领域中,履带车辆凭借其良好的性能发挥着十分重要的作用[1]。但是其工作环境恶劣,经常受到冲击和振动,一些关重部件失效形式表现为疲劳断裂[2]。主动轮为整车提供牵引力和制动力,承受随机交变载荷,对其受力动态变化的过程的研究一直是业界的难点和热点[3]。

1 应变测试基本原理

应力测试系统使用电阻应变片来测量车辆运行中的动态应变。构件上的应变片与测试系统中电阻组成电桥,构件发生形变时,引起桥臂上应变片阻值发生变化,根据胡克定律,通过测试出的构件表面测点的应变,求出测点的应力[4]。

本设计的测量电路采用惠斯登电桥,将应变片的阻值变化转化为电压或电流信号。基本电路如图1所示。

图1 惠斯登电桥测量原理

惠斯登电桥由4个电阻构成4个桥臂,A端和C端介入电源U,B端和D端为输出端。

对电路进行分析,可得出:

其平衡条件为R1·R4=R2·R3,当电桥平衡时,桥路输出电压为零,电桥得到平衡。

2 存储测试方法

单独的单片机控制难以实现高速运行,而单独采用CPLD控制功耗较大且逻辑复杂。在实现高速数据采样和大容量数据存储的功能,同时控制功耗和体积的前提下[5]。

本文设计的存储测试方法采用单片机与CPLD共同控制的模式,使用两片闪存交替工作组成数据存储器。单片机控制测试系统工作状态的转换和发出对闪存进行写入、读取、擦除操作的命令,CPLD控制高速数据采样转换和转换完毕后数据的缓存。这样的设计充分利用了单片机功耗低、逻辑简单,CPLD速度高的优点,提高了测试系统的功能性和稳定性[6]。

2.1 随机触发测试技术

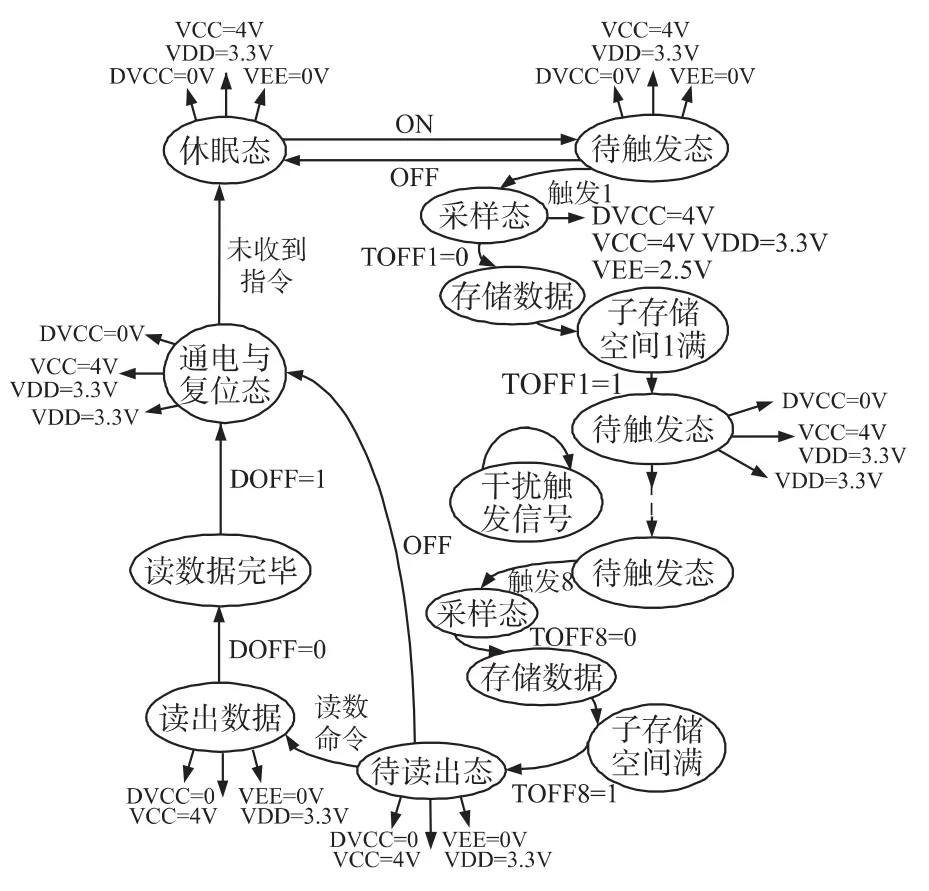

测试系统采用的随机触发采样模式,随机触发采样设计为8次随机触发,且将Flash的存储区域等分为8个容量相等子存储区域,每触发一次,就存储一个子存储区域,具体随机触发采样状态如图2所示。

图2 随机触发采样状态图

多路待测信号输入到测试系统的输入信号端,应力测试系统由休眠态进入待触发态,等待触发信号的到来。系统进入待触发态后,每收到一个触发信号,测试系统的AD根据设计的采样频率进行数据转换,将每次转换的数字量写入存储器并保存,当子存储空间存储满后,输出第一次触发采样完毕信号TOFF1。当系统查询到TOFF1信号为1时,停止采样,等待下一次触发信号的到来。以此类推,直到第8次触发的子存储空间满后,输出第8次触发采样完毕信号TOFF8。当系统查询到TOFF8信号为1时,停止采样,此时随机触发采样过程全部完毕,应变测试系统进入待读状态。

2.2 大容量存储测试技术

存储芯片采用两片三星公司生产的NAND型闪存存储器K9F4G08OM,单片容量为512MB。NADA结构闪存的特点是:以页为单位进行读和编程操作,以块为单位进行擦除操作[7],对一页(2 kbyte)数据编程进入非易失介质的典型时间为200μs,擦除一块(128 kbyte)的时间为1.5 ms。数据、地址、命令采用同一总线,芯片使用引脚少。

由于闪存存在较长的页编程时间,编程时无法对其进行操作,为了在高速数据转换情况下不丢失数据,并进一步提高存储容量,采用两片闪存芯片交替工作组成数据存储器,总存储容量扩大为1 Gbyte。

2.3 多通道测试技术

测试系统需要4通道同时采集,模拟量进行1~4通道的切换,采用4通道模拟开关MAX4634,4路模拟信号每路采样频率为25 kHz,AD的采样频率为100 kHz,对应每个周期的时间为10μs。

3 系统硬件设计

本测试系统主要由以下几部分组成:应变片,信号调理电路,电源管理电路,AD转换器与存储电路,控制电路,通信设备和计算机等。测试系统原理框图如图3所示。

图3 测试系统原理框图

3.1 电桥调平电路

在实际测量中,引线电阻不平衡、应变计阻值误差以及实验环境中温度的变化等因素都会引起桥路微小的失衡,这些会造成桥路不平衡的因素会使应变测试电路在没有应变输入时对应的输出量远远偏离零位,放大器本身又有零漂,这使得系统无法正常测试。因此,在模拟电路中设计了电桥调节平衡这一环节。

本系统中电桥调节芯片选用标称值为10 kΩ的X9C103数字电位器。X9C103内部的数据电路通过开关控制中间节点在电阻网络中的连接位置来改变电阻值,测试系统通过单片机对其输入端口INC、U/D的值来控制电位器的移动和移动的方向。

3.2 信号调理电路

应变片产生的电压差将由INA128仪表放大器进行放大,放大倍数计算公式为:G=1+(50 kΩ/RG)。

对经仪表放大器放大后的被测信号进行滤波处理。系统采用性能高、功耗低运放OPA4340进行低通滤波电路设计。如图所示,图4为滤波器电路图。

图4 OPA2340二阶低通滤波器

3.3 A/D转换模块设计

测试系统选用了高速、低功耗、逐次逼近的12 bit AD转换器AD7492.它可在2.7 V~5.25 V的电压下工作,其数据通过率高达1 Msample/s。它内含一个低噪声、宽频带的跟踪/保持放大器,它可以处理高达10 MHz的宽频信号。编程设置它的采样频率为500 kHz。使用CPLD对外部晶振分频后的信号作为AD转换的时钟,这样得到的信号稳定且占用芯片资源少。

3.4 接口电路设计

测试系统读数设计为高速读数。采用并行转USB的方式将测试系统中数据并行输出到上位机中,速度快且数据传输准确。

设计UART0口的 P3.4和 P3.5与上位机的TXD、RXD连接,实现测试系统与上位机读数中断信号的传输。高速读数时将数据口、控制端与上位机的端口一一对应连接,完成数据的并行输出。

4 系统软件设计

4.1 单片机软件设计

测试系统选用AVR系列单片机ATmega8515,利用汇编语言编写。测试系统软件方案设计主要由控制模块对各部分模块的控制程序组成,其中包括对信号调理模块的控制,应变信号的采集时序,对Flash的各项操作及电源管理设计等。由于测试需求,还设计了软件的低功耗模式和中断机制。

系统程序总体构架如图5所示。测试系统上电后先进行系统初始化,初始化完毕后系统进入低功耗状态,在极功耗下等待中断信号的到来。中断信号发生后,系统将响应中断信号,退出低功耗状态,进入相应中断,发生相应中断的操作。系统一共设置了3个中断,中断1是写中断,中断2是读中断,中断3是擦除中断。

图5 单片机程序总体构架

4.2 CPLD软件设计

CPLD采用XLINX系列芯片XCR3128,CPLD控制高速数据采样转换和转换完毕后数据的缓存。AD输出为12 bit,闪存的数据线为8 bit,转换得到的数据先进入CPLD转化为2组8 bit数据,使数据位数匹配

对A片发出命令后,A片进行编程时对B片写入数据,反之相同,这样提高了测试系统的数据处理速度,满足了测试要求。

图6 CPLD的状态关系

4.3 上位机软件的设计

上位机采用VB语言进行编程,利用测试系统要求,设计了内部1 024 Mbit数据的读取程序。读数时显示界面如图7所示。

图7 读数时显示界面

点击图中装置读数,显示读数窗口,由读数要求灵活选择读数长度,选择读数范围为1~1 024。设置界面其他参数按照需要填写。点击开始读数时,系统将对所选读数长度内芯片的数据进行读数。

5 实验测试及结果

测试装置采用JZT-5型多功能电子式力学综合实验台的冲击梁装置,冲击梁装置配置质量块,使质量块自由下落,产生冲击力[8],把应变片贴在冲击粱上A点处,通过测试系统,测试出瞬态动应变,求出其瞬态动应力。

根据能量守恒定律计算相应载荷动荷系数,将结构在可类比静载荷作用下的最大应力乘以动荷系数,得到结构中的最大冲击应力。

图8 冲击杆

实验参数为:应变片电阻R=120,冲击质量块的质量M=200 g,等强度梁的长度L=300 mm,宽度h=15 mm,厚度b=4 mm,应变片距固定点的距离d=100 mm,支座距固定点的距离l=250 mm,弹性模量E=200 GPa,计算结果如表1所示。

表1 计算结果

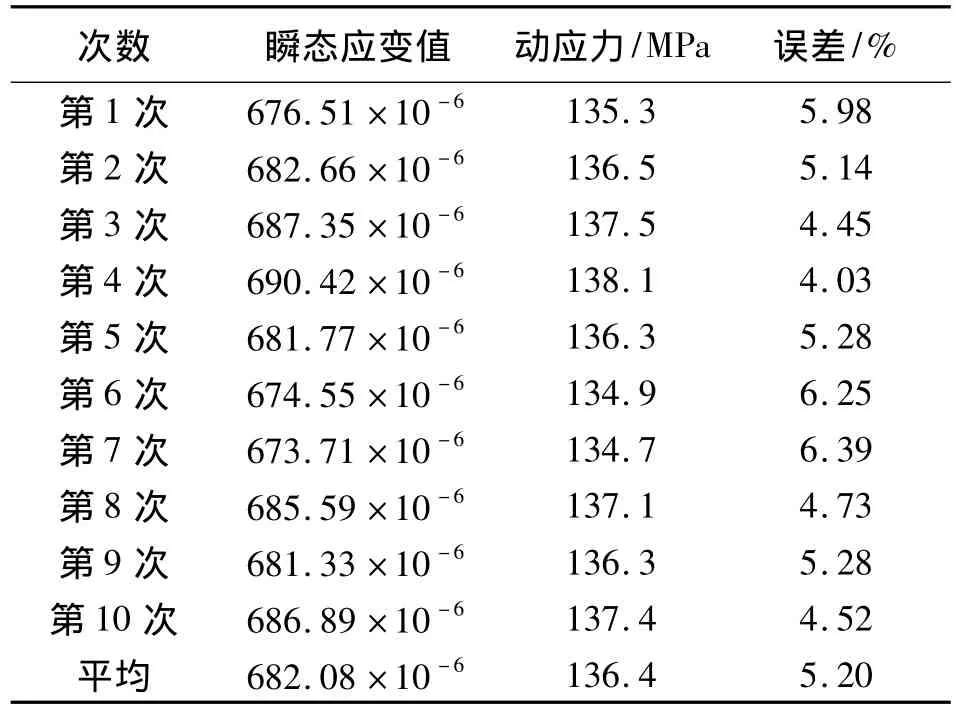

测试系统的实际测量值和理论计算值的误差结果如表2所示。

表2 实际测量值和理论计算值的误差结果

6 结论

本文完成了对动态应力测试系统的软硬件设计,对测试系统进行实验和误差分析,验证了其合理性。与传统测试系统相比,动态应力测试系统具有体积小,功耗低,稳定性高,抗干扰性强的优点,可实时完成对履带车辆主动轮的应力测试,特别适宜于恶劣环境下试验场合。

[1]蔺红军.履带车辆传动系测试系统研究[D].长春:吉林大学,2009.

[2]易当祥,刘春和,吕国志.自行火炮行动系统关重件的疲劳寿命仿真[J].兵工学报2007,28(2):138-143.

[3]田政,陈兵,尹忠俊,等.高速履带车辆主动轮动态应力仿真分析研究[J].计算机仿真,2011,28(11):328-331.

[4]张浩茹,谢锐,崔冬梅.基于FPGA的应力应变测试系统设计[J].测试技术学报,2012,26(2):158-161.

[5]王代华,宋林丽,张志杰.基于ICP传感器的存储式冲击波超压测试系统[J].传感技术学报,2012,25(4):478-482.

[6]陆从青,吴建辉.基于CPLD的高分辨率AD转换电路设计[J].电子器件,2010,33(1):62-66.

[7]谢锐,马铁华,裴东兴.基于闪存的引信电池大容量存储测试方法[J].探测与控制学报,2010,32(4):34-37.

[8]谢占魁,李艳辉,谢锐.冲击动应力实验装置研制[J].中北大学学报(自然科学版),2007,28:35-37.

M icro Dynam ic Stress Storage Measurement System Based on MCU and CPLD

ZHANG Hailong1,2,MA Tiehua1,2*,XIE Rui1,2,LIU Shuanghong1,2

(1.Key Laboratory of Instrumentation Science and Dynamic Measurement,North University of China,Taiyuan 030051,China; 2.Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

A stress storagemicrosystem is introduced to slove the problem of Vehicle Track dynamic stressmeasurement.The bridgemethod is used to test stress signal collected by a strain type pressure transducer and storage testing technology is designed in thismeasurement system.With low loss MCU and CPLD asmain chips low-power of the control system is realized.Analog circuit and digital circuits are designed,The cantilever-beam impact experiment show that experimental results differ,from theoritical calculation by less than 7%.So,this system can be adopted in stressmeasurements of Vehicle track.

stress;memory test;micropower;shock beam

10.3969/j.issn.1005-9490.2014.01.029

TM 93 文献标识码:A 文章编号:1005-9490(2014)01-0123-04

2013-05-21修改日期:2013-06-14

EEACC:7320G

马铁华(1964-)男,教授,博士生导师。1996年获哈尔滨工业大学工学博士学位1999年北京理工大学博士后出站。2002年美国路易斯安那州立大学高级访问学者。现任中北大学信息与通信学院科研副院长、电子测试技术国防科技重点实验室副主任。

张海龙(1988-),男,山西临汾人,中北大学信息与通信工程学院硕士研究生,主要研究方向动态测试,85468214 @qq.com;