基于FPGA和DDS的质子同步加速器共振慢引出信号源设计

童 金 谷 鸣 袁启兵 刘永芳

1(中国科学院上海应用物理研究所 嘉定园区 上海 201800)

2(中国科学院大学 北京 100049)

质子束流在人体组织内的剂量分布呈现 Bragg峰特性,这比传统意义上的利用 X或g射线治疗体内癌症细胞具有更少的正常肌体损伤[1],近 20年来,质子治疗技术在发达国家发展迅速。上海联合投资有限公司、中国科学院上海应用物理研究所及上海瑞金医院正联合推进国内首台质子治疗装置的研制工作。本文重点关注装置中同步加速器驱动信号源产生机制。

从同步加速器存储环中引出用于癌症治疗的质子束流主要有两种方法:一是保持质子束流运行状态不变,逐步缩小由加速器lattice结构决定的稳定区域,使束流越出稳定边界,从而进入共振态;二是保持同步加速器的lattice参数不变,即加速器的稳定区域不变,改变束流运行状态tune值,实现共振。两种情况下的粒子进入共振态以后,其振幅均呈指数式增长,当振幅达到一定值就可以被切割器分离引出[2]。

射频横向激励引出是一种典型的改变束流运行状态实现慢引出的方式,国内外的应用研究在不断发展完善。上海质子治疗装置也采用射频横向激励技术用于质子束流的慢引出,本文工作主要就是围绕该激励信号发生器的研制展开。

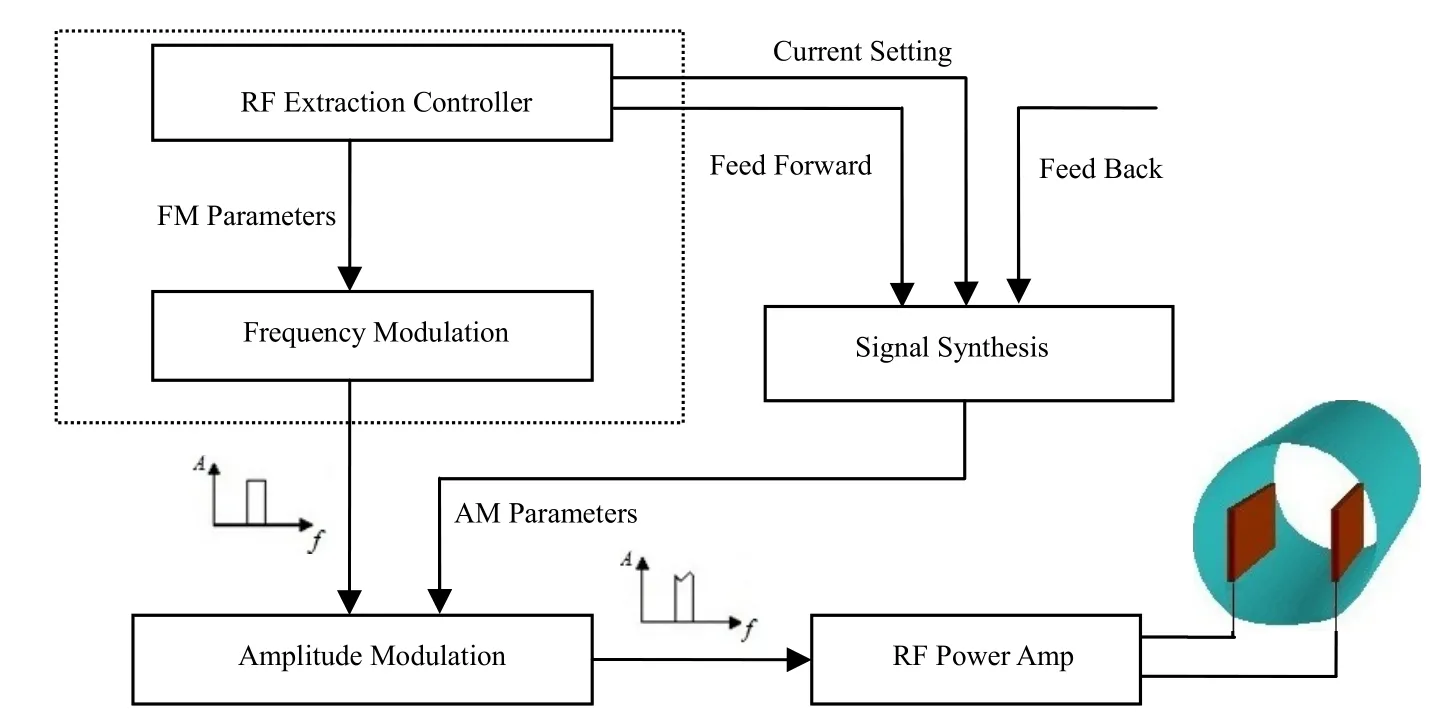

事实上,射频横向激励信号应设计为对应激励频率的调频调幅电场。调频的作用是使得储存环中质子受到的影响各有差异,使得质子群尽量均匀地进入共振态,起到对稳定区内质子工作点的涂抹作用,改善溢出束流的微观时间结构;调幅的作用是调节引出束流的宏观流强,提供流强的设定、前馈和反馈等稳流通道[3]。一定范围内,电场峰值越大则引出束流越强。引出系统的设计框图如图1所示。

根据上海质子治疗装置同步加速器物理设计参数,加速器环周长R为28.4 m,注入能量为7 MeV,引出能量范围为 70−250 MeV,引出工作点 tune=[1.663 0, 1.394 0],共振工作点ν=5/3,回旋频率frev为3.175−4.030 MHz[4]。射频横向激励信号频率和调制宽度按照如下关系变化:横向激励频率fk=0.663×frev=(2.105−2.672) MHz,其中,0.663为引出工作点横向分量的小数部分。

储存束流有一定的能散(Dp/p),即质子有一定的betatron频率分布。粒子从稳定区中心扩散到稳定区边缘,betatron频率也随着改变。激励频率需覆盖储存粒子的betatron频率到共振频率的范围,进而驱使稳定区内的粒子振幅增大进入共振状态引出,因此横向激励频率需满足一定的调制带宽。

激 励 频 率 调 制 带 宽 Δfk≈0.0036×frev=11.43−14.51 kHz,其中,0.003 6为共振工作点与引出工作点横向分量差值。

图1 射频横向激励信号系统设计框图Fig.1 Block diagram of the RF slow_extraction signal.

本文重点关注激励频率信号的发生方法与具体实现。具体来说,是要产生中心频率(MHz量级)和带宽(kHz量级)均在线可调的信号源作为激励信号。上海质子装置设计采用在设定带宽内频率随机变化的信号作为激励源。

1 质子同步加速器共振慢引出信号源方案选择

前文已经确定了激励信号的调频部分参数,回归到电子学,需要研制能产生满足条件的信号发生平台,首先需要确定的是信号源系统的方案选择。

实施乡村振兴战略,是党中央深刻把握世情党情国情农情,着眼于党和国家事业全局,着眼于决胜全面小康、建设社会主义现代化强国作出的重大战略决策。这是因为在这一伟大跨越过程中,最艰巨最繁重的任务在农村,最广泛最深厚的基础在农村,最大的潜力和后劲也在农村。要解决社会主要矛盾、实现“两个一百年”奋斗目标,实现全体人民共同富裕,必然要将乡村振兴落到实处。

1.1 基于压频转换器件的信号源方案

首先考虑压控晶体振荡器VCXO、压控振荡器VCO及 V/F电压频率转换器等模拟压频转换器件用于频率信号合成,但这些方案存在模块众多且多为模拟电路,易受干扰,系统精度不易控,频偏较大等突出问题。

1.2 基于直接数字频率合成器的信号源方案

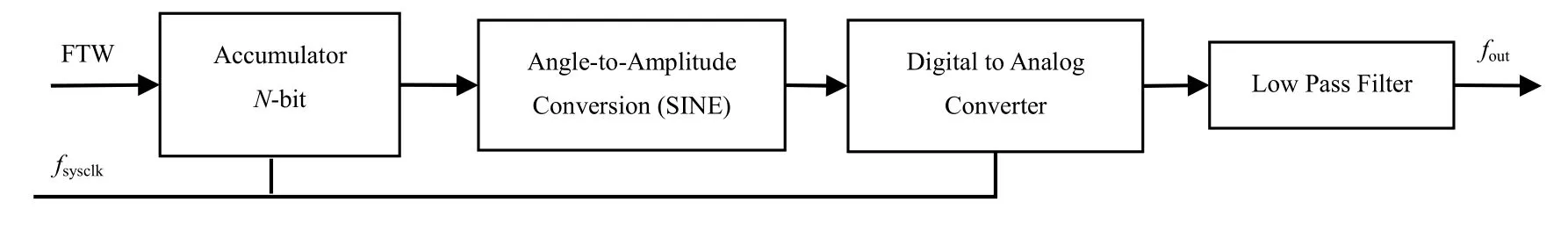

考虑到模拟调制方案中存在诸多弊端,采用直接数字频率合成技术用于信号源合成。这是一种全数字化方式,直接数字频率合成器(Direct Digital Synthesizer, DDS)的原理框图如图2所示。

图2 DDS原理框图Fig.2 Theoretical diagram of direct digital frequency synthesis.

图2 中相位累加器(Accumulator)可在每个时钟上升沿将频率控制字决定的相位增量累加一次,正弦查询表用于实现从相位累加器输出的相位值到正弦幅度值的转换,后续 DAC将数字量化正弦幅度值转变为模拟量,最后由低通滤波器输出纯净的正弦信号。图2中,fout为输出信号的频率,fsysclk为系统时钟频率,N为累加器的位数,FTW (frequency turn word)是频率控制字。

一般情况下有:

当FTW取1时:

为该DDS的频率分辨率。当fsysclk为100 MHz且累加器位数为32位时,分辨率为0.023 3 Hz,可见频率精度很高。

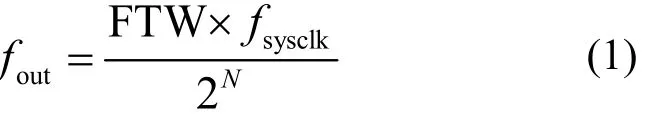

图3展示的是基于FPGA和DDS的信号源系统方案。FPGA对DDS配置控制高精度频率信号输出;同时,FPGA内部PLL生成高稳定度参考频率提供给DDS作为时钟频率。随机信号的产生是为了保证频率变化的随机性。该方案的优点在于 FPGA编程即可灵活实现诸如锯齿波调制、正弦波调制等多种调制方式且DDS输出频率精度很高。缺点在于DDS合成需求频谱成分时会产生很多高频镜像谐波干扰[5],必须设计相应的低通滤波器予以阻隔。

图3 基于直接数字频率合成器的频率调制方案Fig.3 Scheme based on direct digital frequency synthesis.

2 基于DDS的信号发生

图3方案中,FPGA用于对DDS模块的控制和配置,而DDS模块则用于产生高精度的频率信号。考虑到在板资源及接口拓展等方面的因素,FPGA开发板选择Altera公司的DE2-115,其核心芯片为Cyclone IV系列的 EP4CE115F29,主时钟为50MHz;DDS则选用ADI公司的直接数字频率合成器评估板AD9910/PCBZ。

2.1 FPGA与DDS板间通信控制

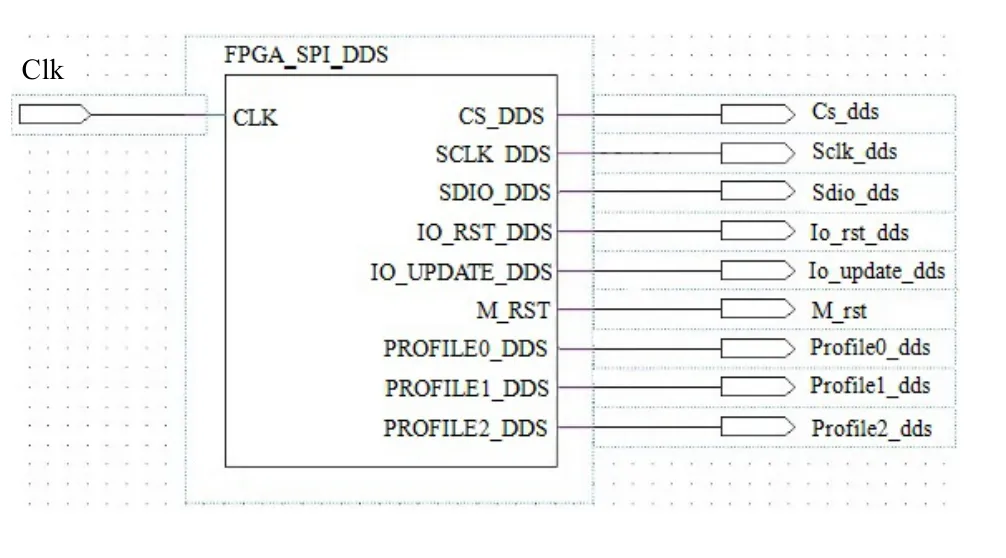

AD9910确定选取单频调制模式,且两板之间采用SPI通信协议进行通信[6]。DDS开发板中有SPI通信接口,FPGA开发板可用GPIO口模拟SPI通信口。

AD9910串行端口是一种灵活的同步串行通讯端口。此接口可进行读/写操作,访问所有AD9910配置寄存器。我们选用简便的2线SPI通信模式,仅需设置AD9910中地址为0X00的控制功能寄存器1(CFR1)的bit1位为0即可。其工作时序如图4所示。

图4 FPGA与DDS板间通讯时序Fig.4 Time sequence for communication between FPGA and DDS.

选定DDS的外部参考频率fsysclk为100 MHz,确定FPGA与DDS的通信控制流程如下所述:

(1) 首先对 DDS初始化,M_RST高电平主机复位将所有寄存器恢复默认值;然后设置 Profile 0−2为000选定单频模式下的profile0。

(2) CS使能令串口传输端口有效,设置CFR1为0X0041_0000,即令反SINC滤波器有效和选择DDS正弦输出,同时配置SDIO引脚为双向操作且串行I/O端口为MSB格式优先。

(3) 根据式(1)中输出频率与系统时钟频率及频率控制字的关系,推算出输出2 MHz正弦信号对应的频率控制字为0X 051EB852;以此类推,可以推算出其他频率点所对应的频率控制字;将不同的频率控制字依次写入串行端口缓冲器。

(4) 利用 IO_UPDATE信号将当次所写频率控制字推送至有效寄存器,若已完成所有写操作,退出返回;否则,进入(3)继续执行。

按照此工作流程,在Quartus II编程环境中,结合有限状态机思想,利用Verilog HDL语言编写软件代码,调试成功并定义好引脚文件后,下载至FPGA开发板运行,生成的模块设计文件如图5。

图5 DDS控制器的模块化框图Fig.5 Block design file of the DDS controller.

2.2 带限随机信号的生成与应用

方案中涉及到随机信号生成的问题,这主要是因为规则频率扫描和多路规则频率合成激励引出时,均会存在一个固有的干扰频率[3],而采用伪随机信号可以消除这种干扰。系统输出频率点虽在一定范围内随机变化,但其频率变化不能太快,应尽可能“柔和”,保证在1 kHz频带范围内。一个高斯白噪声经过1 kHz截止频率的数字低通滤波器(双线性Z变换)后的频谱变得平滑。实际编程中采用的是用伪随机序列代替高斯噪声,均值滤波简化替代数字低通滤波器。

2.3 输出信号平滑滤波

DDS输出有高频镜像谐波且频率变化容易产生高频干扰,所以AD9910/PCBZ开发板信号输出通道设计有截止频率为400 MHz的7阶p型巴特沃斯低通滤波器。但本系统涉及的最高频率仅为2.67MHz,远低于原设计截止频率值。为了更精确地获得输出信号,我们重新设计了 AD9910/PCBZ开发板上无源低通滤波电路参数,使其3 dB截止频率为6 MHz,使输出端口的谐波成分得到最大程度的抑制从而保证信号质量。

2.4 信号生成与评价

综合考虑前述关键点,基于 DE2-115与AD9910/PCBZ开发平台,利用FPGA内部PLL提供100 MHz精准频率作为DDS系统时钟频率,向profile0的写入频率控制字 0X06C8_B439,对应频率值2.65 MHz,观察Agilent 4395A频谱仪中信号输出,可以看到一个高稳定度的2.65 MHz正弦波信号。图6即为输出信号的频域图,从图6中可以看出,在2.65 MHz的标记点,信号质量好于80 dB。

同样的,在FPGA的频率合成控制下,将频率控制字0X05638866−0X06D71F37随机地向profile0写入,并不断用IO_UPDATE信号将其推送至有效寄存器。

同样用Agilent 4395A频谱仪观测信号输出,可以观察到图 7的输出调制范围为 2.105−2.672MHz的频率信号。简单分析可知,频率控制字0X05638866−0X06D71F37就实现了目标频率的全覆盖。

图7 一定调制带宽的信号源实测图Fig.7 Frequency signal with a setting bandwidth.

3 结语

利用FPGA和DDS搭建驱动信号发生平台,实现了高精度且调制带宽设置灵活的频率信号源。在实现高精度单频信号的基础上,合理调整输入频率控制字FTW的内容,即可得到带宽调制信号源。以上阐述的只是调频信号的产生机制。事实上,调幅信号也是可以由控制AD9910中地址为0X09的14-bit振幅比例因子寄存器实现。该调频调幅信号再经放大成为峰峰值为600 V,3 dB带宽为6 MHz的功率信号,即可驱动存储环中的Kicker,实现质子束流慢引出。由输出结果可以看到,FPGA在控制上展现了很大的灵活性,而DDS在信号质量上很有优势。

1 Tomizawa M, Yoshizawa M, Chida K, et al. Slow beam extraction at TRAN II[J]. Nuclear Instruments and Methods in Physics Research A, 1993, 326(2): 399−406

2 丁小平, 王书鸿, 韩谦. 小型医用质子同步加速器的慢引出设计[J]. 强激光与粒子束, 1998, 10(1): 88−93 DING Xiaoping, WANG Shuhong, HAN Qian. Design of vslow extraction for a small proton therapy synchrotron[J].High Power Laser and Particle Beams, 1998, 10(1):88−93

3 Node K, Furukawa T, Shibuya S, et al. Advanced RF-KO slow-extraction method for the reduction of spill ripple[J].Nuclear Instruments and Methods in Physics Research A,2002, 492(3): 253−263

4 史丹, 欧阳联华, 谷鸣. 上海质子治疗装置慢引出RFKO研究[J]. 核技术, 2012, 35(3): 231−235 SHI Dan, OUYANG Lianhua, GU Ming. The RF-knockout slow-extraction for Shanghai proton therapy facility[J]. Nuclear Techniques, 2012, 35(3): 231−235

5 樊世杰, 蔡飞, 范红旗, 等. 基于 AD9910的调频非线性步进信号生成方案[J]. 雷达科学与技术, 2011, 9(1):77−83 FAN Shijie, CAI Fei, FAN Hongqi, et al. Scheme for nonlinear stepped-frequency chirp signal generation based on AD9910[J]. Radar Science and Technology, 2011, 9(1):77−83

6 杨小勇, 毛瑞娟, 许林华. 基于FPGA的AD9910控制设计[J]. 电子设计工程, 2011, 19(2): 150−153 YANG Xiaoyong, MAO Ruijuan, XU Linhua. Control design of AD9910 based on FPGA[J]. Electronic Design Engineering, 2011, 19(2): 150−153