Mosaic line-scan camera based on FPGA

XIA Hu-pei, SU Xin-yan, LIU Pei-zhen, LIU Bin

(Shanxi Key Laboratory of Signal Capturing & Processing, North University of China, Taiyuan 030051, China)

Mosaicline-scancamerabasedonFPGA

XIA Hu-pei, SU Xin-yan, LIU Pei-zhen, LIU Bin

(ShanxiKeyLaboratoryofSignalCapturing&Processing,NorthUniversityofChina,Taiyuan030051,China)

Abstract:Because single line-scan camera loses light in the edge of the sensor when the field of view is large, a mosaic camera based on field programmable gate array (FPGA) is presented by putting multiple cameras arranged in a straight line to share the field of view and reduce the view angle of every camera.For detecting doping micro particles with the designed mosaic line-scan camera, a detection algorithm of the target’s location in FPGA is proposed.Finally, the practicability and stability of the system were validated experimentally.The results of the experiment show that the camera can get images clearly with less light loss and can accurately distinguish the target and the background.

Key words:large field of view; line-scan camera; field programmable gate array (FPGA); threshold segmentation

CLDnumber: TP273Documentcode: A

Line-scan camera generally uses linear charge coupled device (CCD) or complementary metal oxide semiconductor (CMOS) as its imaging sensor.Due to its characteristics of fast scan speed, high precision and non-contact measurement, line-scan camera is widely used in sorting and doping fields to detect whether there is any target and the location of the target[1-2].

There is great need for detecting a large field in the practical application of line-scan camera, and commonly used method is to select the optical imaging system with large aperture and wide field of view[3-5].Due to effect of the lens, both sides of the axis have light energy decrease in imaging system, the energy distribution is uneven on the surface of the sensor.The image of line-scan camera is a middle high curve, not a straight line[6-7].This phenomenon is more obvious in optical imaging system with large aperture and wide field of view.It may cause the uselessness of edge pixels, seriously affecting the performance of the camera.

To solve the above problems, this paper presented a detection algorithm of the targets’ existence and position in a large field of view, introducing a mosaic line-scan camera based on field programmable gate array (FPGA).First, to solve the light loss problem due to large field of view, multiple line-scan cameras are arranged in a line to reduce every camera’s field of view.Then a detection algorithm is proposed based on FPGA according to the features of the detected objects.Finally, a camera is used to detect doping process of micro particles and to verify the camera’s reliability and stability.

1 Working principle and system composition

According to the imaging principle of camera, the object distance of camera isL, and the field angle isθ, therefore the width of the fieldDis

(1)

Because of the limitation of environment in the practical application,Lcannot be increased arbitrarily.To increase the field width, the view angle of camera must be increased.Using the camera mosaic method, field width can be increased with the increase of the camera number at the same distance and angle of view.At the same time, considering the parallel working characteristics, FPGA can drive a plurality of cameras working simultaneously to improve the overall pixel quality of the camera without affecting line frequency.

Based on the parallel signal processing ability of FPGA, this paper spliced four cameras in a line, and the line-scan camera schematic diagram shown in Fig.1.The camera is composed of CMOS image acquisition module and FPGA image processing module.The image sensor outputs image data after the data of AD converter enters into the FPGA for image processing.Communication interface is used to communication with external equipment; display is used to display the image in real time.

Fig.1 Schematic diagram of mosaic line-scan camera

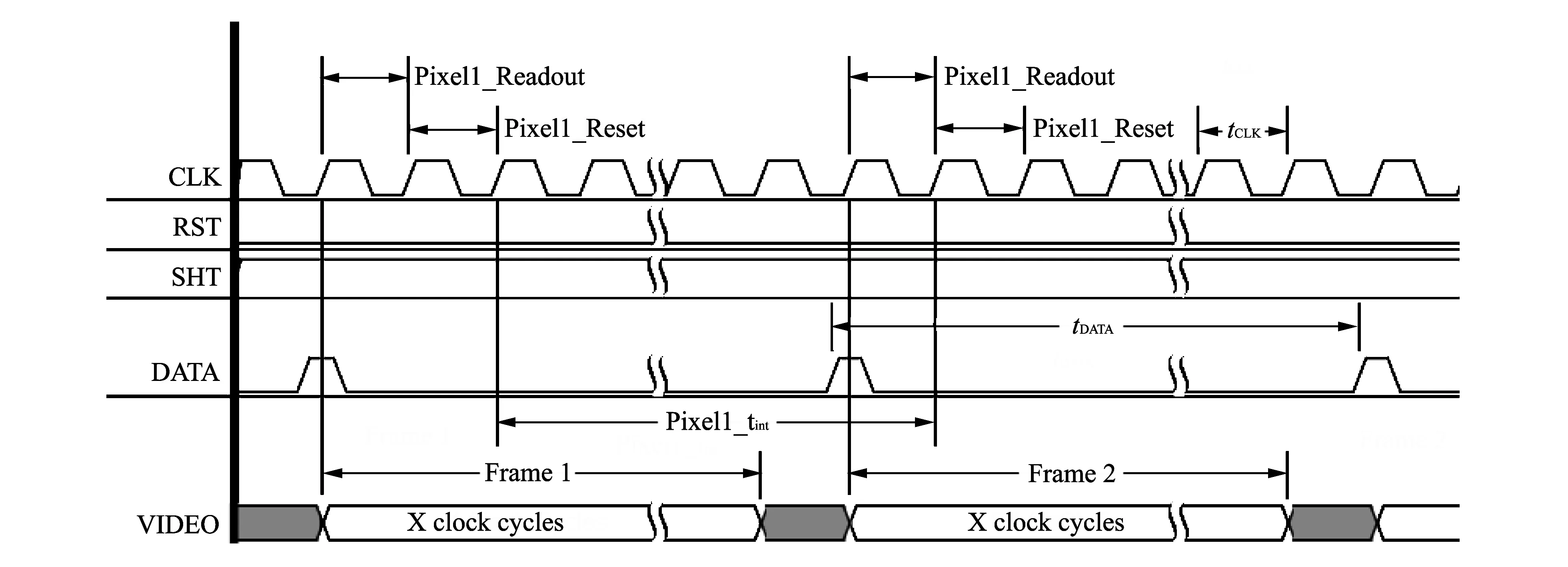

The camera sensor is ELIS-1024, a CMOS sensor from Photon Vision Systems Company with high sensitivity, high signal-to-noise ratio and low dark current.Its resolution can be configured through the pin level.Chip driving sequence is shown in Fig.2.DATA is line frequency signal, and CLK is image output clock.The system has the resolution of 1 024 pixels, frequency of 10 kHz.

Fig.2 ELIS-1024 driving sequence

The AD chip is AD9280 produced by Analog Devices Company.It is a 8 bit parallel ADC and can configure up and down reference voltages to achieve the best result.According to the resolutionMand frequencyK, the sampling ratefof the system can be calculated by

f≥MK.

(2)

The sampling rate should be greater than 10.24 MHz.In this system it is set at 12.5 MHz.The maximum conversion rate of AD9280 is 32 million samples per second, fully meeting the design requirements.

FPGA is Spartan-3E series chip XC3S500E from Xilinx Inc.The chip uses 90 nm process, supports a variety of standard levels, and has abundant internal logic resources.Its equivalent logic gate count is 50 million, with 158 user I/O ports, 65 differential I/O pairs, 73 Kbit distributed RAM, 360 Kbit RAM blocks, 20 dedicated multipliers and four digital clock managers (DCMs).In this system, FPGA is not only control unit of sensors and AD converters, but also the image processing unit.

2 Detection algorithm and FPGA implementation

2.1 Detection algorithm

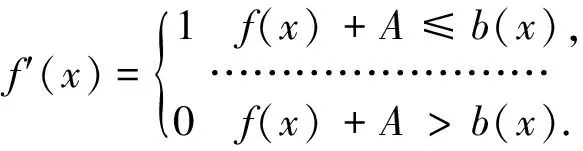

To detect the presence and location of the target, threshold segmentation method is used to achieve the target’s feature extraction.Threshold operation is simple, fast, high efficienty and very suitable for hardware implementation.Threshold algorithm is described as

(3)

wheref(x) is original image,xis pixel location,Tis segmentation threshold andf′(x) is segmentation result.By using a backlight, when the target gets into the detection area, the image gray value of the area will be darkened.By setting a reasonable threshold, when the detected image gray level is less than or equal to the threshold, the point is set at a value of 1, otherwise 0.Finally, the value off′(x) is analyzed, 0 for background and 1 for the target, and the target position can be calculated byx.In this system the background image is relatively simple, therefore the change range of the gray can be found through experiments.By getting the minimum of the rangeAand setting the background imageb(x), the threshold is calculated by

T=b(x)-A.

(4)

Because subtraction needs more clock cycles than that in the FPGA, combining Eqs.(3) and (4), the algorithm is rewritten as

(5)

2.2 FPGA Programming

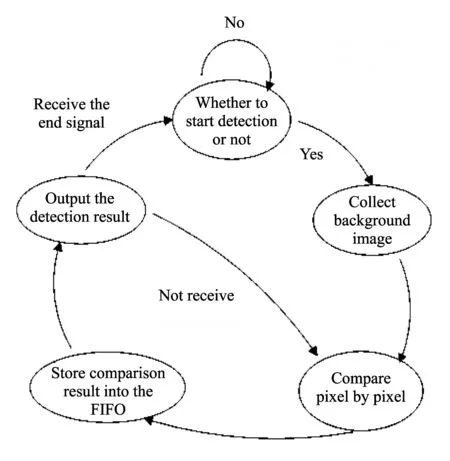

In the actual production environment, background image itself will change, thus the detection results may lead to mistakes.To ensure the accuracy of detection, the threshold should be changed with the change of the background image.Before starting the detection, the background image is gained and the threshold is reset based on the image.

According to Eq.(5), the system uses a state machine to achieve the detection program and state transition diagram is shown in Fig.3.

Before the target gets into the detector field, collecting a row of data as a background imageb(x), then combining the horizontal frequencies of the image sensor and image output clock, comparingf(x)+Apixel by pixel with the background imageb(x), the comparison result is stored into the first-in first-out (FIFO) with the depth of 4 096.And then outputting the detection result through the communication interface and meanwhile determining whether it receives the signal for the end.If FPGA receives the signal, the detection cycle is completed, and it enters the next detection.If it does not receives the signal, collecting the next line of data and segregating it, the result again enters into the FIFO.Repeating this process until it receives the signal.

Fig.3 State machine of FPGA program

3 Experimental verification

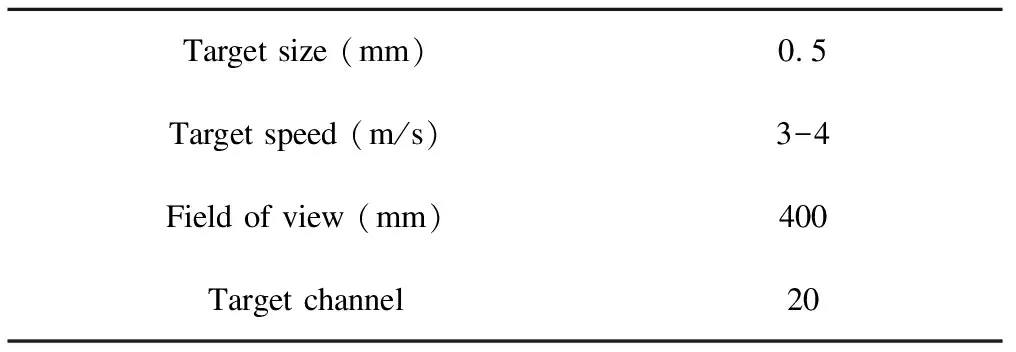

The process of a new product needs doping tiny metal particles to the product and the position of the dopant metal particles is also required strictly.According to this background, a detection system is built based on the camera to test the camera’s performance.Testing requirements are shown in Table 1, and the photo of the detection system is shown in Fig.4.

Table 1 Testing requirements

A single camera’s field of view is 120 mm, but in order to prevent the loss of light effect on the camera, the effective field of view of each camera is 100 mm, thus the whole field of view is 400 mm.The detection system’s working process is as follows: the tiny metal particles through the transparent glass channels are illuminated by the backlight, then are dropped on the machined products according to the predetermined pipeline.Finally the cameras photograph the images of the channels to detect whether the target has been passed through the channels and the channel position.

Fig.4 Photo of detection system

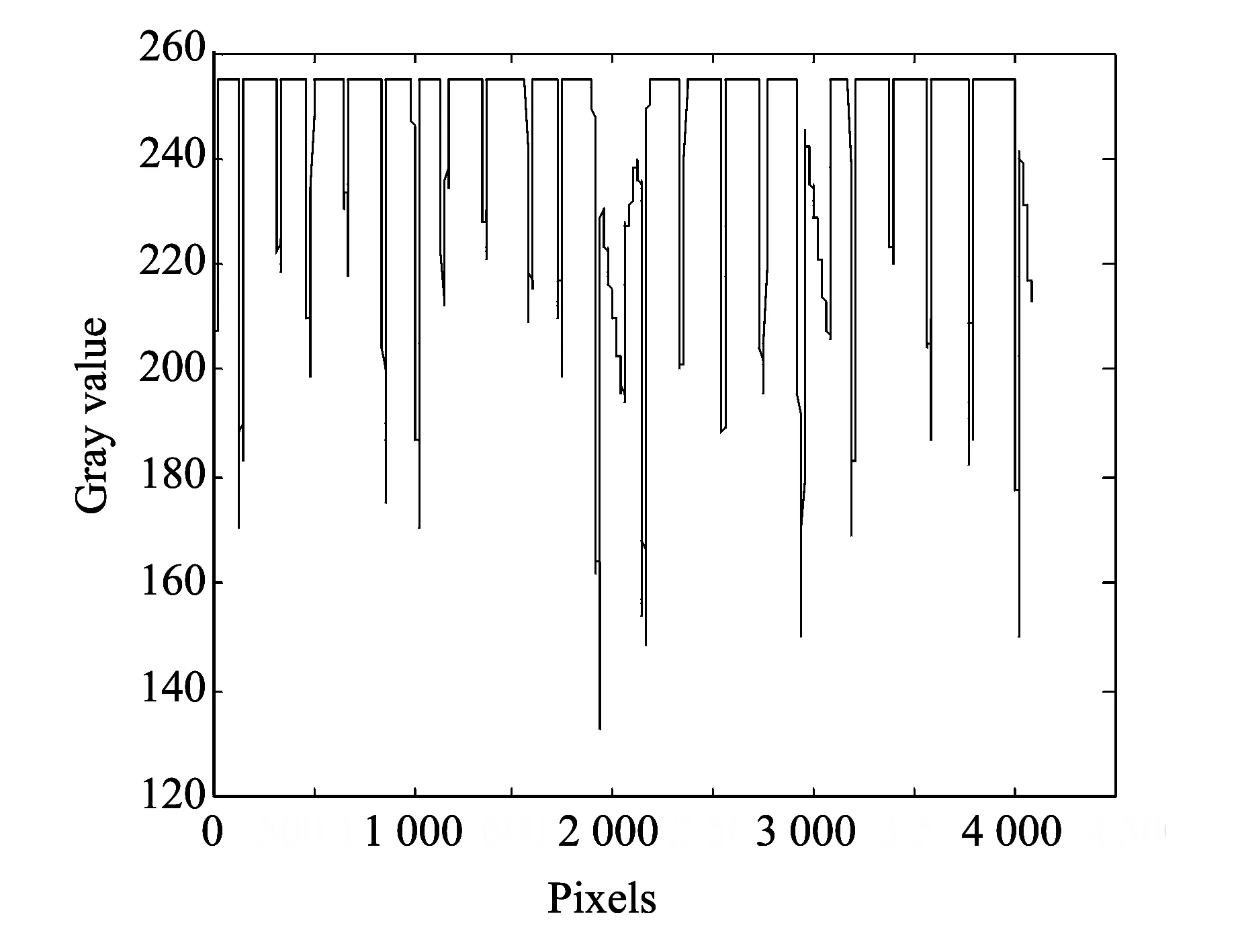

In the experiment, each camera detects five channels.Fig.5 shows gray values of the background image.There are 23 low gray values under spikes, among which 20 values are from 20 target channels of four cameras, and other three values are from the loss of light in the edge of the sensor.

Fig.5 Background image

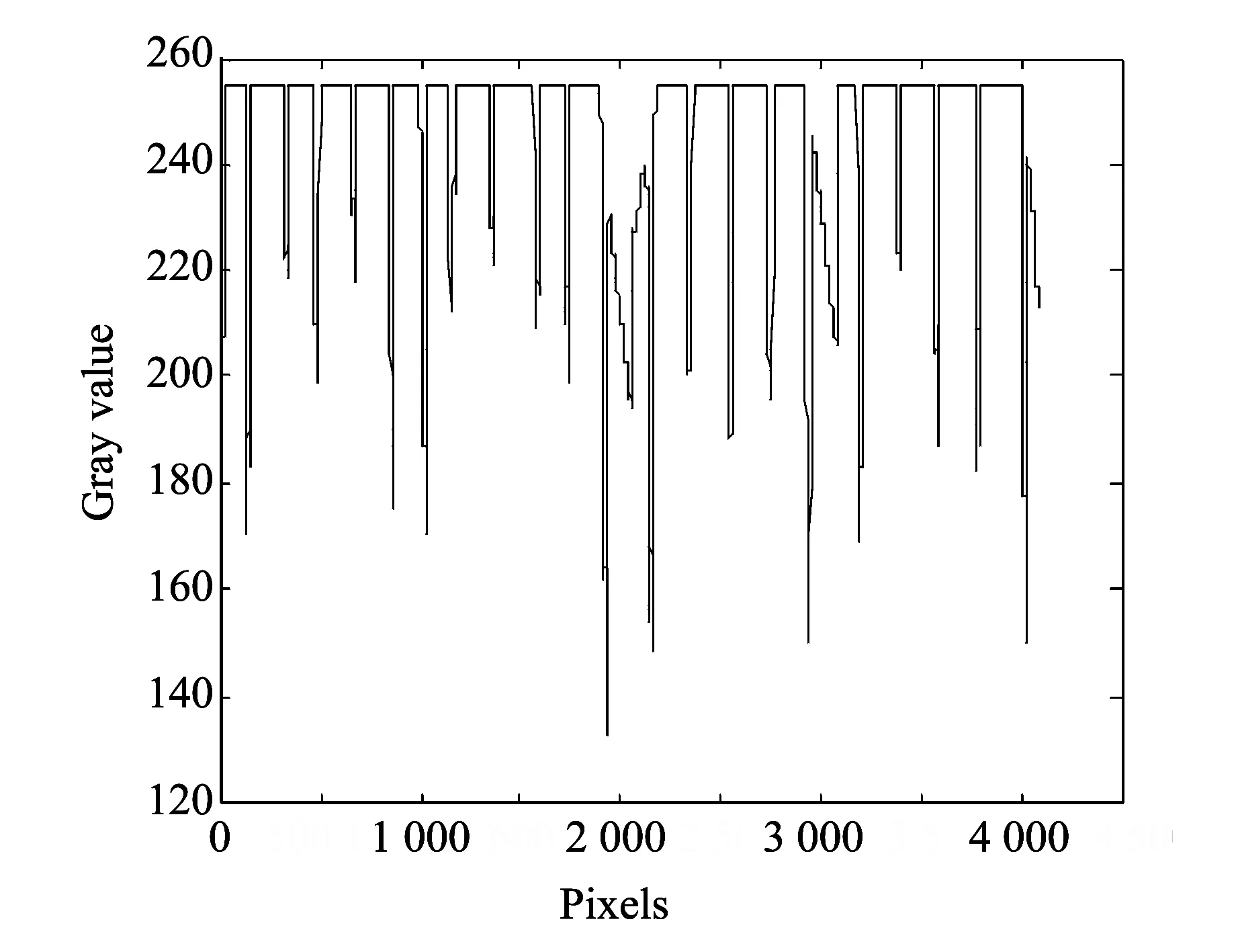

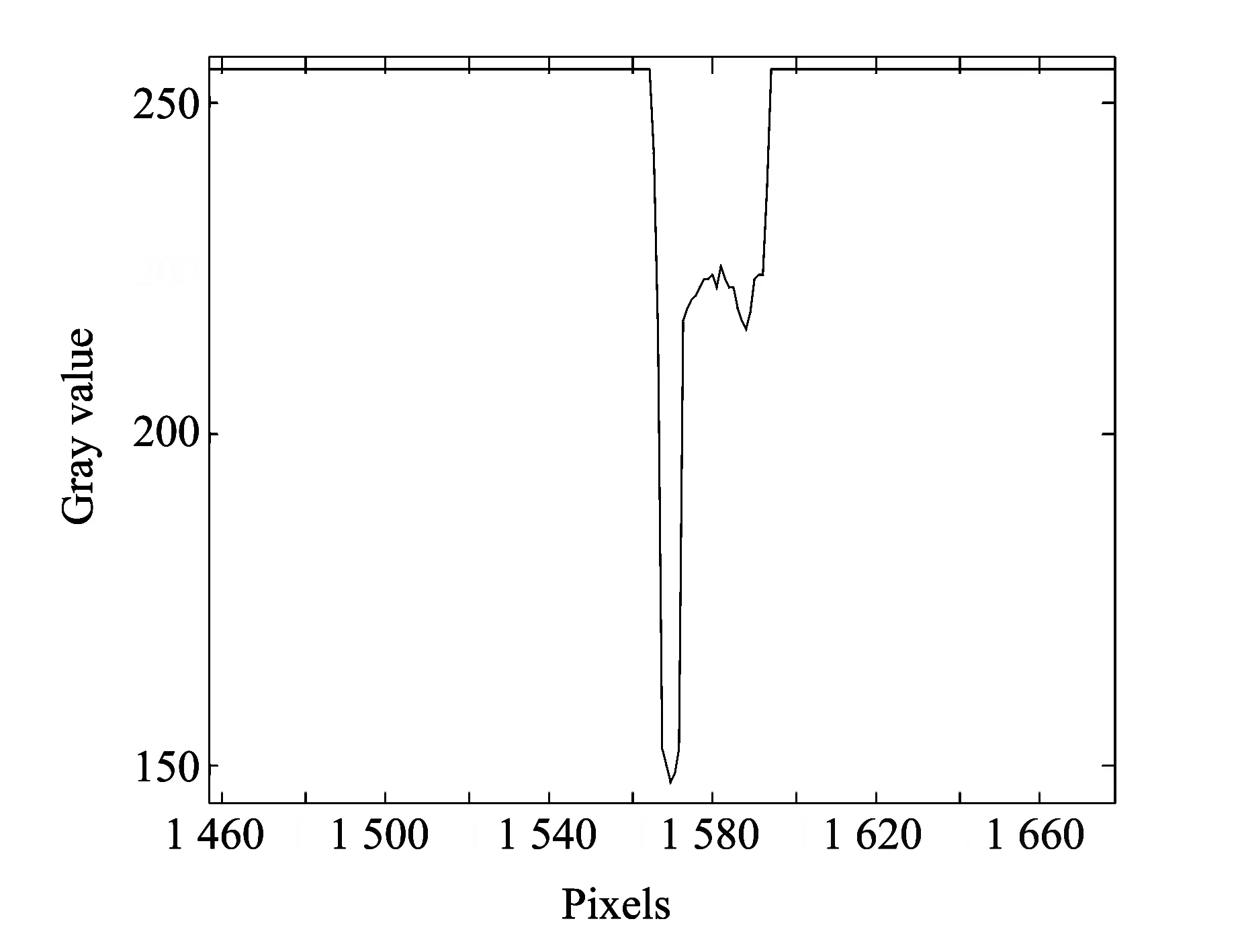

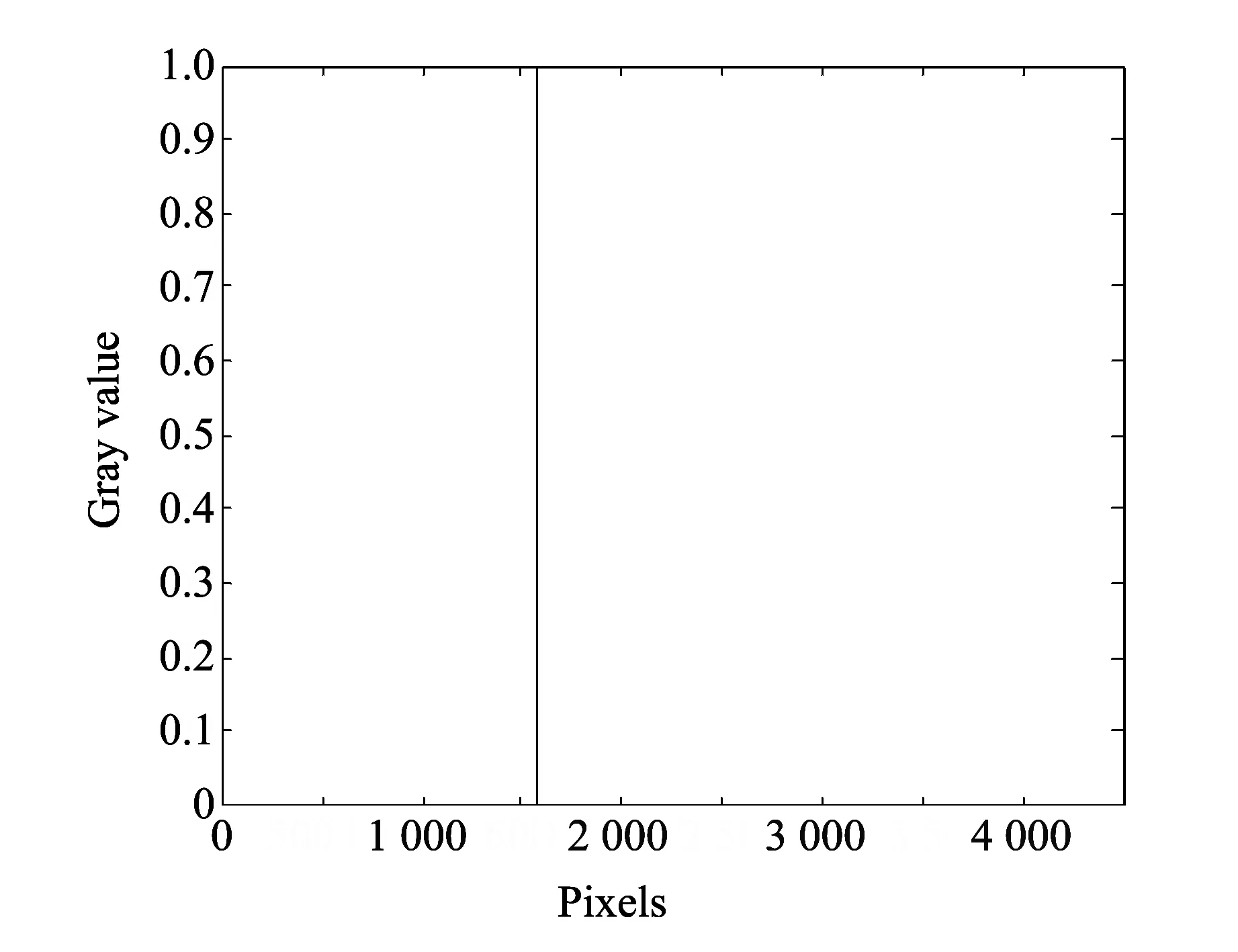

Fig.6 shows the gray values of a single target through the background, and Fig.7 shows the details.It can be seen that there is a significant reduction nearby 1 500 pixel point.Fig.8 is the segmentation results (FIFO values) of this target.In the range from 1 568 to 1 572 pixels, the value is 1, and others are 0.The value of 1 is the target.Based on camera imaging principle, we can calculate the actual position of the target.

Fig.6 A single target image

Fig.7 Details of a single target image

Fig.8 Segmentation result

4 Conclusion

The design of mosaic line-scan camera based on FPGA reduces the light loss phenomenon under a large field of view.The camera uses FPGA as the controller and image processor and a FPGA-based detection algorithm is designed according to the target characteristics.Finally, the camera is used to detect doping process of micro particles, and verify the camera's reliability and stability.

[1] YU Xiao-lei, ZHAO Zhi-min, CHEN yuan, et al.On-line nep detection used in carding machine based on machine vision.Transducer and Microsystem Technologies, 2008, 27(7): 96-98.

[2] CHEN Ping, LI Yi-hong.Automatic detection system of small objects falling based on linear CCD.Manufacturing Automation, 2013, 35(2): 45-49.

[3] BIE Jun-feng, YE Yu-tang, LIU Lin, et al.A new method of high-precision and real-time splicing based on the multi-line array CCD camera’s large format scanner.Chinese Journal of Electron Devices, 2013, 36(1): 44-48.

[4] ZHANG Ming-yu, LIU Jin-guo, LI Yu, et al.Binocular CMOS APS image system based on camera link interface.Optoelectronic Technology, 2008, 28(4): 270-273.

[5] JIN Yi, ZHAI Chao, XING Xiao-zheng, et al.Modeling and simulation of LAMOST focal plane observation planning.Acta Metrologica Sinica, 2007, 28(4): 306-310.

[6] GUAN Che, WANG Yan-jie.Real-time auto light control system of CCD camera.Optics and Precision Engineering, 2008, 16(2): 358-366.

[7] ZHU Jun-chao, LIU Tie-gen, LIU De-rui, et al.Linear CCD gray-scale distribution real-time calibration method.Opto-Electronic Engineering, 2007, 34(12): 108-112.

基于FPGA的拼接式线阵相机设计

夏湖培, 苏新彦, 刘培珍, 刘 宾

(中北大学 信息探测与处理山西省重点实验室, 山西 太原 030051)

摘 要:针对单线阵相机在大视场下传感器边缘的失光问题, 设计了基于FPGA的拼接式线阵相机。 采用将多个相机直线排列的方法, 对视场进行分担, 减小了单个相机的视场角。 在检测微小颗粒掉落的应用中, 在FPGA内部设计了目标位置的检测算法, 并通过实验验证了系统的实用性和稳定性。 实验结果表明, 相机成像清晰, 边缘失光较小, 可准确区分目标和背景。

关键词:大视场; 线阵相机; FPGA; 阈值分割

引用格式:XIA Hu-pei, SU Xin-yan, LIU Pei-zhen, et al.Mosaic line-scan camera based on FPGA.Journal of Measurement Science and Instrumentation, 2014, 5(4): 57-61.[doi: 10.3969/j.issn.1674-8042.2014.04.011]

Article ID:1674-8042(2014)04-0057-05

10.3969/j.issn.1674-8042.2014.04.011

Receiveddate: 2014-07-16

Foundation item:National Natural Science Foundation of China (No.61227003, 61171179, 61302159); Natural Science Foundation of Shanxi Province (No.2012021011-2); Research Project Supported by Shanxi Scholarship Council of China (No.2013-083); Specialized Research Fund for the Doctoral Program of Higher Education, China (No.20121420110006); Top Science and Technology Innovation Teams of Higher Learning Institutions of Shanxi Province, China

Corresponding author:XIA Hu-pei (xiahupei@163.com)

Journal of Measurement Science and Instrumentation2014年4期

Journal of Measurement Science and Instrumentation2014年4期

- Journal of Measurement Science and Instrumentation的其它文章

- Research on measuring time constant of NANMAC thermocouple

- Cutting force measurement based on tool embedded Ni-chrome thin-film micro-sensors

- Empirical model of correction for zenith tropospheric delay

- Detection technique of moving target based on passive millimeter wave

- Polarization state measurement based on photoelastic modulation

- Measurement and control system for servo pressure pulse testing equipment