某弹载计算机CPU模块的设计与实现❋

吕 浩,梁争争,李翠娟

(中航工业西安航空计算技术研究所,西安710068)

某弹载计算机CPU模块的设计与实现❋

吕 浩,梁争争,李翠娟

(中航工业西安航空计算技术研究所,西安710068)

弹载计算机作为精确制导武器的核心单元,是实现武器系统精确制导的关键部件。随着武器装备发展水平的提高,弹载制导计算机要求更高的数据采集与处理速度、更高的实时性与可靠性。从功能上讲导引头弹载计算机要完成数据的采集、处理与运算,并提供通信接口。为保证武器的制导精度,弹载计算机必须具备较高的数据采集与运算速度,并完成实时处理。现从设计者的角度提供了一种应用高性能DSP主机接口的弹载计算机设计方法。

TMS320C6455处理器;现场可编程门阵列;SPI接口;HPI接口

1 引 言

精确制导武器的研制对于提升我国常规武器的空中打击能力起着尤为重要的作用。弹载计算机作为其重要组成部分,具有体积小,成本低,速度快,层叠结构等显著特点,并且单个模块融合多种接口。导引头弹载计算机是导弹的核心部件,其处理的数据量大,运算复杂,实时性强,对CPU模块的设计要求较高。随着可编程超大规模集成电路技术和微处理器技术的提升,更多的处理工作由可编程器件来直接完成,并配以高性能CPU完成后处理,逐渐取代了以往双CPU以软件分工的设计。

2 系统描述

某弹载计算机安装在导弹电子仪器舱内,用于导弹的信息采集、处理、信号输出与目标检测等功能。某弹载计算机由两个部分构成:CPU模块和IO处理模块。IO处理模块主要负责模拟量、离散量的输入\输出转换;CPU模块主要负责系统管理、转换后数字量的传递处理、数值运算与其他数字接口。系统结构框图如图1所示。

3 设计与实现

某型弹载计算机CPU模块主要采用DSPTMS320C6455和FPGA XC2V2000来设计实现,对各接口信号进行采集处理和运算。

图1 某弹载计算机系统结构

24通道A/D,数据转换后通过两路SPI接口进入CPU模块处理,CPU模块在不用处理器干预的情况下以基频信号为基准,以DMA方式写入DSP固定内存,周期性存储和更新数据,并通知CPU及时处理,周期性工作均由FPGA逻辑完成;1路D/A,也通过SPI接口与CPU模块相联,FPGA可按照CPU预先写入的数据周期性发送输出。

另外CPU模块还具有的接口包括:16路离散量输出、4路离散量输入、4路调试LVDS信号输出、双口存储器可与飞控计算机通信以及RS232调试接口可用于地面调试。

HPI主机控制器以DMA方式访问DSP内存,采用双缓冲操作以防止读写冲突;其余功能模块均通过EMIFA并行总线与DSP通信,DA输出在FPGA内部同样采用双缓冲操作。

根据某弹载计算机功能要求,CPU模块主要包含以下功能模块:

1)DSP及其外部电路;

2)SPI接口逻辑;

3)HPI接口逻辑;

4)数字离散量接口;

5)RS232串行接口与LVDS接口;

6)双口存储器;

7)电源转换电路。

某弹载计算机的CPU模块结构图如图2所示。

图2 CPU模块结构框图

3.1 DSP及其外围电路

某弹载计算机CPU模块选用的DSP是TI公司的TMS320C6455,该芯片是32位定点数字信号处理器,主频可达1GHz,该DSP内部集成2MB的RAM和32KB的ROM,并集成了64位EMIFA总线等丰富的外围接口资源,能够大大简化系统电路设计。

设计中给DSP以40MHz的外部时钟,经倍频后DSP工作主频800MHz,EMIFA总线频率100MHz; DSP外接FLASH芯片SM29LV320,并配置BOOT自举模式为FLASH启动。DSP和FPGA的统一上电\手动复位信号均来自MAX706提供的200ms低脉冲复位信号。

DSP外的存储器包括FLASH存储器和DPRAM,分别设置在TMS320C6455的CE2和CE3空间。由于其内部RAM有2MB,所以没有外扩RAM。C6455与XC2V2000连接的EMIF接口,接在CE4空间。存储器电路设计充分利用了芯片内部集成的资源,在保证性能的前提下,简化了DSP外部电路设计,降低了器件成本。

3.2 SPI接口模块

CPU模块的SPI接口、HPI主机控制器等诸多功能均由FPGA内部实现,FPGA采用XC2V2000,其具有200万门规模,1Mbit的RAM资源,I/O管脚支持LVDS信号传输。

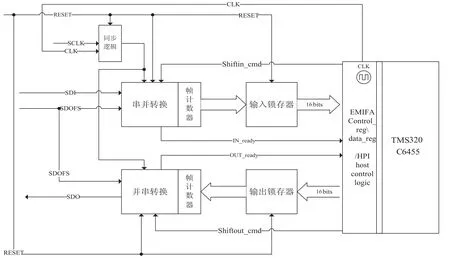

SPI接口实现了串并/并串转换,用于AD/DA芯片的通信连接。其设计要点为在接口同步时钟的节拍下,数据移入移位寄存器或由移位寄存器移出,每帧数据为16bit,输入的后级和输出的前级需有锁存寄存器。图3为SPI接口逻辑的结构框图。

图3 SPI接口模块结构框图

设计中,在上电后对AD73360芯片初始化启动时,DSP通过EMIFA总线和SPI接口逻辑输出符合芯片手册要求的初始化命令序列,AD芯片启动工作后,则变为数据通过SPI接口逻辑输入给主机控制器,主机控制器通过HPI接口写入DSP内存;DA7714芯片的初始化操作和AD芯片相同,启动后的操作则是DSP通过EMIFA总线将数据写入双缓冲区,而后数据以基频信号为周期通过SPI接口逻辑单向输出给DA芯片。

3.3 HPI接口模块

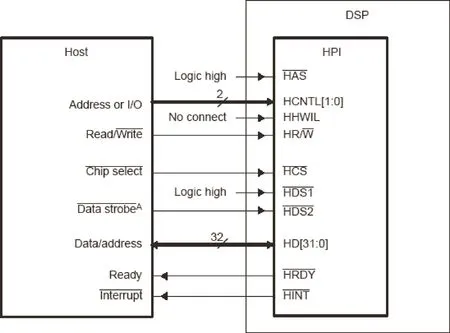

TMS320C6455自带的32位HPI主机接口可使主机CPU与其连接,以DMA方式访问DSP的内存,实现通信交互。HPI接口信号由地址选通信号、读写使能信号、片选信号、数据使能信号、32位数据信号、完成信号和中断信号组成。寄存器包括地址寄存器、控制寄存器和数据寄存器。HPI接口操作则是利用控制信号对寄存器的操作序列。HPI接口内部带有数据FIFO,可以地址递增方式联系读写数据,数据传输速率最高可达160MB/s,可满足设计中24路16位 AD的要求,并能免除DSP干预,提高系统性能。

在FPGA内部实现HOST主机控制器,用来接收两路SPI接口传输进来的AD数据,分别打入两个16*16bit的FIFO,当某个FIFO接收达到阈值时,将数据按照HPI写状态时序写入DSP的内存区。HOST主机与DSP的信号连接如图4所示。

图4 HOST信号连接示意图

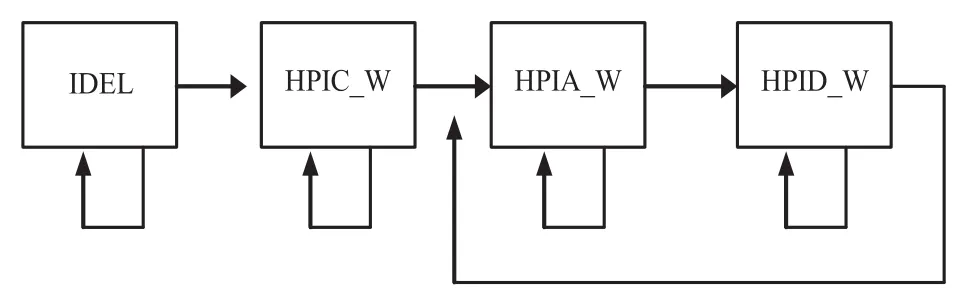

HOST主机操作用状态机来实现,其基本流程如图5所示。系统启动后,先进行HPI接口的初始化配置,写控制寄存器(HPIC_W),如果主机、SPI接口被使能,并且两缓冲区可用,则进入写地址寄存器状态(HPIA_W);根据DSP置位的缓冲区使能寄存器将当前可用缓冲区地址写入地址寄存器,当有某个FIFO接收数据达到阈值时,则进入写数据寄存器状态(HPID_W);判断当前是哪路SPI输入的AD数据,在当前有效16位数据前加上SPI通道标识,将32位数据写入数据寄存器。在当前状态的最后要判断当前缓冲区是否将写满,如果是则写入结束标识符并更新当前可用缓冲区地址,中断通知DSP,同时将当前缓冲区状态写入主机状态寄存器供DSP读取,循环进入写地址寄存器状态(HPIA_W),如果没有写满则循环进入HPID_W状态,继续等待写入AD数据。

图5 HOST主机基本状态示意图

状态机中每一个状态分别由一系列符合手册时序要求的分状态序列组成。

3.4 电源转换电路

采用两级电源转换,由电源TPH05000将5V输入电源转换为3.3V供给TMS320C6455 I/O电压和XC2V2000 I/O电压,同时输入给第二级的三路可调电源TPS74401。三路TPS74401配以不同的调节电阻分别提供1.25V给DSP的内核电压、1.8V给DSP的PLL I/O电压以及1.5V给FPGA的内核电压。开关电源TPH05000最大可提供6A输出电流,线性可调电源TPS74401最大可供3A输出电流,满足设计功耗要求。图6为CPU模块供电示意图。

3.5 RS232串行接口与其它功能模块

CPU模块上还包括有RS232调试接口、开关量输入输出接口、DPRAM接口和LVDS信号输出接口。DPRAM由在XC2V2000内部的1K*8bit的双口存储器来实现。

RS232调试口由C6455的McBSP接口通过软件编程来实现,后级由MAX3232实现电平转换,波特率选择115200bps。

开关量输入由FPGA内部的可读寄存器来实现,开关量输出由FPGA内部的只写寄存器来实现,寄存器操作由DSP通过EMIFA总线控制,寄存器分配在DSP的CE4空间中。

图6 CPU模块供电示意图

AD73360的SPI接口输出(帧同步信号、串行输出、同步时钟)经驱动进入FPGA后转换为LVDS信号输出,用于弹载计算机的调试监测。三路LVDS信号由FPGA的LVDS兼容管脚和功能模块实现。

4 结束语

TMS320C6455是一种高速定点DSP,它以其强大的运算和控制功能以及方便、灵活等特点在通信、信号处理、消费类电子产品等领域得到了广泛应用。在国防领域,随着各类机载精确制导武器的不断发展,系统单位对弹载计算机在运算能力、数据处理能力、实时性等方面提出了越来越高的要求。这就要求更多地应用高速接口和硬件分担更多的任务以减少CPU干预。设计采用了HPI接口连接高速定点DSP和FPGA,不仅能够完成弹载计算机的数据采集、处理与控制任务,而且减少了CPU干预,提高了效率,在系统应用中取得了很好的效果。对于高速定点DSP在弹载计算机设计中的推广使用具有一定的实用参考价值。

[1]黄克武,吴海洲.基于TMS320C6455的高速SRIO接口设计[J].电子测量技术,2008,31(9):143-144.HUANG Ke wu,WU Hai zhou.Design of high-speed SRIO interface based on TMS320C6455[J].ELECTRONIC MEASUREMENT TECHNOLOGY,2008,31(9):143-144.

[2]Texas Instruments.SPRU969B,2007,TMS320C645X DSP HOST PORT INTERFACE USER’S GUIDE[S].USA:TI,2007.

[3]Texas Instruments.SPRS276M,2005,TMS320C6455 FIXED-POINT DIGITAL SIGNAL PROCESSOR[S].USA:TI,2007.

Design and Im plementation of a Missile-borne Com puter CPU Module

LV Hao,LIANG Zheng-zheng,LICui-juan

(Xi’an Aeronautics Computing Technique Research Institute,AVIC,Xi’an 710068,China)

Themissile-borne computer,as the core unit of the precision-guided weapons,is the key component of the precision-guided weapon system.With the improvement of the level of weapons development,the missile-borne guidance computer requires high speed of data acquisition and processing and a higher level of real-time and reliability.From a functional perspective,missile-borne computer needs to complete the data acquisition,processing and computing,and provide the communication interface.In order to ensure the accuracy of the weapons guidance,itmust have high speed of data acquisition and operation,and complete real-time processing.This article describes a missile-borne computer design method with the application of high-performance DSP host interface from the designer's point of view.

TMS320C6455;FPGA;SPI;HPI

10.3969/j.issn.1002-2279.2014.06.021

TP302.1

:A

:1002-2279(2014)06-0074-04

航空科学基金项目资助(20100231)

吕浩(1984-),男,河南新郑人,工程师,硕士研究生,主研方向:嵌入式计算。

2013-12-23