阻容并联端接的研究与仿真

杨 沛

阻容并联端接的研究与仿真

杨 沛

端接技术可以改善高速电路中的信号完整性问题。首先,介绍了多种端接技术的原理及其各自的优势与不足,然后重点研究了阻容并联端接的原理和应用,通过理论分析给出端接方案中器件的取值对电路的影响,并利用电路仿真工具进行验证,为今后进行高速电路端接设计提供了参考依据。

信号完整性;高速电路;端接;电路仿真

0 引言

随着电路板上的信号速度越来越快,端接技术也变得越来越重要。高速信号在电路板上的传输过程中,由于受到芯片和电路板加工工艺的自身的限制以及布线约束,无法完全做到的阻抗一致性,导致了信号反射,串扰,地弹和EMI等一系列信号完整性问题。而端接技术作为一种改善信号完整性的方案,具有灵活性和低成本的特点,在目前的高速电路中得到了普遍的应用。

1 端接方案

信号完整性的定义是信号线上的信号质量[1],集成电路的切换速度过高,电路的布局布线不合理等都会引起信号完整性问题[2]。其根源就在于阻抗的不一致,端接技术的目的就是确保高速信号在传输过程中,感受到尽可能一致的阻抗,达到阻抗匹配的目的,从而避免各种信号完整性问题的发生。各种端接技术各有优缺点,需要针对实际需要选用[3]。目前,电路设计中,普遍采用以下几种端接技术:

串联端接:在发送端芯片侧,放置一个电阻,其目的就是用来防止从接收端芯片反弹回来的信号在发送端再次反弹。这种匹配方式只是实现了发送端的匹配[4]。一般来说,单端信号的传输线设计阻抗为50欧姆,发送端的内部电阻有十几欧姆,为了消除反射,电阻的大小通常为22欧姆或33欧姆,具体采用多大的电阻,可以通过仿真或者实际调试来确定。串联端接的优点就是结构简单,易于实现,缺点是对点到点的拓扑结构效果较好,点到多点的结构效果较差,电阻放置的位置需要进行精确的仿真。

并联端接:即在接收端附近与接收端并联,或上拉到电源或下拉到地。上拉时,可以提供最够大的驱动电流,下拉时也能吸收足够大的电流。由于接收器的电阻理想情况下是无穷大,并联一个50欧姆的电阻,可以消除信号在负载处的反射。并联端接的缺点是有直流功耗,并且可能导致直流工作点的偏移。

戴维南端接:借鉴了并联端接技术,上下拉电阻都并联在接收端。这种端接可以灵活地调节工作点的偏移,且保证阻抗匹配,缺点是直流功耗依然存在,需要慎重的选择阻值。

阻容并联端接:为了克服端接中的直流功耗问题,可采用阻容并联匹配,也称为终端交流匹配,如图1所示:

图1 阻容并联端接

由于增加了电容,阻隔了直流通路,消除了直流功耗和直流工作点的漂移。但增加的电容也引起了信号边沿的退化,应用时一定要结合具体电路进行理论与仿真分析。

2 阻容并联端接的理论分析

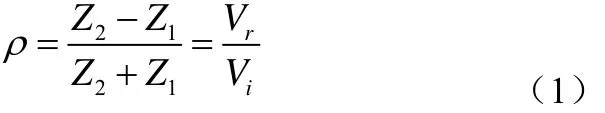

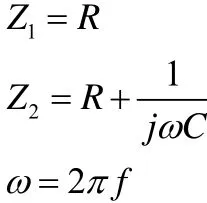

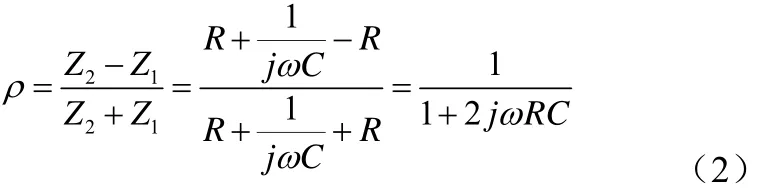

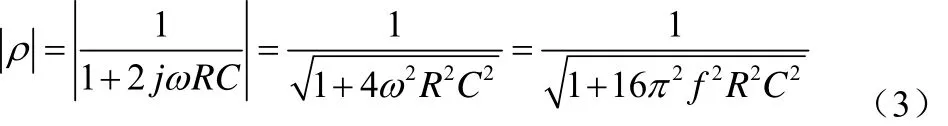

在高速设计中,连接线是带有电阻,电容和电感的复杂网络,需要用分布参数系统模型来描述[5],即传输线。信号从驱动器发出后,假设驱动器是理想的模型,其内阻为0欧姆,信号直接进入50欧姆的传输线,经过信号线后,到达A点。此时,信号会感受到阻抗的不连续,发生反射,其值由反射系数,如公式(1):

其中:

Vr 表示反射电压

Vi表示入射电压

Z1表示信号之前所在区域的瞬态阻抗

Z2表示信号进入之后所在区域的瞬态阻抗

ρ表示反射系数

图1的相应参数如下:

代入式(1)后,得公式(2):

对反射系数取模值,可以得到反射系数的幅度大小为公式(3):

其中:

ω是角频率,单位弧度/秒

f是频率,单位是赫兹

C是电容值,单位是法

由此可见,阻容并联端接的反射系数与信号的频率和电容值的大小有关,假设信号频率值一定,电容值越高反射系数越小,当电容值无穷大时,反射系数接近于0,可以看作电容对此频率的信号短路,相当于并联端接;反之,当电容值趋近于0时,反射系数趋近于1,相当于断路,没有进行任何端接。

驱动器的边沿信号的上升或下降速率越快,带宽越宽,包含的频率分量也就越高。从公式(3)中可以看出,电容越大越好,这样可以保证较高频率的信号也有近似为0的反射系数,从而近似消除反射。但是电容变大后,其时间常数也变大,充电时间变长,使得上升沿的上升时间变长,影响电路的时序。因此具体采用多大的容值,需要进行精确的仿真。

3 阻容并联端接的仿真

Hyperlynx作为高速信号仿真工具,其通用性,易用性和实用性赢得了广泛的用户[6]。它包含布线前仿真工具和布线后仿真工具。前仿工具是Linesim,其特点是用户可以像原理图设计一样进行操作,根据虚拟的叠层和物理约束,对信号进行what-If仿真,得到的结果用来指导电路板设计。后仿工具boardsim是电路板设计完成后,对其具体的电路板进行仿真,以用来验证前仿数据或改正电路板的布线约束,从而解决布线后的信号完整性问题。

用Hyperlynx的前仿工具进行阻容并联端接中电容值的仿真,如图2所示:

图2 Hyperlynx的阻容并联端接仿真

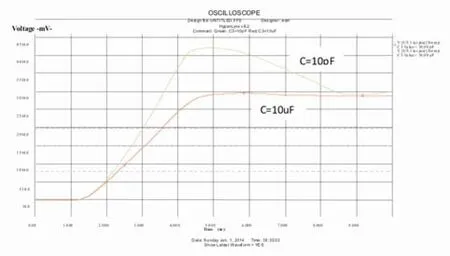

图(2)驱动器和接收器均采用CMOS3.3v的模型,传输线特性阻抗50欧姆,R3=50欧姆。为了比较电容值,先取C3=10pF,再取C3=10uF,比较接收端的上升沿情况,如图3所示:

图3 电容取10pF与10uF时,接收端仿真波形

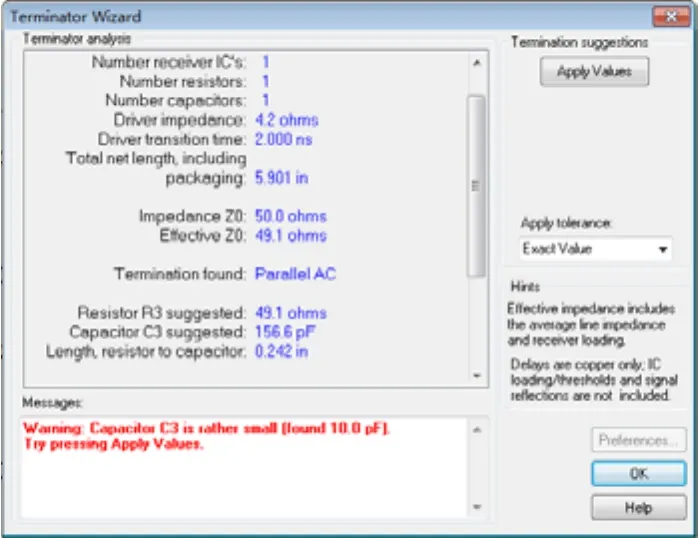

可见如果电容取值较小,则反射越大;如果电容较大,上升沿较缓,可能会对电路的时序产生影响。因此,需要根据实际应用进行仿真,来确定电容的大小。在Hyperlynx中,就有相应的设计指导Terminator Wizard,运行Terminator Wizard,软件会自动识别终端方式,并根据实际情况,得出终端中相应器件的推荐值。如图4所示:

图4 Hyperlynx的Terminator Wizard的推荐方案

图(4)Terminator Wizard提示C3的值过小,推荐采用156pF的电容,点击apply value后,C3的值变为156pF,再次仿真,如图5所示:

图5 电容取10pF,10uF与156pF时,接收端仿真波形

此时,接收端没有反射,信号的上升沿也较为陡峭,是较为折中的方案。

4 总结

在高速信号电路的设计中,阻容并联端接没有直流功耗,是一种比较通用的端接技术,但是电容的存在使得信号边沿变缓。本文对阻容并联端接进行了理论分析,同时利用仿真工具进行验证,并最终给出在仿真电路中的电容值,其理论分析和仿真方法具有普遍性,可以对今后高速信号电路端接设计起到指导作用。

[1] 余永莉.数字电路设计中的信号完整性分析[J].合肥工业大学学报(自然科学版), 2004,27(7):843-846.

[2] 肖汉波.高速PCB设计中信号完整性的仿真与分析[J].电讯技术,2006,5:109-113.

[3] 李成,程晓宇,毕笃彦等.基于HyperLynx的高速DSP系统信号完整性仿真研究[J]电子器件,2009,32(2):445-451

[4] 王剑宇,苏颖. 高速电路设计与实践[M] 北京:电子工业出版社 2010.

[5] 周萍.高速PCB板的信号完整性设计[J].电子质量,2009,1:32-36.

[6] 邵鹏. 信号/电源完整性仿真分析与实践[M].北京:电子工业出版社 2014.

Analysis and Simulation of RC Parallel Termination

Yang Pei

(DragonWave Telecommunication Technology (Shanghai) Co., Ltd., Shanghai200233, China)

Termination is used to improve signal integrity of high-speed circuit. The theory of many kinds of termination is presented, including their advantages and disadvantages, alongside the concentration on theory and application of RC parallel termination. The influence of components’ value from RC parallel termination is discussed in theory, and the result is verified by circuit simulation tools. It provides reference for design and application of termination of high speed circuit.

Signal Integrity; High-Speed Circuit; Termination; Circuit Simulation

TN41

A

1007-757X(2014)10-0038-03

2014.06.30)

杨 沛(1983-),男,山东青岛,加微通信技术(上海)有限公司,工程师,硕士,研究方向:高速电路设计,上海,200233