基于ARM+FPGA高分辨率液晶显示系统的设计与实现

张占来,任红光,季新明

(上海朗睿电子科技有限公司 郑州研发中心,河南 郑州450002)

传统工业液晶显示方案一般采用ARM结构[1],即ARM响应用户操作的同时又驱动液晶显示屏,实现人机交互操作。随着工业液晶显示的不断提高,高分辨率显示屏应用于工业场合,传统ARM方案驱动高分辨率显示屏已力不从心,操作反应迟钝、刷屏速度慢、显示效果差等缺点暴露出来。为解决上述缺点,本文给出一种ARM+FPGA结构驱动高分辨率液晶显示设计方案。

1 方案设计及工作原理

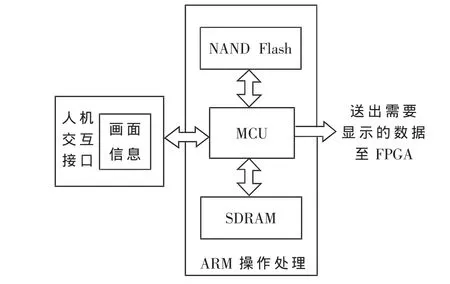

图1 方案框架结构

本文方案架构如图1所示,主要分为ARM操作处理和FPGA接收显示数据两大部分,其核心是用FPGA取代ARM内部显示缓冲区,提高ARM处理速度的同时,将ARM显示数据宽度由16 bit提升到32 bit,从整体上提升工业液晶显示器性能。

1.1 ARM操作处理

ARM操作处理结构如图2所示。画面信息通过人机交互接口和MCU下载到NAND Flash中,需要显示时,MCU将画面读出,根据要求送出需要显示的数据至FPGA。为达到高画质、刷屏速度快的效果,NAND Flash及SDRAM采用32 bit数据宽度的设计,MCU内部处理使用32 bit模式,需要显示的数据直接送出32 bit。

1.2 FPGA接收显示数据

FPGA操作处理结构如图3所示。FPGA主要完成以下任务:根据液晶显示时序产生读写显示控制部分;将接收的数据存储到DDR中;从DDR中读取需要显示的数据,将需要显示的数据转换为LVDS信号格式,输出驱动液晶显示屏。

图2 ARM操作处理结构

图3 FPGA操作处理结构

1.2.1 读写显示控制单元设计

根据液晶显示时序设计读写显示控制单元。各种液晶显示屏虽然时序有差异,但原理[2]相同,如图4所示,包括显示时钟 DCLK、显示数据 RGB_data、场频 Vs、行频Hs、场消隐和行消隐,只要满足以上条件即可驱动显示屏。在行消隐期间将每行需要显示的数据从DDR中读取到读FIFO中用于该行的显示,完成每行的读操作后将写FIFO中数据存储到DDR中。

图4 液晶显示屏时序(DE模式)

1.2.2 LVDS信号设计

LVDS信号中传输的数据是按照LVDS信号格式排列显示的,LVDS信号设计就是将需要显示的RGB888数据、DE使能信号和时钟信号转换为图5所示的LVDS信号格式[3]。

图5 LVDS信号格式(8 bit模式)

2 硬件设计

硬件设计主要分为ARM硬件设计模块和FPGA硬件设计模块。

2.1 ARM硬件设计

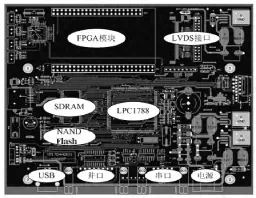

ARM硬件设计部分主要由ARM芯片1788、4片8bit NAND Flash存储芯片及两片16 bit SDRAM组成,如图6所示。LPC1788通过并口、串口或者USB接口接收画面信息,经过处理预先存储到NAND Flash中;根据用户需求再从NAND Flash中读取将要显示的画面信息,同时配合SDRAM操作,将需要显示的画面送至FPGA硬件设计模块,进行下一步驱动显示屏操作。

图6 ARM硬件设计结构

2.2 FPGA硬件模块设计

FPGA硬件设计模块主要由一片Xilinx公司的XC6SLX9芯片和一片镁光公司的MT46V32M16-5B组成,如图7所示。在XC6SLX9内部需要设计的硬件结构包括:接收LPC1788送出的需要显示的数据;从MT46V32M16-5B中读取显示数据转换至LVDS驱动显示屏。

图7 FPGA硬件设计结构

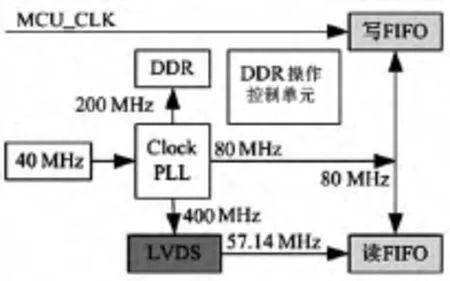

为方便处理,保证系统稳定可靠,FPGA芯片XC6SLX9内部时钟资源分配如图8所示。外部时钟40MHz输入到FPGA内部时钟锁相环,经设计分别输出200 MHz至MT46V32M16-5B;80 MHz至DDR操作控制单元、写FIFO的读时钟和读FIFO的写时钟;400 MHz至LVDS信号产生模块的同时,经7分频输出57.14 MHz至读FIFO中的读时钟。其中,写FIFO的写时钟来自LPC1788的MCU_CLK。

图8 FPGA时钟资源分配图

3 系统方案设计和整体显示效果测试

3.1 系统方案设计要点及解决方法

FPGA程序时序逻辑基于Xilinx ISE软件提供的编程环境和相关资源[4],通过VHDL语言编写完成。结合系统特点,在进行时序逻辑设计时需要解决以下问题。

(1)ARM送出的显示数据是一种随机位置的像素点,所以在存储数据时只能是单个数据的存储,不能批量操作,否则会导致存取速度降低。

(2)高分辨率显示屏像素点一般在1 280×1 024以上,此类显示屏要求驱动数据是奇偶列数据分离驱动,即双路LVDS接口(见图5)。因此在实现LVDS数据接口操作时,就需要将显示的数据进行奇偶分离处理,同时送出至显示屏。

为解决上述问题,本方案采用双端口操作DDR控制器模块,即其中一个端口负责ARM送出奇地址数据的接收至DDR和奇地址显示屏数据的读取至读奇FIFO;同时,另一端口负责偶地址的存取并最终至读偶FIFO。在进行显示时,采用双路LVDS信号转换方式,同时送出LVDS信号驱动液晶显示屏。

3.2 系统方案硬件搭建

LCD液晶显示屏采用三星公司的LTM170ET01。系统采用ARM底板+FPGA核心板组合的方式实现,ARM模块电路板(底板)如图 9所示,FPGA模块电路板(核心板)如图10所示。在图9中,上位机通过USB接口或者串口与ARM实现人机交互,ARM将需要显示的数据送至FPGA模块;FPGA将接收到的数据根据需要通过LVDS接口送出至LCD液晶显示屏。

图9 ARM模块电路板(底板)设计

图10 FPGA模块电路板(核心板)设计

3.3 显示效果评测

传统ARM显示处理模式为 16 bit,即 RGB656结构。显示屏接口数据为RGB888结构,就需要将RGB565结构通过高位补低位的方式扩展到RGB888模式。而本文设计的数据接口为32 bit,即 xRGB8888模式,实现了与显示屏接口的无损失对接,显示全彩无失真,如图11所示。

传统ARM方式既要响应用户操作,又要驱动显示屏,占用了ARM较多的资源。而本文采用ARM+FPGA结构,将显示部分由FPGA完成,节省了ARM资源的同时,提高了ARM的响应速度。

为了节约成本,将LVDS信号接口放在FPGA内部实现,省掉外部专用LVDS接口转换芯片,降低了产品硬件成本,提高了产品竞争力。

图11 ARM+FPGA系统方案显示效果

[1]NXP Semiconductors.LPC178x/7x.32-bit ARM Cortex-M3 microcontrolle r;up to 512 KB Flash and 96 KB SRAM;USB Device/Host/OTG;Ethernet;LCD;EMC.Rev.00.08.1.[Z]2011.

[2]Lux Display.AT070TN83 V.1[Z].

[3]Samaung Electronics.Samaung TFT-LCD.LTM-170ET01[Z].21.2009.

[4]Xilinx.Spartan-6 FPGA memory controller UG388(v2.3)[Z].2010.