激光测距高速采集和处理电路的设计

周少杰

(华中光电技术研究所 武汉光电国家实验室,湖北 武汉 430223)

激光测距高速采集和处理电路的设计

周少杰

(华中光电技术研究所 武汉光电国家实验室,湖北 武汉 430223)

针对激光测距仪经典接收方法,设计了一种高速数字化采集电路。论文采用ADC+FPGA+DSP的设计方案,具有可调分辨率,最小分辨率可达0.3mv。详细介绍了电路的具体设计方法。对脉冲信号进行测量,结果表明该方案可行。

激光测距;高速ADC

0 引言

激光测距仪是利用激光良好的准直性及非常小的发散角度来测量距离的一种仪器。但目前激光测距仪主要采用脉冲法进行测距,通过测量激光器发出光脉冲的时刻与光脉冲到达目标并由目标返回接收机的时间差计算出目标距离。准确判断回波的到达时刻是测距的关键。激光测距仪经典信号检测一直采用模拟电路来完成,主要利用分离元件和小规模集成电路对回波进行放大、滤波、阈值触发、整形,在信噪比较大的条件下,能够准确的判断回波到达时刻,当信噪比变小时,由于噪声的干扰,回波到达时刻就难以确定。近年来随着高速AD、存储器以及高速并行处理器的飞速发展,为回波检测提供了新的方向。本文提出了一种激光测距的数字化方案,它采用以高速数字采集为核心的数字化接收电路,利用高速FPGA进行数据存储和信号控制,最后利用DSP进行处理以实现回波信号检测。

1 硬件电路设计

1.1 电源设计

高速电路板设计的一个重要的考虑就是电源的设计和网络分配。电源的设计是选择合适的电源芯片,满足电压强度、电压纹波以及电流强度的要求。电源的网络分配必须为高速电路板上各部分的电路提供一个低噪声的电压信号,包括VCC和接地匹配。电源分配网络同时还得为电路板上所有产生或接受的信号提供一个信号回路,合理的分配电源层和地层可以有效减少电磁干扰。本电路采用5V供电,采用线性稳压芯片对各电源单元供电,对重要电源增加滤波电路设计。布局布线方面,在避免使信号线跨电源平面的前提下,对电源层进行分割, 以减少成本。详细设计参考如图1所示。高速的模拟器件一般对数字噪声很敏感,所以我们将模拟电源和数字电源分开,在电源的入口处接在一起。

图1 电源设计框图Fig.1 Block diagram of power supply

1.2电路设计

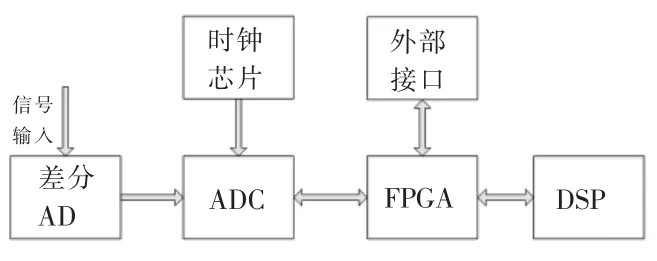

电路包括以下几个部分:差分AD模块、超低抖动时钟芯片模块、高速ADC模块、FPGA,DSP以及所需要的外部接口模块。电路组成框图如图2所示。差分AD和超低抖动时钟芯片模块组成了高速ADC模块的信号输入端,FPGA为高速ADC提供必要的初始化和控制信号,以及存储ADC采样数据。DSP通过EMIF总线读取FPGA中的采样数据后进行数据处理。

图2 电路原理示意图Fig.2 Schematic of circuit

由香农采样定理可知,要想通过采样信号对原始信号进行恢复,采样频率至少得是原始信号最高频率的两倍[1]。 目前激光回波信号为几十到几百ns,因此采样频率至少为MHz。通过比较,我们选择ADC08D500作为高速采样AD。它是一款高速双通道低功耗CMOS模数转换器,内置2个ADC电路,1.9V单电源供电,单个ADC电路工作时,功耗为1.4W[2]。单路最高采样率为500 MSPS,8位的分辨率(250MHz信号输入时,有效位为 7.5)。每个 ADC都有一个分解器,它可以将单个ADC的采样值分两路LVDS总线输出,从而可以降低总线输出频率。ADC08D500提供了一种DES的工作模式,该模式利用其内置的2个ADC对一个通道的输入模拟信号进行双沿采样,可以在500 MHz的时钟频率下实现1GSPS的采样频率。ADC08D500的输入信号和时钟要求采用LVDS电平标准。目前主要由两种方式将单端信号变成差分信号:①单端放大器+变压器;②采用专用全差分放大器。对于第一种方式,放大器要消耗大量功耗来使HD2变低,如果不用放大器,信号的增益调节受到限制(只能采用改变变压比的方式),并且变压器限制了低频信号的通过。第二种方式消耗的功耗小,并且具有灵活的增益调节能力。通过比较,我们选用第2种方式,采用AD8138作为信号差分放大器。AD8138是一款低成本、差分或单端输入至差分输出放大器,通过电阻设置增益,能够抑制谐波并降低辐射电磁干扰[3]。它具有较高的增益带宽,当增益为 10时,-3dB带宽为20MHz。对于微弱信号,可以方便利用合适的电阻来设置放大增益,来配合ADC08D500提高电路分辨率。高频时钟产生电路主要由以下三种方式:①以 PLL和VCO等分离器件构成;②以专有的集成芯片产生;③直接通过FPGA的内部锁相环倍频电路产生。通过比较,我们选用专有的集成芯片来作为时钟发生器。CDCM61001是一款超低抖动的时钟芯片,通过配置外部电阻,可以产生合适的差分时钟频率,最高可达600MHz, CDCM61001芯片尺寸仅有5×5mm,便于布线和放置[4]。

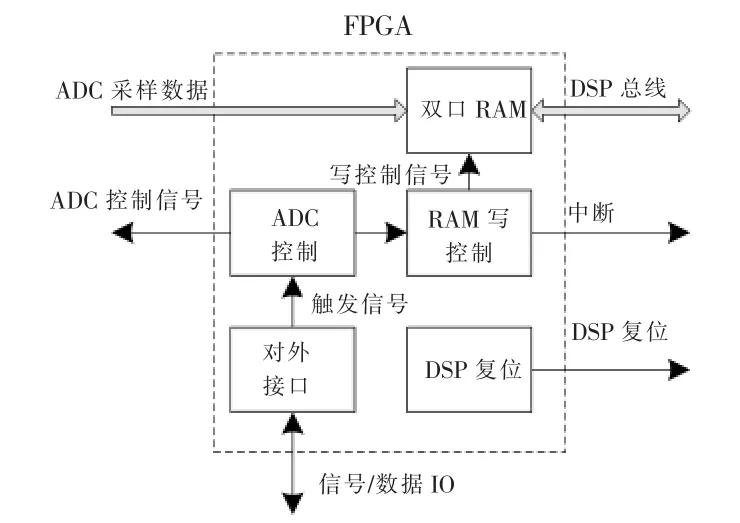

FPGA采用了StratixⅡ系列芯片,其IO端口支持LVDS信号,省去了电平转换芯片,并且IO端口速度快,可以满足ADC08D500的输出采样频率要求。FPGA时序和逻辑控制部分包括ADC控制模块、双口RAM模块、RAM写控制模块、DSP复位,对外接口。ADC控制模块包括控制ADC的供电电源芯片的使能端和ADC的状态设置。使FPGA在上电过程中ADC08D500的电源芯片处在禁止状态。配置ADC08D500寄存器,选择ADC的工作方式和模式,本设计中利用QuartusⅡ自带的工具产生双口RAM。写控制模块产生同步的地址信号和写信号。对外接口包括数据和控制信号的输入输出。DSP复位模块为DSP提供上电复位信号。FPGA内部各功能模块如图3所示。

图3 FPGA内部各功能模块示意图Fig.3 Diagram of function blocks in FPGA

DSP采用C6000系列处理器,通过 EMIF总线与FPGA内部双口RAM相连,激光测距算法的实现在DSP上完成。

1.3 PCB设计与实现

本系统PCB设计需要实现>=200MHz的模拟采样信号,>=200MHz的高速时钟,32bit差分高速数据信号以及多个电源信号的布局布线。在PCB设计中合理地布局器件,分开模拟电路和数字电路,尽量缩短高频元器件之间的连线,同时兼顾信号完整性和高速信号的阻抗匹配[5]。基于上述考虑,PCB设计采用FR-4板材,8层板设计,各层信号依次为:顶层(信号)-地层-信号层-电源层-信号层-电源层-地层-底层(信号)。待采样信号在顶层走线,32bit差分高速数据线对分布在顶层和底层。布局时使集成高速时钟芯片尽量靠近ADC的时钟输入管脚,差分时钟线布置在顶层。在PCB设计中,严格控制差分线对的长度和特征阻抗,使得数据线与时钟线的误差在100mil以内,差分阻抗100Ω[6]。由于电路中采用4种电源供电。因此在PCB设计时多种电源信号出现在同一平面层,在考虑信号完型性的前提下使各种不同的电源信号以分割的方式实现,防止电源信号对其他电路造成影响。

2 实验测试

利用SignalTapⅡ观察的结果如图4所示。实验中配置ADC08D500工作在非扩展模式,禁止ADCQ工作,使得ADCI单独工作,利用外部电阻配置相应管脚,使得LVDS输出电压峰峰值为710mV,上升沿输出,采用内部校验,输入电压范围为870mV。配置ADC8138的增益为2。通过选用合适的阻值,配置CDCM61001输出为200MHz的LVDS时钟信号。模拟输入信号采用信号发生器产生的脉冲信号。脉冲信号频率为1MHz,宽度为50ns,幅度为100mV。

从图中可以看出本设计的电路可以满足测量要求。

图4 SignalTap II数据采集图Fig.4 Diagram of data acquised by SignalTap II

3 结论

本文提出了一种对激光测距仪回波进行高速采样的方案,通过实际测量,证明该方案能够满足测量要求。FPGA+ DSP的构造为采用灵活的信号处理方法提供了便利。

[1]Charles L.Philips,等.信号、系统和变换[M].机械工业出版社,2006.

[2]TEXAS INSTRUMENTS.ADC08D500 Datasheet.

[3]TEXAS INSTRUMENTS.AD8138 Datasheet.

[4]ANALOG DEVICES.CDCM61001 Datasheet.

[5]阮琼,廖红华.高速电路板的信号完整性设计与仿真[J].湖北民族学院学报(自然科学版),2010.

[6]张健楠,鲍丹,刘婷婷.差分线对在高速PCB设计中的应用[J].新特器件应用,2011.

High Speed Acquisition and Processing Circuit for Digital Laser Range Finding

ZHOU Shao-Jie

(Huazhong Institute of Electro-optics,Wuhan National Laboratory for Optoelectronics,Wuhan Hubei 430223,China)

Against traditional echo acquisition in laser distance finding,a circuit to sample echo in high speed is introduced.In the cicuit,An ADC+FPGA+DSP mode is used..It has a flexible dissolution,which has a very slow value 0.3mv.The design is discussed in detail,a measurement of pulses with frequencies 5K Hz and pulse width 50ns shows that this circuit is practicable.

laser distance finding;high speed ADC

TP274

:Adoi:10.3969/j.issn.1002-6673.2014.03.050

1002-6673(2014)03-132-03

2014-03-09

周少杰,男,工程师。主要研究方向:数字电路设计与信号处理。